Verilog_HDL入门教程:硬件描述语言的基础

需积分: 9 148 浏览量

更新于2024-07-30

收藏 8.2MB PDF 举报

"本资源为Verilog_HDL的基础学习资料,适合初学者了解和掌握Verilog语言。内容包括Verilog HDL的简介及其在硬件描述语言中的地位,同时对比了另一种常见硬件描述语言VHDL。文件详细阐述了HDL的特点,如强大的描述能力、良好的可读性和可移植性,以及对设计生命周期的延长和支持大规模设计的分解和再利用。此外,还提及了HDL在保护知识产权方面的作用。"

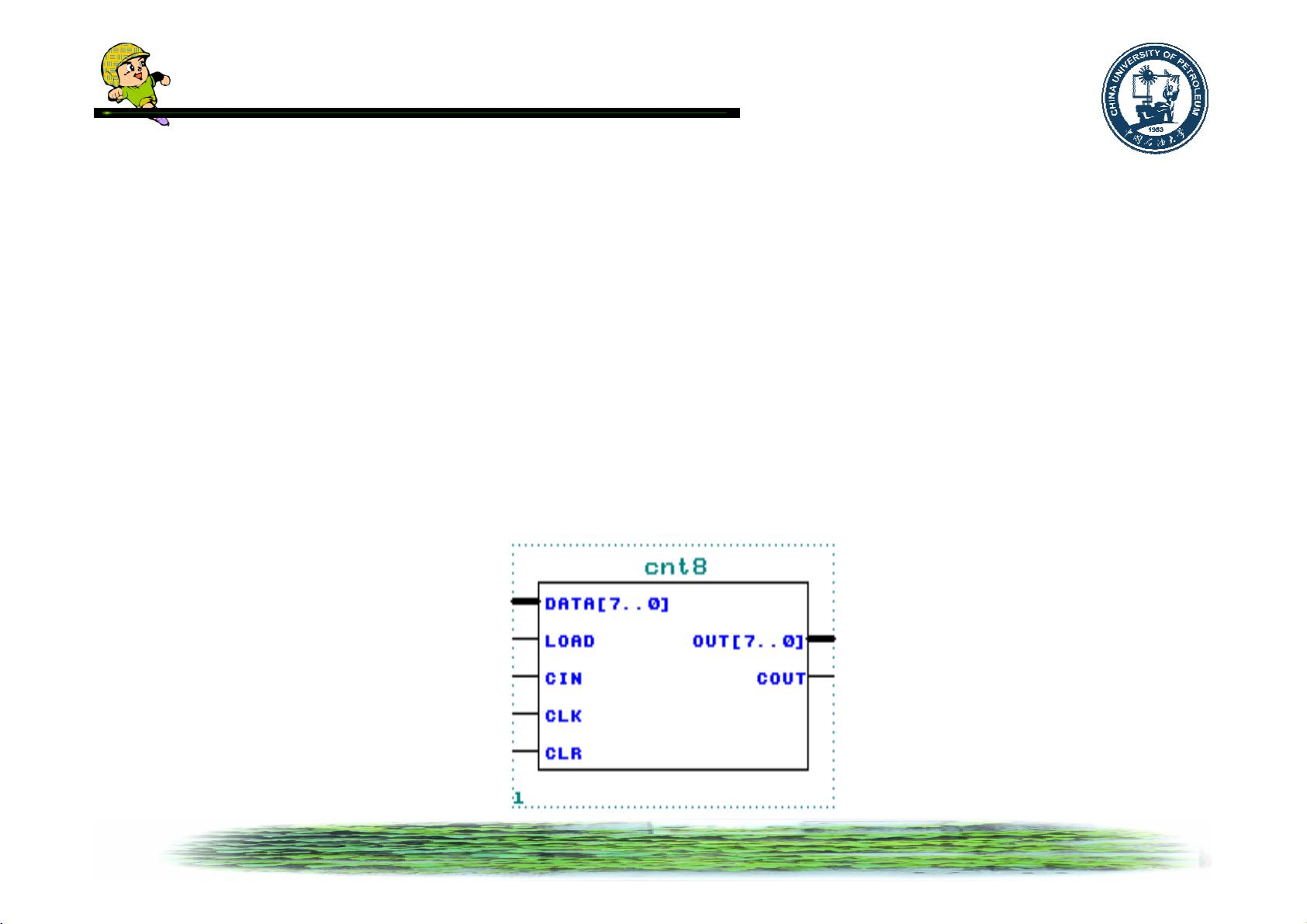

Verilog HDL是电子设计自动化(EDA)领域广泛使用的硬件描述语言之一,与VHDL一同成为IEEE的标准。它允许设计师以文本形式描述数字系统的结构和行为,涵盖了从门级到寄存器传输级,再到行为级的各种设计层次。Verilog HDL的语法简洁,易于理解和学习,适合初学者入门。

HDL的主要特点包括:

1. 强大的功能和广泛的覆盖面:Verilog HDL不仅可以描述基本的逻辑门电路,还能描述复杂的寄存器传输级电路,甚至可以处理基于行为算法的电路设计。

2. 良好的可读性:源代码既可被计算机解析执行,也便于人类阅读和理解,提高了设计交流的效率。

3. 高度的可移植性:作为IEEE标准,Verilog HDL可在不同的设计工具和平台上通用,确保了设计的跨平台一致性。

4. 延长设计生命周期:用Verilog HDL描述的设计与具体制造工艺解耦,工艺变化只需调整相关属性,而不需重构整个设计。

5. 支持大规模设计和团队协作:通过模块化设计,大型项目可以被拆分成多个小部分,由多个团队协同完成,便于设计复用。

6. 知识产权保护:使用Verilog HDL设计的ASIC,可以通过加密等手段保护设计不被轻易复制或窃取。

学习Verilog HDL对于电子工程师和芯片设计者来说至关重要,因为它提供了一种高效、灵活和标准化的方式来实现和验证数字系统设计,同时也为现代电子行业的创新和发展提供了坚实的技术基础。

点击了解资源详情

192 浏览量

点击了解资源详情

185 浏览量

118 浏览量

305 浏览量

189 浏览量

2022-09-22 上传

121 浏览量

fengling867

- 粉丝: 0

最新资源

- Cutterman: iOS代码审查与优化建议征集

- Eclipse工作空间配置文件分享与使用指南

- Linux内存分析器:检测内存泄漏与消耗

- 经典Java8 32位JDK下载 - JDK8最新版本发布

- WebOffice在线编辑器:快速处理Word和Excel文档

- Telerik Reporting 2014 Q3正式版发布,支持零序列号体验

- Delphi语言环境下的TsiLang组件范例分析

- 掌握SPI通信:C语言实现数据收发技巧

- 京东商城收货地址三级联动插件代码解析

- 通过RXTXcomm包实现Web端串口通信配置指南

- IEServer-master实现HTTP调用IE浏览器打开URL

- Chocolatey: React Native开发环境快速安装指南

- 两分钟内轻松将组织模式文件转化为炫酷HTML

- 绿色版VB图标制作工具v2.05:轻松制作与编辑ICO图标

- WoWoViewPagerAndroid:创新Android引导页面设计

- ResourceBundle Editor:提升本地化属性文件管理效率