布局验证基础:Calibre设计规则检查与 parasitic 提取

需积分: 16 25 浏览量

更新于2024-08-02

收藏 742KB PDF 举报

"这篇资料主要介绍了Calibre在布局验证中的基本应用,包括设计规则检查、布局与电路图对比以及寄生参数提取等关键步骤,并强调了布局验证的必要性。"

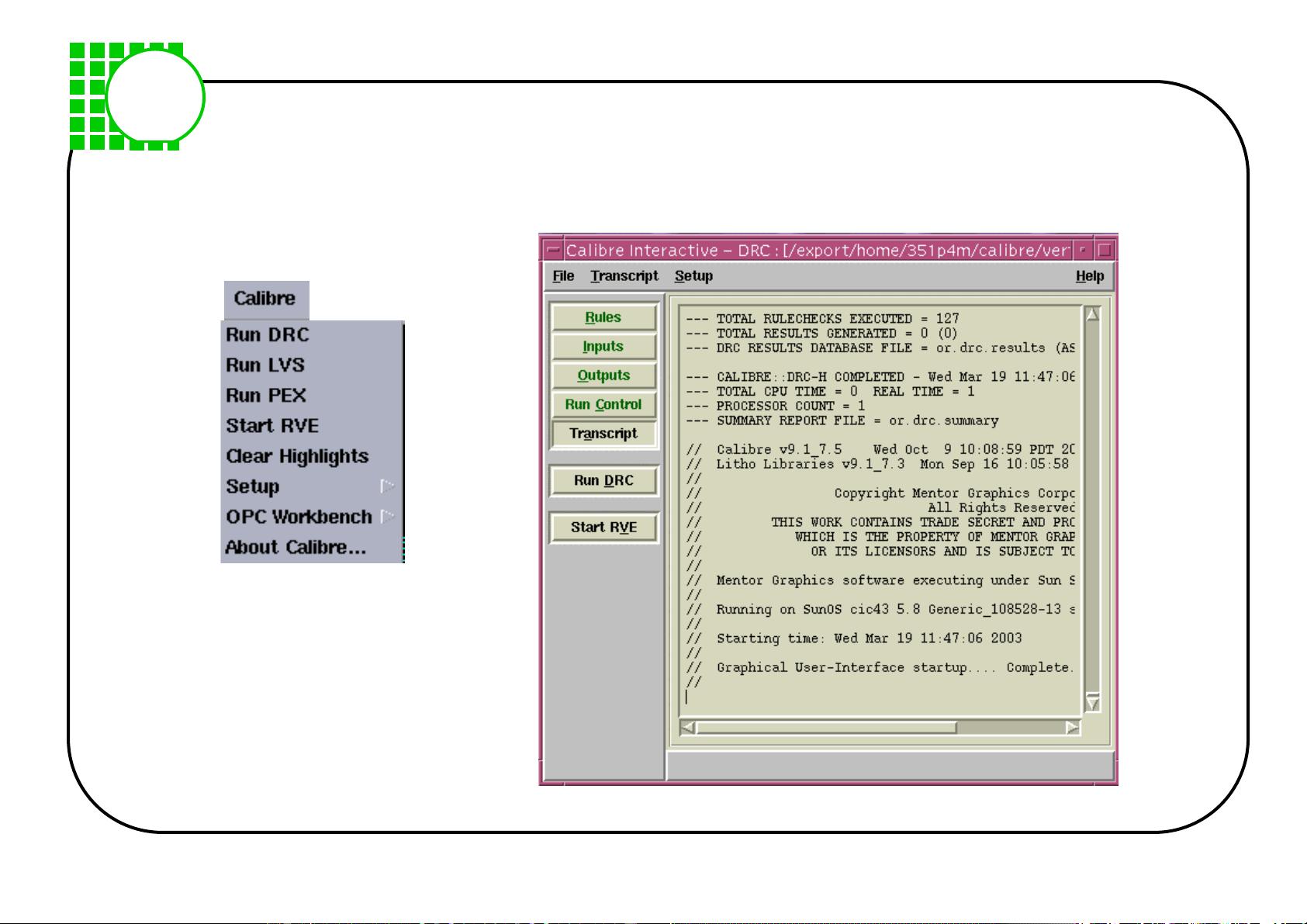

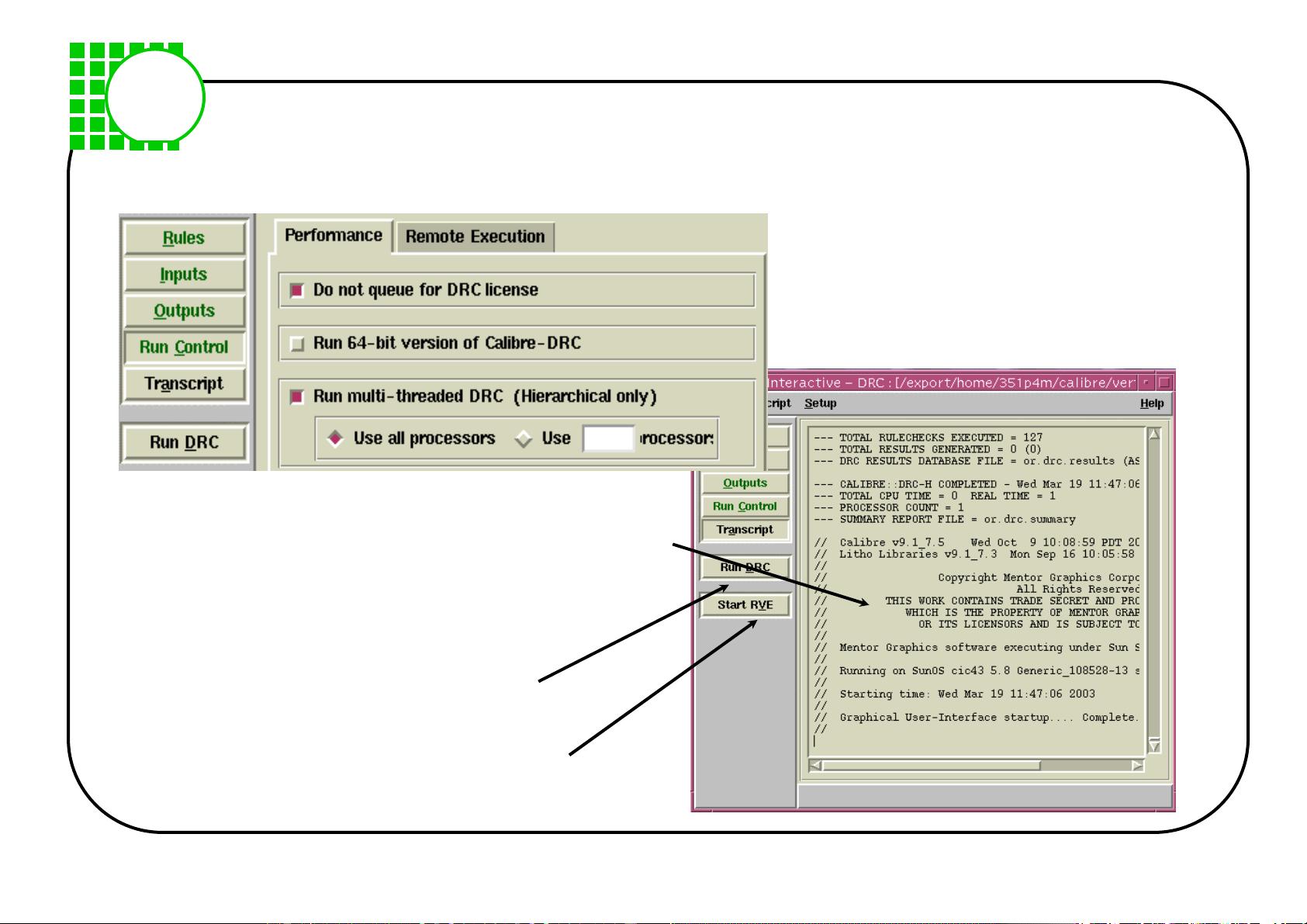

Calibre是 Mentor Graphics 公司推出的一款业界广泛使用的集成电路(IC)布局验证工具,它在半导体设计流程中扮演着至关重要的角色。布局验证是确保芯片物理设计满足制造工艺规则、保证可靠性和性能的关键步骤。

4-1 和 4-2 提到的CIC可能是指课程或者会议的代码,它们在介绍Calibre在布局验证中的应用。4-3至4-5进一步阐述了布局验证的必要性:

- 设计者通常只进行功能设计验证,但物理设计必须符合制造工艺规则,以确保可制造性和可靠性。

- 即使是商业化的布线工具也可能引入错误,因此需要布局验证来检查。

- 将布局数据库转换为代工厂接受的格式可能会引入新的错误。

- 布局完成后,设计的性能也需要经过验证。

4-6 描述了布局验证的基本概念:

- 布局验证是基于工艺流程的,需要一个数据库来存储工艺信息。

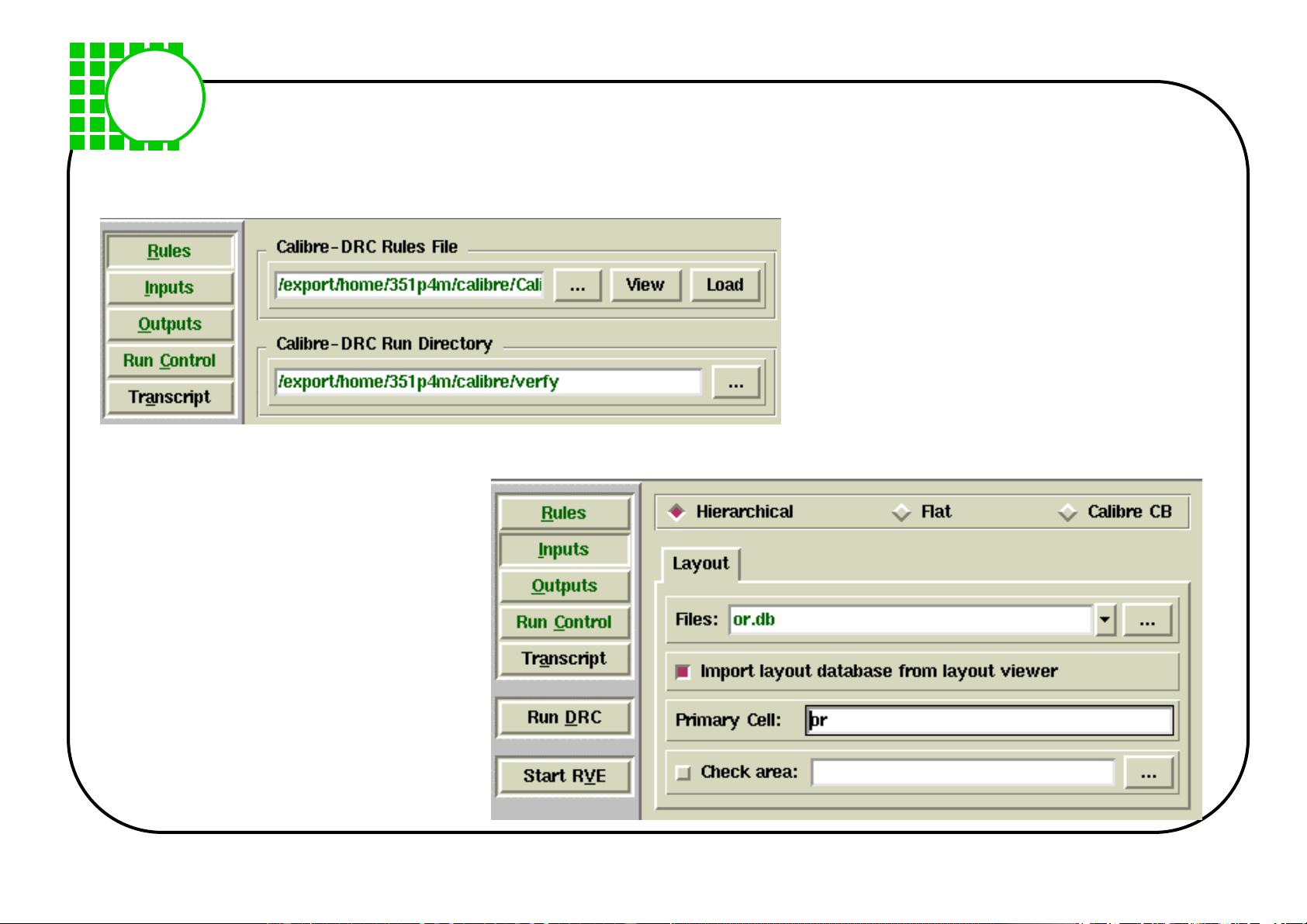

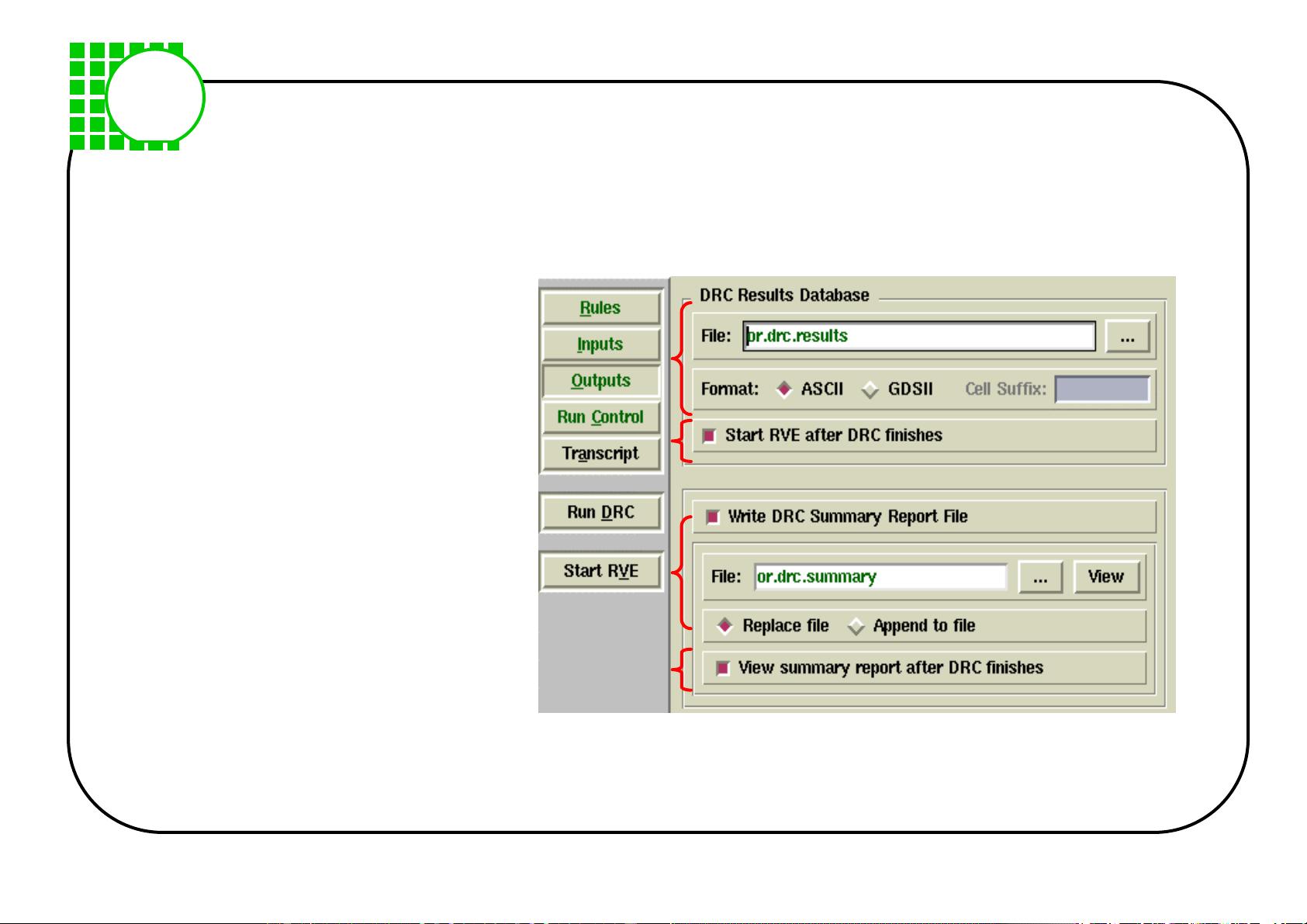

- 验证输入包括GDSII格式的布局数据库(有时也包含CIF或Cadence格式)、用于LVS(Layout versus Schematic)的网表信息以及工艺指定的信息。

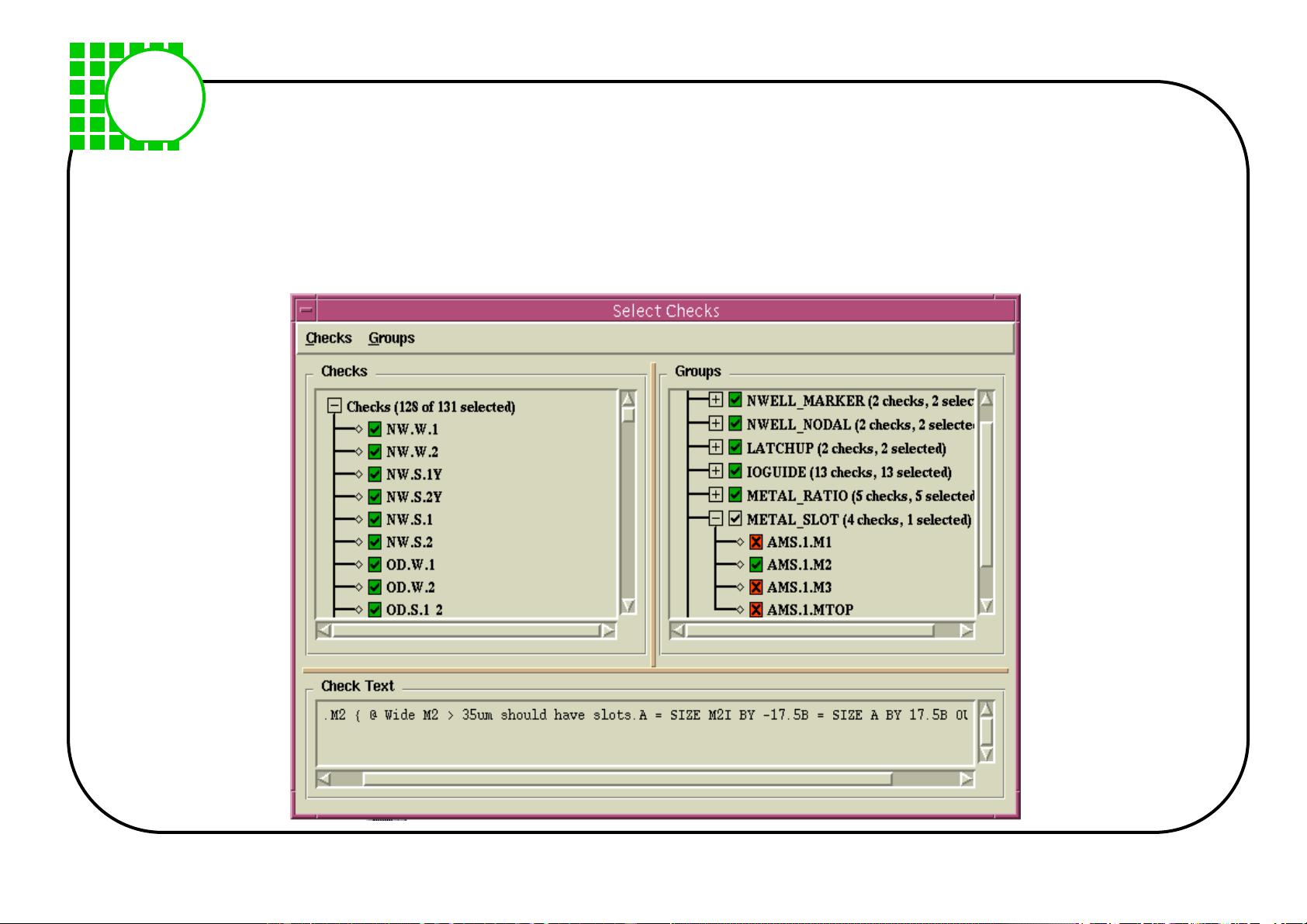

- 布局验证可以是增量式的,针对设计更改的部分进行检查,也可以是全芯片验证,覆盖整个设计。同时,验证可以采用层次化或扁平化的方式进行。

Calibre提供了以下核心功能:

1. **设计规则检查(DRC)**:DRC用于检查设计是否违反了特定工艺节点下的制造规则,如最小线宽、间距、接触区域等,确保设计能够在制造过程中成功实现。

2. **布局与电路图对比(LVS)**:LVS比较布局数据和电路原理图,验证两者的一致性,确保物理实现与逻辑设计匹配。

3. **寄生参数提取(Pex)**:XCalibre是Calibre的一个扩展,用于提取布局中的寄生电阻、电容和电感等参数,这些参数对电路模拟和性能预测至关重要。

4. **层次化处理**:对于大型设计,Calibre支持分层次的验证方法,能够提高验证效率并简化问题定位。

5. **增量验证**:仅对设计更改的部分进行验证,提高验证速度,适合频繁迭代的设计过程。

Calibre作为一款强大的布局验证工具,是保证IC设计质量和制造可行性的关键工具,通过DRC、LVS和Pex等步骤,确保设计在物理层面的完整性和性能。

2023-02-03 上传

2020-02-07 上传

2021-05-23 上传

2010-02-03 上传

2010-10-20 上传

2021-05-11 上传

150 浏览量

2021-02-03 上传

2021-05-18 上传

zouxinfeng953213

- 粉丝: 0

- 资源: 6

最新资源

- Angular程序高效加载与展示海量Excel数据技巧

- Argos客户端开发流程及Vue配置指南

- 基于源码的PHP Webshell审查工具介绍

- Mina任务部署Rpush教程与实践指南

- 密歇根大学主题新标签页壁纸与多功能扩展

- Golang编程入门:基础代码学习教程

- Aplysia吸引子分析MATLAB代码套件解读

- 程序性竞争问题解决实践指南

- lyra: Rust语言实现的特征提取POC功能

- Chrome扩展:NBA全明星新标签壁纸

- 探索通用Lisp用户空间文件系统clufs_0.7

- dheap: Haxe实现的高效D-ary堆算法

- 利用BladeRF实现简易VNA频率响应分析工具

- 深度解析Amazon SQS在C#中的应用实践

- 正义联盟计划管理系统:udemy-heroes-demo-09

- JavaScript语法jsonpointer替代实现介绍