高速电路设计:50MHz+信号挑战与仿真解决方案

4 浏览量

更新于2024-08-30

收藏 315KB PDF 举报

随着信息技术的飞速发展,电子系统设计进入了前所未有的高速时代。设计师们面临的挑战是,如何在100MHz乃至更高频率下确保电路的性能和可靠性。在现代系统中,高达80%的设计时钟频率超过50MHz,50%的设计主频超过120MHz,部分甚至达到500MHz以上,这就意味着传统的电路设计方法已无法满足高速信号传输的需求。

传输线效应和信号完整性问题成为关键的关注点。传输线效应是指信号在电路中的传播过程中,由于线路长度、特性阻抗匹配、不连续性和非线性等因素引起的信号失真和干扰。这些效应包括:

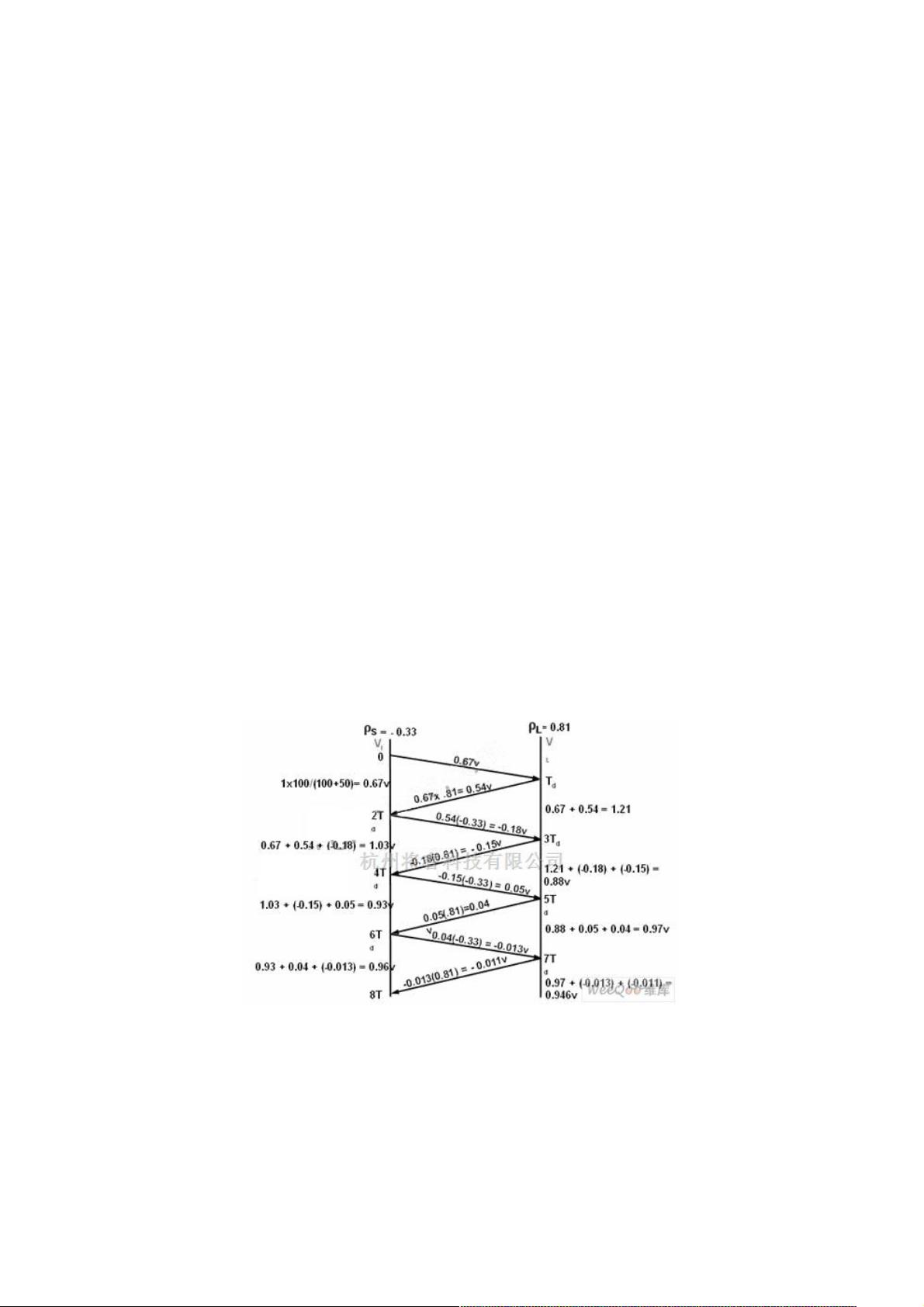

1. 反射信号:当信号在不匹配的终端遇到时,会反射回来,形成反射脉冲,可能导致信号失真,严重时可能引起时序错误和数据损坏。此外,反射信号还增加了噪声敏感性,易引发电磁干扰(EMI)。

2. 延迟和时序错误:高速信号的传播速度受到线路长度的影响,延迟可能导致信号到达接收端的时间与预期不符,进而破坏信号的时序关系,影响整个系统的正常工作。

3. 过冲和下冲:信号在传输过程中可能会超出其设计范围,即出现过冲(信号幅度超过最大允许值)或下冲(信号幅度低于最小允许值),这会导致信号失真和电路故障。

4. 串扰:相邻的信号线之间会相互影响,形成串扰噪声,干扰其他信号的传输,降低信号质量。

5. 电磁辐射:高速电路的电磁场可能会泄漏,对周围的电子设备造成干扰,影响系统的电磁兼容性(EMC)。

为了克服这些问题,电子系统设计师必须运用高速电路设计知识,进行信号质量仿真和先进的物理设计。高速电路仿真技术能够模拟信号在实际电路中的行为,帮助设计师评估和优化设计,确保信号完整性。这通常涉及到使用专业的电路仿真软件,如SPICE(Simulation Program with Integrated Circuit Emphasis)等,进行精确的波形分析和时域、频域分析。

总结来说,随着系统工作频率的提升,理解和解决高速电路传输线效应和信号完整性问题是电子系统设计的关键环节。设计师不仅需要熟悉高速电路原理,还要掌握现代设计工具和技术,以确保系统在高速环境下稳定运行,提高整体性能和可靠性。

2020-08-20 上传

2023-06-14 上传

2023-07-20 上传

2023-09-09 上传

2023-08-30 上传

2023-07-14 上传

2024-08-10 上传

2023-09-18 上传

2023-06-23 上传

weixin_38689223

- 粉丝: 7

- 资源: 909

最新资源

- ***+SQL三层架构体育赛事网站毕设源码

- 深入探索AzerothCore的WoTLK版本开发

- Jupyter中实现机器学习基础算法的教程

- 单变量LSTM时序预测Matlab程序及参数调优指南

- 俄G大神修改版inet下载管理器6.36.7功能详解

- 深入探索Scratch编程世界及其应用

- Aria2下载器1.37.0版本发布,支持aarch64架构

- 打造互动性洗车业务网站-HTML5源码深度解析

- 基于zxing的二维码扫描与生成树形结构示例

- 掌握TensorFlow实现CNN图像识别技术

- 苏黎世理工自主无人机系统开源项目解析

- Linux Elasticsearch 8.3.1 正式发布

- 高效销售采购库管统计软件全新发布

- 响应式网页设计:膳食营养指南HTML源码

- 心心相印婚礼主题响应式网页源码 - 构建专业前端体验

- 期末复习指南:数据结构关键操作详解