Altera FPGA的三速以太网MAC核用户指南

"Altera FPGA IP CORE 以太网 MAC 是Altera公司提供的一个核心功能,用于在FPGA(Field Programmable Gate Array)设计中实现以太网通信。这个IP核支持三速以太网(Triple Speed Ethernet MegaCore),涵盖了10/100/1000Mbps的速率,适用于各种网络接口的需求。该文档是软件版本9.0,发布于2009年3月,提供给用户关于如何使用和配置这一功能的指南。

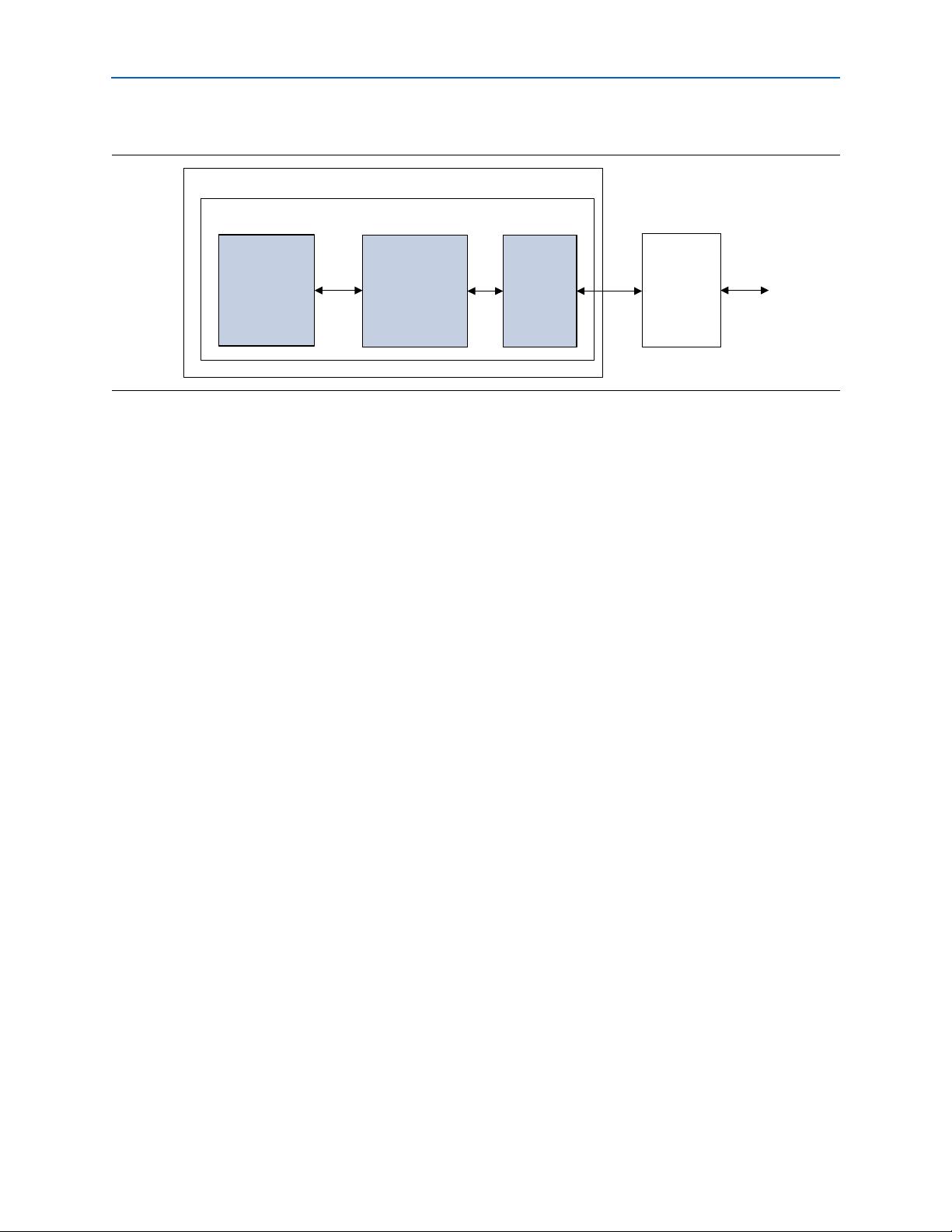

在Altera FPGA中集成以太网MAC(Media Access Controller)核心,可以实现FPGA与以太网网络的物理层和数据链路层的交互。MAC层是OSI模型中的第二层,负责控制设备之间的数据传输,包括冲突检测、帧的封装和解封装等。通过使用此IP核,设计者可以快速构建符合IEEE 802.3标准的以太网接口,无需从底层开始设计所有的硬件逻辑。

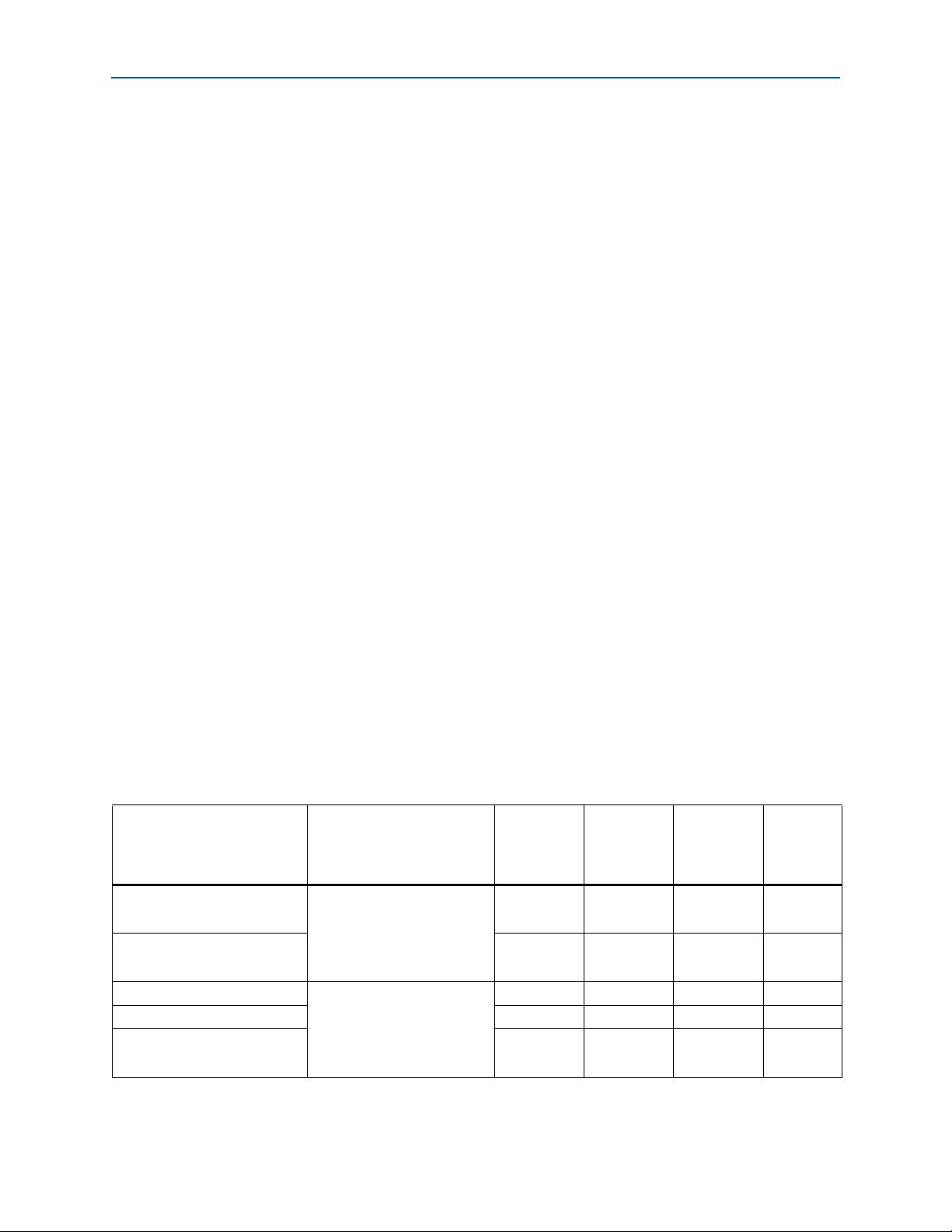

该IP核的功能可能包括但不限于以下几点:

1. 支持多种速率:10Mbps、100Mbps和1000Mbps,适应不同的网络环境。

2. 自动协商(Auto-Negotiation):允许设备自动协商最佳的工作模式和速率。

3. 冲突检测(Collision Detection):在半双工模式下,确保数据不会在传输过程中发生碰撞。

4. 流量控制(Flow Control):通过PAUSE帧机制提供全双工环境下的流量控制,避免数据溢出。

5. 错误检测和校验:如CRC(Cyclic Redundancy Check)校验,确保数据的完整性。

6. 硬件加速功能:例如,TCP/IP协议栈的部分处理可以通过FPGA硬件加速,提高系统性能。

使用Altera的开发工具,如Quartus II,设计者可以轻松地将该以太网MAC核集成到他们的FPGA设计中,并进行参数配置、时序分析和仿真验证。此外,文档通常会提供详细的例程和示例设计,帮助用户理解和应用IP核。

在实际应用中,Altera FPGA IP CORE 以太网MAC可以广泛用于各种领域,如工业自动化、网络设备、数据中心通信、嵌入式系统等,为系统设计提供了灵活、高性能的网络连接解决方案。然而,用户需要注意,虽然Altera保证其半导体产品的性能符合标准规格,但不对任何应用或使用这些信息、产品或服务产生的责任或损失负责,除非在书面协议中有明确约定。用户在使用前应仔细阅读文档,了解并遵循所有使用条件和限制。"

248 浏览量

点击了解资源详情

164 浏览量

1141 浏览量

266 浏览量

160 浏览量

169 浏览量

374 浏览量

点击了解资源详情