Verilog语言入门与FPGA应用详解

需积分: 23 124 浏览量

更新于2024-07-14

收藏 498KB PPTX 举报

Verilog语言快速入门教程深入解析

1. **电子设计自动化 (EDA)**: Verilog是电子设计自动化工具中的一个重要组成部分,它是一种硬件描述语言(HDL),用于描述和实现数字电路的功能。EDA技术利用计算机软件来替代传统手工设计,通过可编程逻辑器件(PLDs)如单片集成500门以下的简单PLD、复杂PLD、 PROM、PAL、GAL、 CPLD,以及更高级的FPGA进行设计。FPGA尤其因其灵活性和广泛应用,被广泛用于高速处理系统、数字集成芯片前端设计、嵌入式系统(SOPC,System-on-a-Chip)和通用逻辑设计等领域。

2. **硬件描述语言 (HDL)**: VHDL和Verilog是两种主要的HDL。Verilog以其简洁的语法和易上手的特点,虽然语法更为严格,但在调试过程中更加便捷。Verilog的设计流程包括设计电路的逻辑功能部分,通过assign语句定义输入和输出之间的逻辑关系,always语句处理时序逻辑,以及调用底层模块的功能描述。

3. **Verilog模块结构**:

- 模块是Verilog设计的基本单元,由module关键字开始,endmodule结束。模块结构通常包含输入(input)、输出(output)、内部信号声明以及可能的参数声明。

- 三种核心语句:assign用于描述组合逻辑,always用于处理时序逻辑,调用其他模块的语句用于模块间的交互。

- 模块结构中,功能描述部分和模块说明部分是可选的,但module名和endmodule是必需的。

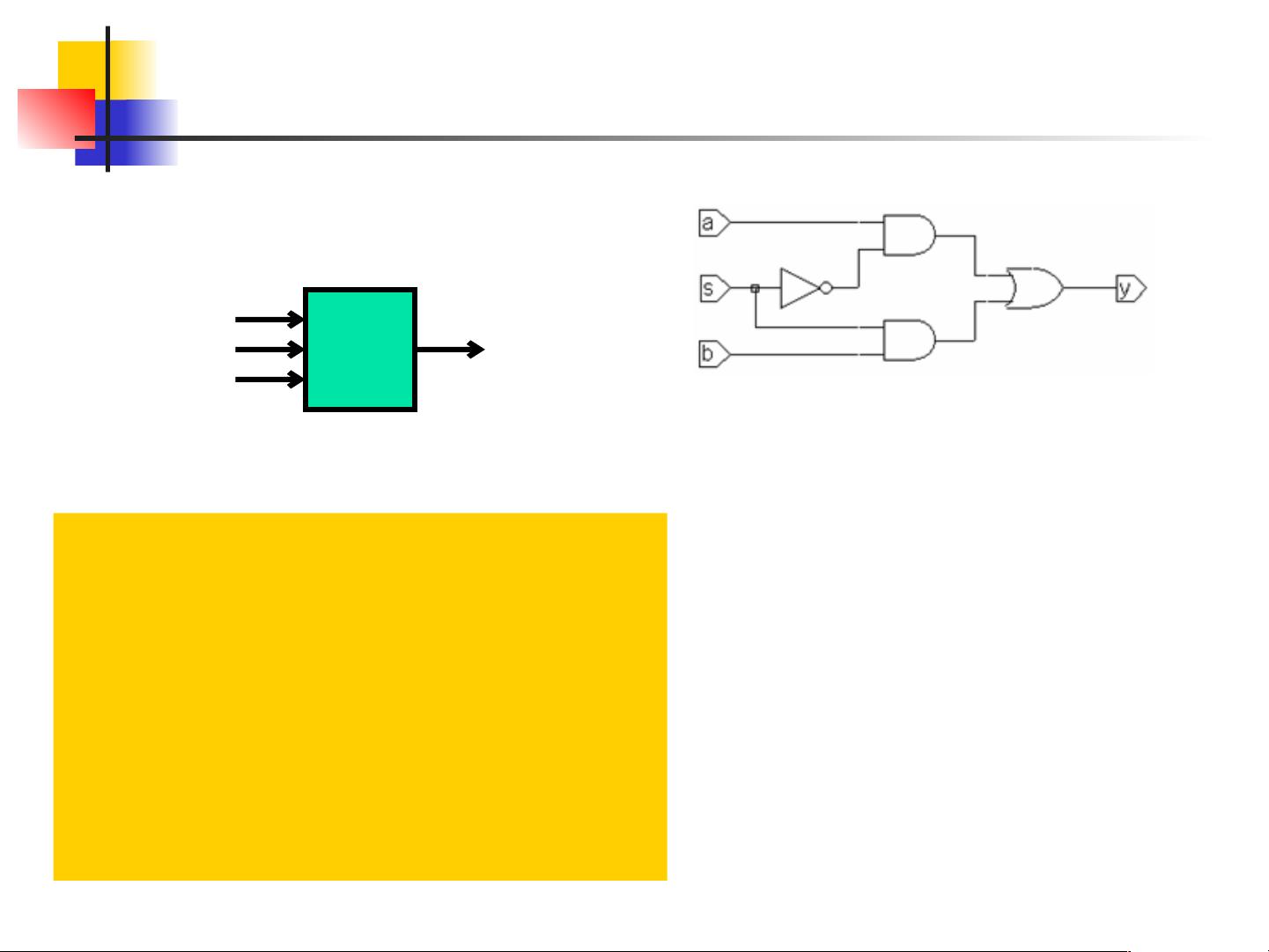

4. **实例演示**: 例如,MUX21模块就是一个二选一数据选择器,其代码展示了如何使用Verilog编写模块,包括输入变量a、b、s,输出变量y,以及用assign语句定义选择逻辑。模块名(MUX21)后面跟随着端口列表和具体的逻辑实现。

Verilog语言作为硬件描述语言在现代电子设计中扮演着关键角色,它提供了灵活且高效的电路设计手段。通过理解模块结构和基本语句,设计师能够构建并测试复杂的数字电路,适应不断发展的电子技术需求。无论是初学者还是经验丰富的工程师,掌握Verilog都是电子工程领域的重要技能。

126 浏览量

2023-07-26 上传

2021-10-07 上传

168 浏览量

2022-01-22 上传

2021-10-07 上传

2021-10-07 上传

朵儿

- 粉丝: 0

- 资源: 7

最新资源

- 2009年java最新面试题

- Graphical Models, Exponential Families, and Variational Inference

- 计算机外文 计算机专业

- C# 如何判断一个Byte数组中是否存在某些连续的数据).txt

- unix常用命令有助于日常工作的小贴士

- C# 的类型转换.doc

- 华为笔试面试指南有兴趣的可以好好看

- service 天气预报

- 城市生活垃圾逆向物流网络优化设计

- C#编码规范,共享参考

- Ext 的中文手册PDF

- A Multiresolution Image Segmentation Technique Based on Pyramidal Segmentation and Fuzzy Clustering

- 图书管理系统SQL数据库

- C#完全手册.pdf

- 工作流原理及实例说明

- java从基础到应用编程经验