3DES加密算法升级与FPGA在安全应用中的设计优化

48 浏览量

更新于2024-08-30

1

收藏 254KB PDF 举报

3DES加密算法及其FPGA设计

随着网络的迅速发展,信息安全问题日益突出,加密技术作为保障信息安全的核心手段,扮演着至关重要的角色。传统的加密方法主要依赖于主机上的软件,这种方式存在诸多局限性。首先,软件加密占用大量主机资源,运算速度相对较慢;其次,密钥管理不善,如明文存储或加密存储在文件中,容易导致关键数据在内存或磁盘中的安全风险,比如个人密码PIN等。

相比之下,硬件加密采用独立于主机系统的专用硬件设备,如FPGA(Field-Programmable Gate Array,现场可编程门阵列),将加密过程硬件化。这种设计的优势在于:不消耗主机资源,加密和解密操作速度更快,且能提供更高的安全性。硬件加密确保关键数据在整个生命周期中都是在加密状态下处理,避免了密钥暴露带来的安全隐患。

3DES(Triple Data Encryption Standard)算法正是针对DES的安全性问题而提出的改进。DES原本的56位密钥长度被提升至112位或168位,大大增强了抵抗攻击的能力。虽然DES曾被认为不够安全,但在IPSEC等新一代互联网安全协议中,DES仍被纳入考虑范围,这表明即使面临更新的安全需求,DES算法的某些特性依然有价值。

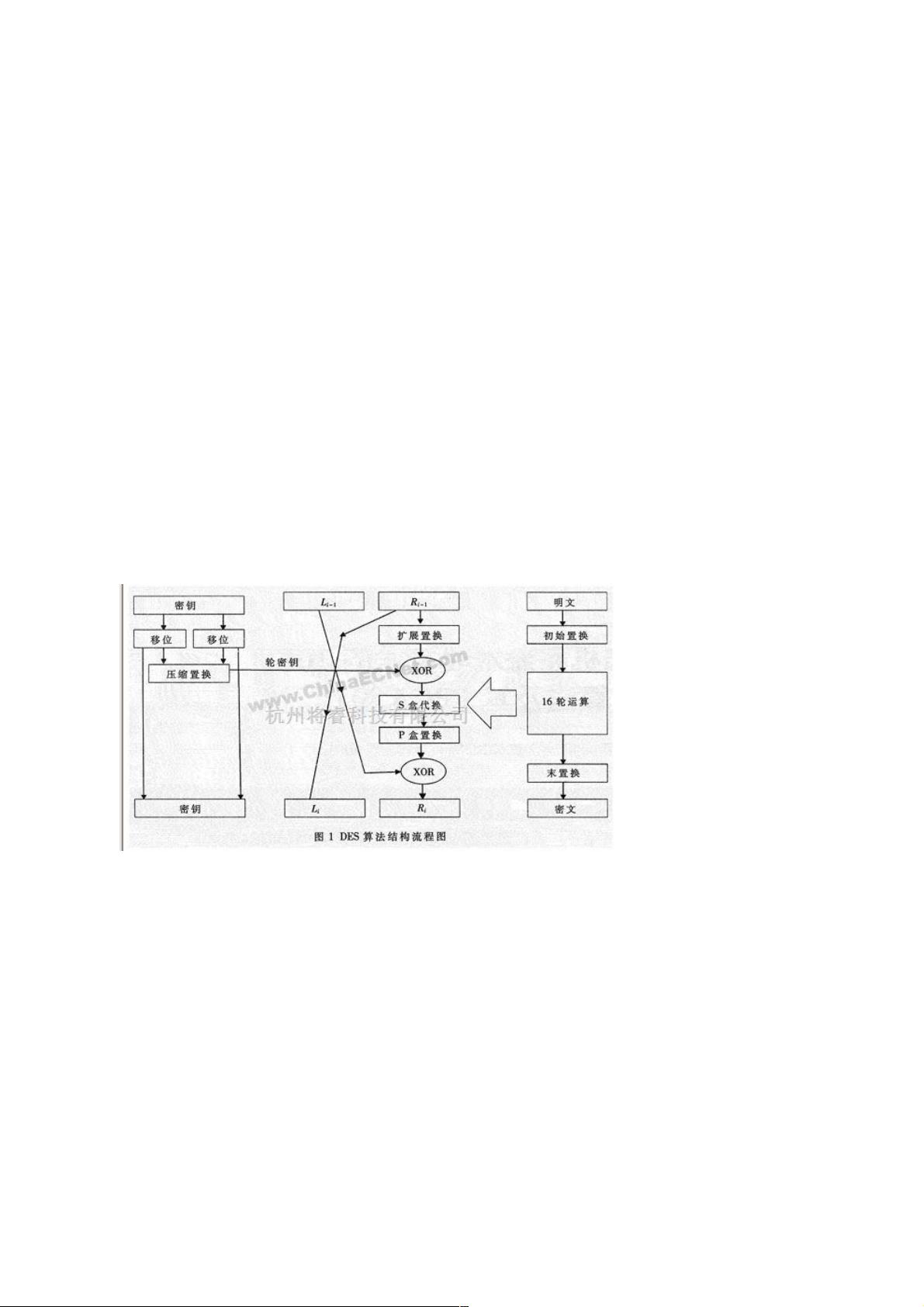

3DES是对DES的三倍应用,通过对每个DES块进行三次加密,进一步增强数据保护。其加密过程包括:初始置换、16轮相同的运算(涉及扩展置换、S盒代换、P盒置换和异或运算)、末置换,最终生成64位密文。这种加密算法在卫星通信、网关服务器、机顶盒、视频传输等场景广泛应用,允许现有系统在不大幅改动的情况下实现升级。

尽管DES的局限性使得3DES成为更为理想的选择,但FPGA的设计与实现并非易事。它涉及到复杂的电路设计、算法优化和硬件加速,以确保在实时性和效率之间找到平衡。FPGA可以灵活地根据特定应用调整加密引擎的性能,从而提供定制化的加密解决方案。在实际的FPGA设计中,需要考虑功耗、面积和性能等因素,同时还要进行严格的测试以确保算法的正确性和安全性。

3DES加密算法因其更高的安全性而在现代信息系统中占据重要地位,而其在FPGA上的实现则是实现高效、安全硬件加密的关键技术之一,对于保障网络通信和个人数据的安全具有深远的意义。随着技术的进步,如何在硬件平台上优化3DES算法并适应不断变化的威胁环境,将是未来研究和实践的重点。

2022-07-14 上传

2020-07-29 上传

2020-12-13 上传

点击了解资源详情

2022-07-14 上传

2020-07-22 上传

weixin_38632825

- 粉丝: 3

- 资源: 947

最新资源

- 高清艺术文字图标资源,PNG和ICO格式免费下载

- mui框架HTML5应用界面组件使用示例教程

- Vue.js开发利器:chrome-vue-devtools插件解析

- 掌握ElectronBrowserJS:打造跨平台电子应用

- 前端导师教程:构建与部署社交证明页面

- Java多线程与线程安全在断点续传中的实现

- 免Root一键卸载安卓预装应用教程

- 易语言实现高级表格滚动条完美控制技巧

- 超声波测距尺的源码实现

- 数据可视化与交互:构建易用的数据界面

- 实现Discourse外聘回复自动标记的简易插件

- 链表的头插法与尾插法实现及长度计算

- Playwright与Typescript及Mocha集成:自动化UI测试实践指南

- 128x128像素线性工具图标下载集合

- 易语言安装包程序增强版:智能导入与重复库过滤

- 利用AJAX与Spotify API在Google地图中探索世界音乐排行榜