FPGA硬件实现8位除法运算

93 浏览量

更新于2024-09-02

收藏 91KB PDF 举报

"FPGA实现除法运算的原理与步骤"

在数字电路设计中,特别是在FPGA(Field-Programmable Gate Array)这样的可编程逻辑器件中,实现除法运算是一项复杂的任务,与我们在软件编程中使用的简洁除法操作符"/"截然不同。FPGA的除法实现主要依赖于硬逻辑门电路,需要通过精心设计的算法来完成。本文将详细介绍FPGA如何实现除法运算,并提供一个具体的8位除法器的实例。

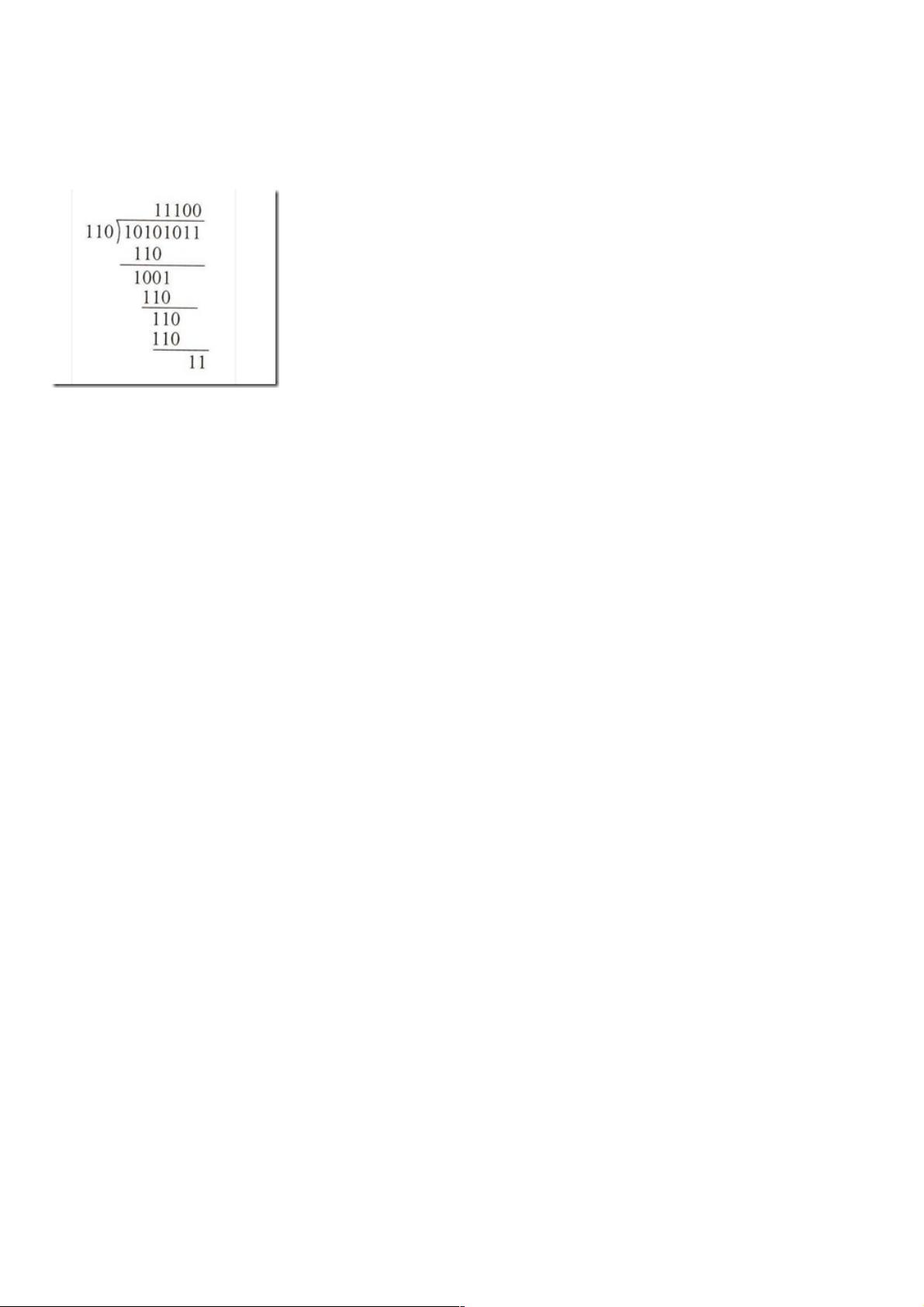

首先,理解二进制除法的基本原理至关重要。二进制除法与十进制除法的逻辑基本相同,都采用了辗转相除法,即通过不断的试除和调整来得到商和余数。在二进制中,从最高位开始逐位比较,如果被除数的当前位大于或等于除数,则商为1,否则为0。然后更新被除数,直至所有位都被处理。

在FPGA实现中,以8位无符号数为例,我们将被除数扩展为16位,高8位为0,低8位为原始的被除数值。除数则保持8位。运算过程通常涉及一个开始信号,当开始信号触发时,将16位数据初始化为被除数的值。接下来,通过一系列的比较、移位和减法操作来计算商和余数。

具体步骤如下:

1. 比较:将被除数的16位扩展数据与除数进行比较。如果被除数的高8位大于或等于除数,商的相应位置为1,否则为0。

2. 赋值与减法:如果商为1,将被除数减去除数,并更新商的低位。

3. 左移:将被除数的数据左移一位,进入下一位的比较。

4. 循环:重复上述步骤,直到进行了8次左移,即处理了所有的8位。

5. 结果:最后,被除数的高8位为余数,低8位为商。

例如,对于输入的被除数78(二进制:01001110)和除数34(二进制:00100010),经过8次左移和比较后的结果如下:

- 初始:00000000_01001110(被除数)

- 第一次:00000000_10011100(商0,余数不变)

- 第二次:00000001_00111000(商0)

- 第三次:00000010_01110000(商0)

- 第四次:00000100_11100000(商0)

- 第五次:00001001_11000000(商0)

- 第六次:00010011_10000000(商0)

- 第七次:00100111_00000000(商1,余数)

这个例子展示了整个除法过程,最终得到的余数是00100111(十进制23),商是00000100(十进制4)。这种实现方法虽然较为直观,但在实际应用中可能需要优化以提高速度和资源效率,例如使用更高效的除法算法或流水线设计。

FPGA实现除法运算涉及到数字逻辑设计、位操作和循环控制等概念,是数字系统设计中的一个重要组成部分。理解并掌握这些原理和方法对于FPGA开发者来说是至关重要的。

2037 浏览量

325 浏览量

2021-11-18 上传

423 浏览量

182 浏览量

weixin_38690407

- 粉丝: 1

最新资源

- 微信小程序开发教程源码解析

- Step7 v5.4仿真软件:s7-300最新版本特性和下载

- OC与HTML页面间交互实现案例解析

- 泛微OA官方WSDL开发文档及调用实例解析

- 实现C#控制佳能相机USB拍照及存储解决方案

- codecourse.com视频下载器使用说明

- Axis2-1.6.2框架使用指南及下载资源

- CISCO路由器数据可视化监控:SNMP消息的应用与解析

- 白河子成绩查询系统2.0升级版发布

- Flutter克隆Linktree:打造Web应用实例教程

- STM32F103基础之MS5单片机系统应用详解

- 跨平台分布式Minecraft服务端:dotnet-MineCase开发解析

- FileZilla FTP服务器搭建与使用指南

- VB洗浴中心管理系统SQL版功能介绍与源码分析

- Java环境下的meu-grupo-social-api虚拟机配置

- 绿色免安装虚拟IE6浏览器兼容Win7/Win8