UVM入门指南:学习SystemVerilog与验证环境

"Getting Started with UVM" 是一个关于UVM(Universal Verification Methodology)的入门教程,由Verilab Publishing出版。本教程可能涵盖了UVM的基础概念、组件使用以及验证环境的构建等内容。

UVM(Universal Verification Methodology)是基于SystemVerilog语言的一种标准化的验证方法论,它为集成电路(IC)设计的验证提供了可复用、可扩展的框架。在IC设计领域,UVM被广泛用于验证芯片功能的正确性,通过创建验证组件、类库和预定义的机制,简化了复杂的验证流程。

这个教程可能由JL Gray作为项目管理者,Vanessa R. Cooper作为设计师,以及Georgellen Burnett作为编辑共同完成。Verilab是一家专注于验证环境开发、方法论定义和项目规划的公司,他们在全球有多个办公室,并且在SystemVerilog(包括UVM、OVM、VMM等)方面有着丰富的经验和专业技术支持。

在UVM的学习中,你可能会接触到以下几个关键知识点:

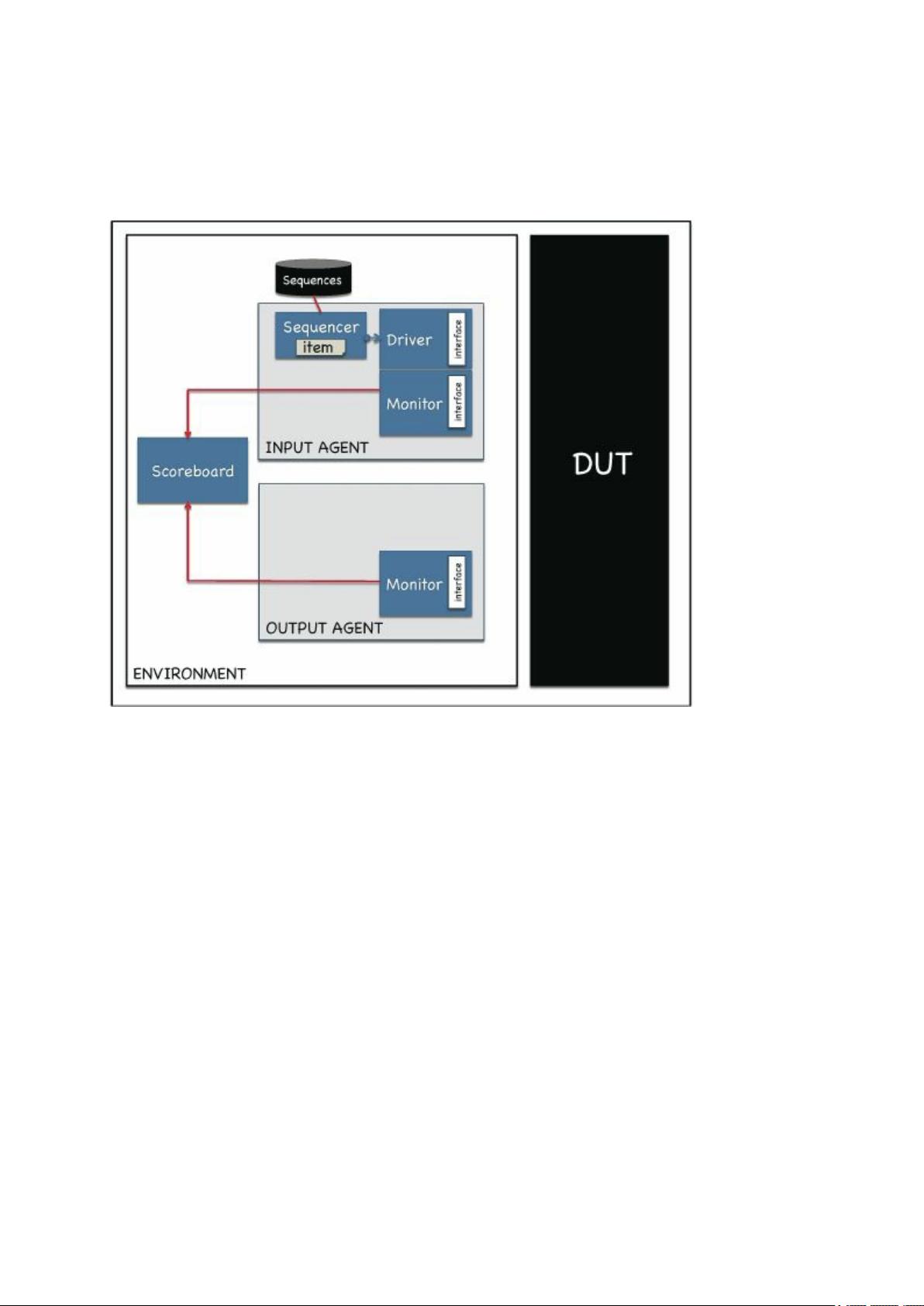

1. **基础概念**:理解UVM的核心概念,如Agent(代理)、Environment(环境)、Sequence(序列)、Transaction(事务)等,以及它们在验证中的作用。

2. **类库结构**:了解UVM类库的组织结构,包括Base Class、Configurations、Sequences、Monitors、Drivers、Scoreboards等,以及如何根据需求定制和扩展这些类。

3. **组件交互**:学习如何通过UVM通信机制(如put/get接口、connectivity、callbacks等)来实现组件间的交互。

4. **配置与复用**:掌握如何使用UVM配置机制来控制组件的行为和连接,以及如何通过工厂(Factory)机制实现动态对象创建和类型映射。

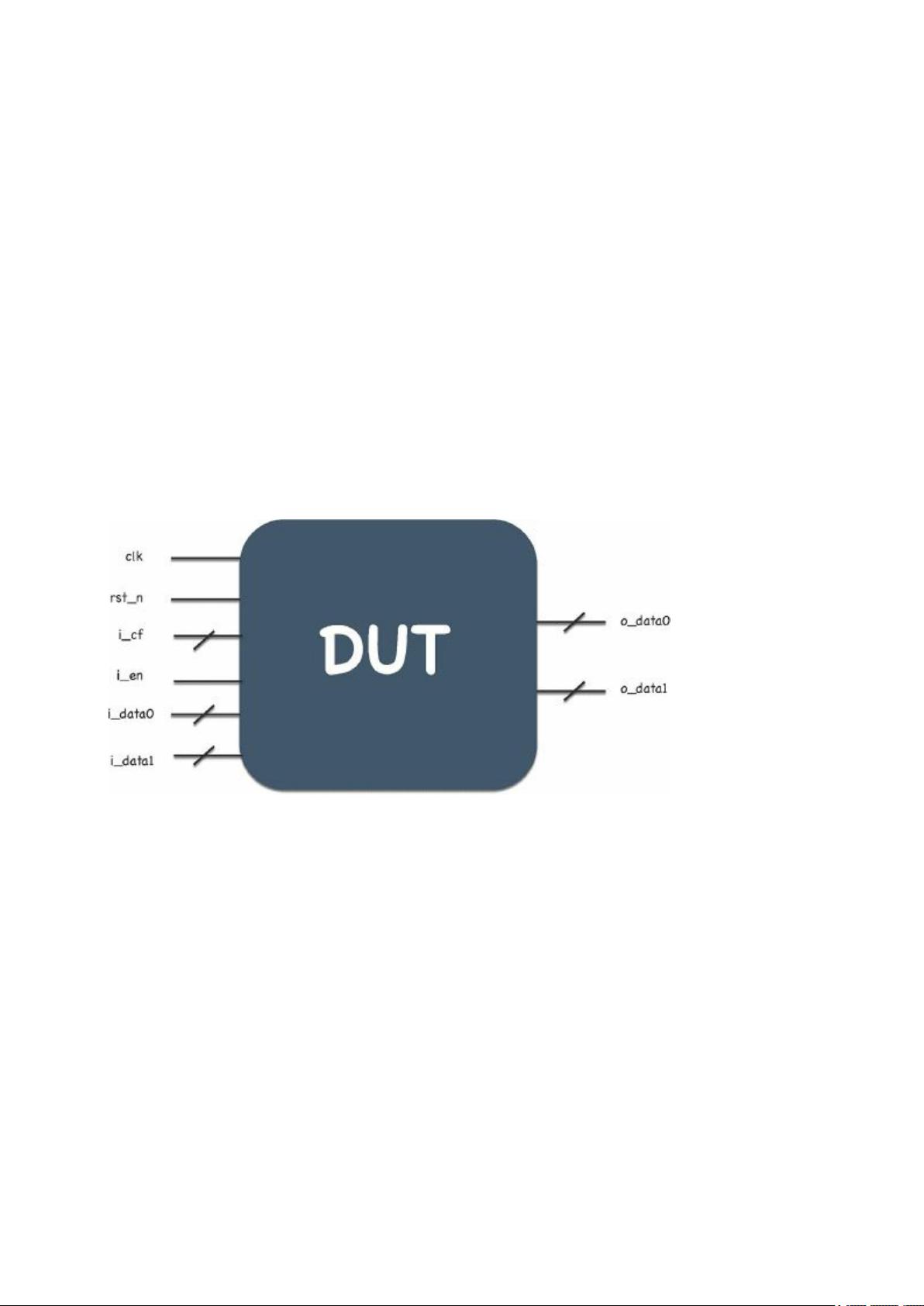

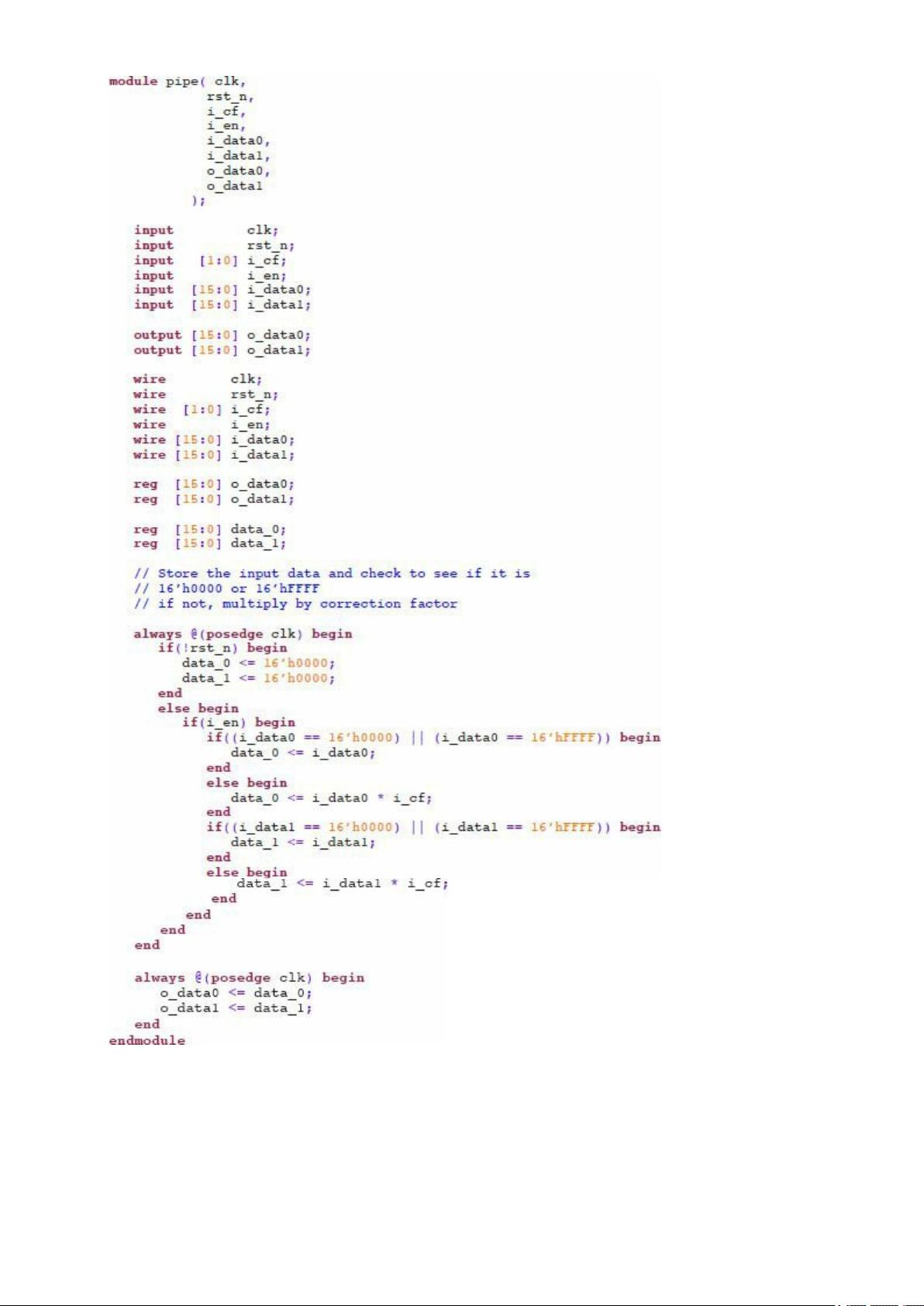

5. **验证环境搭建**:学习如何构建一个完整的UVM验证环境,包括测试平台(Testbench)的构造,激励生成器(Sequencer)的设计,以及响应处理(Driver)和结果比较(Scoreboard)的实现。

6. **高级特性**:深入理解如覆盖(Coverage)、调试(Debugging)、报告(Reporting)等高级功能,以及如何利用它们来提高验证的效率和完整性。

7. **实战应用**:通过实例学习如何将理论知识应用于实际项目,解决具体验证问题,如协议一致性检查、性能评估等。

8. **持续集成和自动化**:了解如何将UVM验证环境与版本控制工具、自动化构建系统(如Makefile或连续集成工具)相结合,以实现验证过程的自动化。

9. **最佳实践**:学习业界验证的最佳实践,如模块化设计、重用策略、验证计划制定等,以提升验证的效率和质量。

10. **标准更新与兼容**:由于Verilab参与了IEEE-1800(SystemVerilog)委员会和VIP-TSC(UVM),教程可能会涵盖最新的UVM标准和技术趋势。

通过这个入门教程,读者将能够逐步掌握UVM的基本概念和使用技巧,为进行高效、可靠的集成电路验证打下坚实的基础。

415 浏览量

756 浏览量

109 浏览量

109 浏览量

466 浏览量

138 浏览量

336 浏览量

455 浏览量

132 浏览量

Unicom6

- 粉丝: 0

最新资源

- C++课程作业全集:深入掌握编程技能

- Unity游戏开发必备——LitJson插件使用指南

- 绿色版图标提取器:快速提取EXE/DLL图标

- Android搜索器实现-简约炫酷的SearchableSpinner

- 飞思智能车用两路IR2104S驱动电路设计与测试

- Android图表绘制简易教程与hellochart应用

- HWP2007viewer:便捷的韩国文档编辑软件查看器

- 创新设计:防丢失笔帽的笔具技术方案

- 老朽痴拙汉化版FrontEnd Plus 2.03:JAVA反编译利器

- 网络压缩项目:探索高效信息编码新方法

- Combuilder:Joomla组件开发的命令行神器

- 易语言实现多参数线程启动技巧分享

- Hishop网店助理v1.6.2:本地管理与平台互通神器

- MonoGame案例解析:构建单人游戏的C#之旅

- 网上商城系统实现:JSP+Servlet+JavaBean源码

- TCPView3.05:网络连接状态监控利器