FPGA实现的CPM信号解调器设计与VHDL应用

153 浏览量

更新于2024-09-01

收藏 387KB PDF 举报

"本文介绍了在EDA/PLD领域中,如何基于FPGA设计部分响应CPM(连续相位调制)信号的解调器。文章详细阐述了CPM的基本原理,特别是二进制部分响应L=2的调制方式,并提出了相应的FPGA实现方案,采用VHDL作为硬件描述语言进行设计。

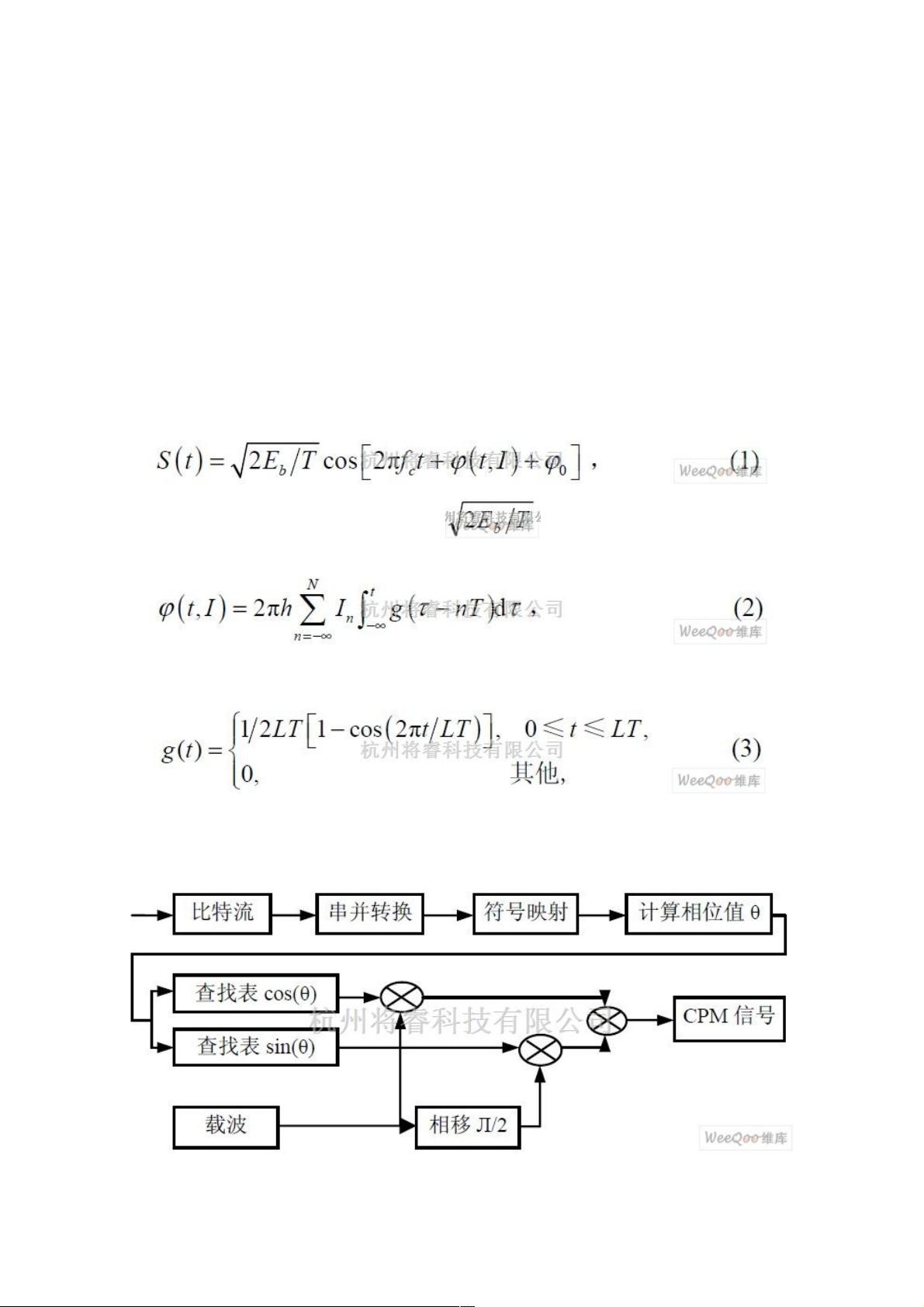

1. CPM(连续相位调制)的基本原理

CPM信号是一种具有恒包络特性的调制方式,其相位轨迹随信息连续变化,从而实现高带宽效率。公式(1)给出了CPM信号的数学表示,其中bE代表码元能量,T为码元间隔,cf为载波频率,φ(t,I)为包含信息的相位函数。调制指数h和成形脉冲函数g(t)(通常选择升余弦脉冲RC)共同决定了信号的特征。对于二进制调制,信息序列nI取值为+1或-1。

2. CPM信号的生成

通过计算基带相位,然后根据相位生成I/Q两路信号,两路信号相加形成调制后的CPM信号。这一过程如图1所示,展示了从基带相位到调制信号的转换。

3. CPM解调器的实现原理

解调过程通常包括解调、最大似然序列估计、Viterbi译码和判决等步骤。首先,接收的复包络信号被分为I/Q两路,经过下变频处理成为基带信号。随后,这些基带信号与参考正交信号(cos(ψ(t,a))和sin(ψ(t,a)))进行相关运算,用于提取信息。

4. FPGA设计方法

文章提出了一种基于FPGA的解调器设计方案,利用VHDL语言进行硬件描述,这使得设计能够高效地在FPGA上实现。FPGA的灵活性和并行处理能力使其成为高速数据处理的理想平台,特别是在通信系统中实现复杂算法时。

5. 部分响应L=2的特性

部分响应L=2是一种优化带宽效率的方法,通过设计适当的脉冲形状,可以减少信号间的干扰,提高解调的精度。在FPGA中实现这种解调器,可以有效地处理部分响应L=2的CPM信号,实现高效的数据恢复。

6. VHDL在设计中的应用

VHDL作为一种硬件描述语言,允许工程师以结构化的方式描述数字系统的逻辑,使得FPGA的设计和验证更加直观和高效。在本文的解调器设计中,VHDL被用来定义逻辑门级的电路,实现解调算法的硬件化。

该文提供了CPM信号解调器的FPGA实现,不仅揭示了CPM调制解调的基本理论,还展示了如何在实际工程中运用EDA/PLD技术,对于提升通信系统的性能和效率具有重要的指导价值。"

点击了解资源详情

点击了解资源详情

点击了解资源详情

2020-11-09 上传

2020-11-09 上传

2020-11-10 上传

2020-12-06 上传

2020-11-07 上传

2020-11-09 上传

weixin_38590989

- 粉丝: 8

- 资源: 940

最新资源

- Angular程序高效加载与展示海量Excel数据技巧

- Argos客户端开发流程及Vue配置指南

- 基于源码的PHP Webshell审查工具介绍

- Mina任务部署Rpush教程与实践指南

- 密歇根大学主题新标签页壁纸与多功能扩展

- Golang编程入门:基础代码学习教程

- Aplysia吸引子分析MATLAB代码套件解读

- 程序性竞争问题解决实践指南

- lyra: Rust语言实现的特征提取POC功能

- Chrome扩展:NBA全明星新标签壁纸

- 探索通用Lisp用户空间文件系统clufs_0.7

- dheap: Haxe实现的高效D-ary堆算法

- 利用BladeRF实现简易VNA频率响应分析工具

- 深度解析Amazon SQS在C#中的应用实践

- 正义联盟计划管理系统:udemy-heroes-demo-09

- JavaScript语法jsonpointer替代实现介绍