FPGA与MPC875实现多路接口到E1协议转换

88 浏览量

更新于2024-08-29

1

收藏 237KB PDF 举报

"多路接口与E1协议转换器设计与实现"

本文介绍了一种创新的解决方案,用于解决低速设备无法直接接入高速E1通信线路的问题。设计中采用了可编程逻辑器件FPGA(Field Programmable Gate Array)和嵌入式微处理器MPC875,构建一个多路接口与E1协议转换器。该转换器能够将多个低速接口如RS 232、RS 449、V.35的数据转换并整合到E1线路的高速传输中。

0 引言部分强调了随着信息技术和通信技术的进步,对于高带宽的需求日益增长,E1作为2.048Mb/s的传输标准,在DDN(Digital Data Network)和帧中继网络中的应用越来越广泛。多路接口与E1协议的转换器旨在使多种设备能够利用E1线路进行高效通信。

1 系统原理

1.1 系统描述

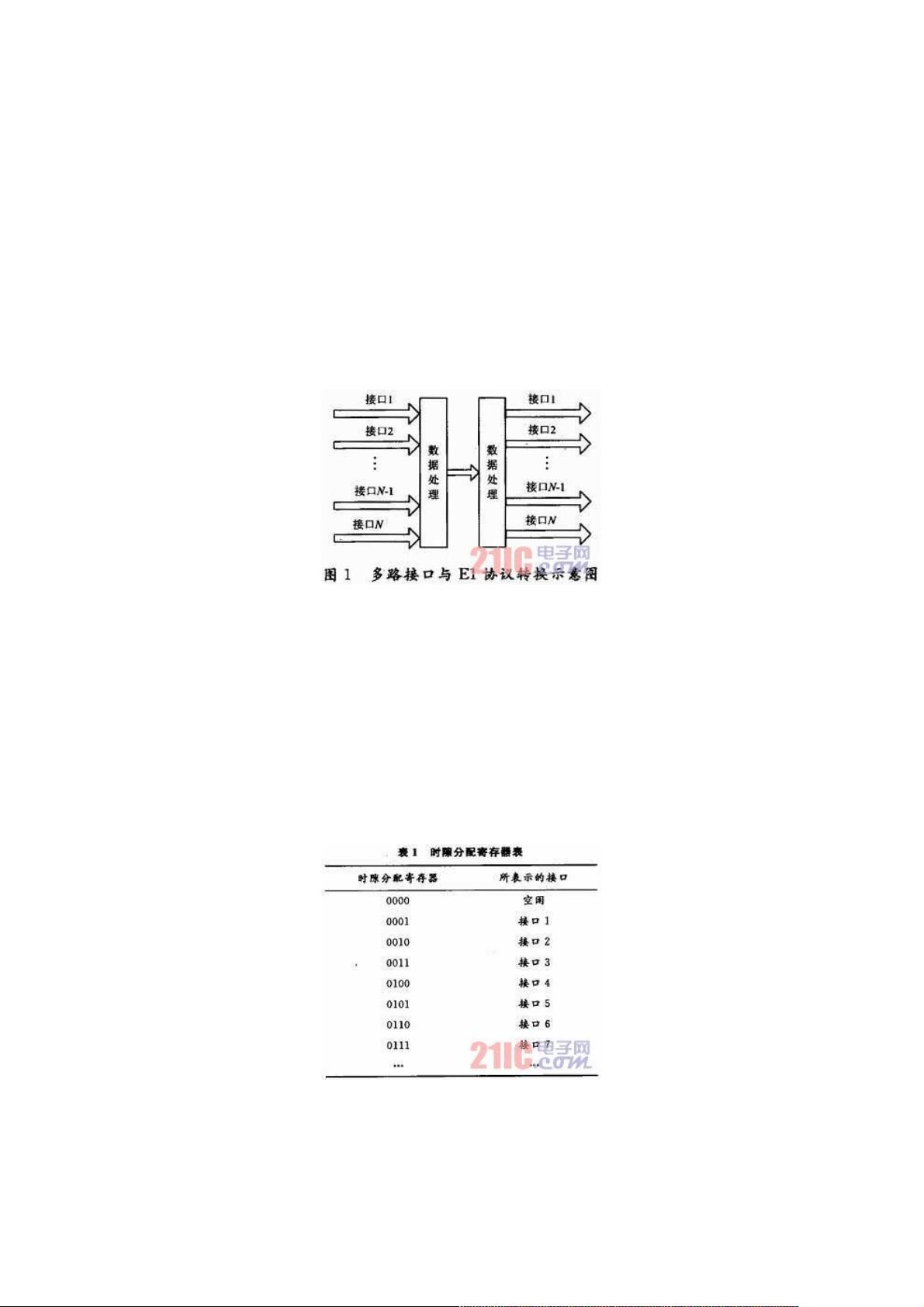

转换器的工作原理如图1所示,它在发送端将来自多路接口的数据按照特定顺序组合成一个符合E1协议的数据流,然后通过E1信道传输。在接收端,这个E1信号被拆分还原成原始的多路接口数据。

1.2 数据映射到E1帧的方法

E1帧结构包含32个时隙,其中CH0用于帧同步,CH16用于信令,剩余时隙用于数据传输。为了实现多路接口数据与E1的转换,不同接口的数据被分配到不同的时隙中。接口速率决定了时隙的分配,确保分配给每个接口的时隙速率至少等于接口本身的速率。用户需要通过软件界面预先设定这些分配。

为实现这一功能,设计了30个4位的时隙分配寄存器。CPU依据用户的设置,生成对应的数据时隙地址,从而控制数据在E1帧中的位置。这种静态分配方式要求用户根据接口速率手动配置,转换器本身不具备接口速率的自适应功能。

在实际应用中,这种转换器可以有效提高E1线路的利用率,使得低速设备能够无缝接入高速网络,提升通信效率。通过RS 232、RS 449和V.35接口的转换测试,证明了该设计方案的可行性与实用性。这样的设计不仅适用于现有的通信系统升级,也为未来可能出现的类似问题提供了参考解决方案。

2025-03-25 上传

2025-03-25 上传

2025-03-25 上传

2025-03-25 上传

weixin_38667697

- 粉丝: 10

最新资源

- 掌握随机森林回归器:sklearn预测模型实践

- STM32F407官方评估板资源下载:原理图与PCB文件

- OpenGL实现屏幕拆分与图形旋转技术

- Seay源代码审计系统2.0发布:增强SQL监控与在线升级功能

- 深入解析VC Button源码重写技术与实践

- 探索jQuery图片局部缩放放大镜插件使用

- Java EE 5实用教程:WebLogic与Eclipse集成开发

- 拍拍贷“魔镜风控系统”:信用评分与逾期预测算法设计

- C#到VB.NET代码转换工具实现方法

- 深入了解OpenXML SDK:微软Office 2007文件格式背后的秘密

- 掌握凯撒密码:加密解密工具的使用与原理

- 实现jQuery锚链接的平滑滚动效果

- JD-GUI:一款强大的Java jar包反编译GUI工具

- 嵌入式SQL在数据库访问中的应用实验报告

- Python+Selenium实现账号自动化登录测试

- C#实现阿拉伯数字到中文金额的转换