理解数字逻辑:一位半加器与全加器的工作原理

需积分: 0 124 浏览量

更新于2024-08-04

收藏 110KB DOCX 举报

"本文主要介绍了数字逻辑中的基本加法电路,包括一位半加器和一位全加器的设计、工作原理及仿真结果。"

在数字电路设计中,加法操作是基础计算之一,通常通过组合逻辑电路实现。半加器和全加器是构成多位加法器的基础单元。

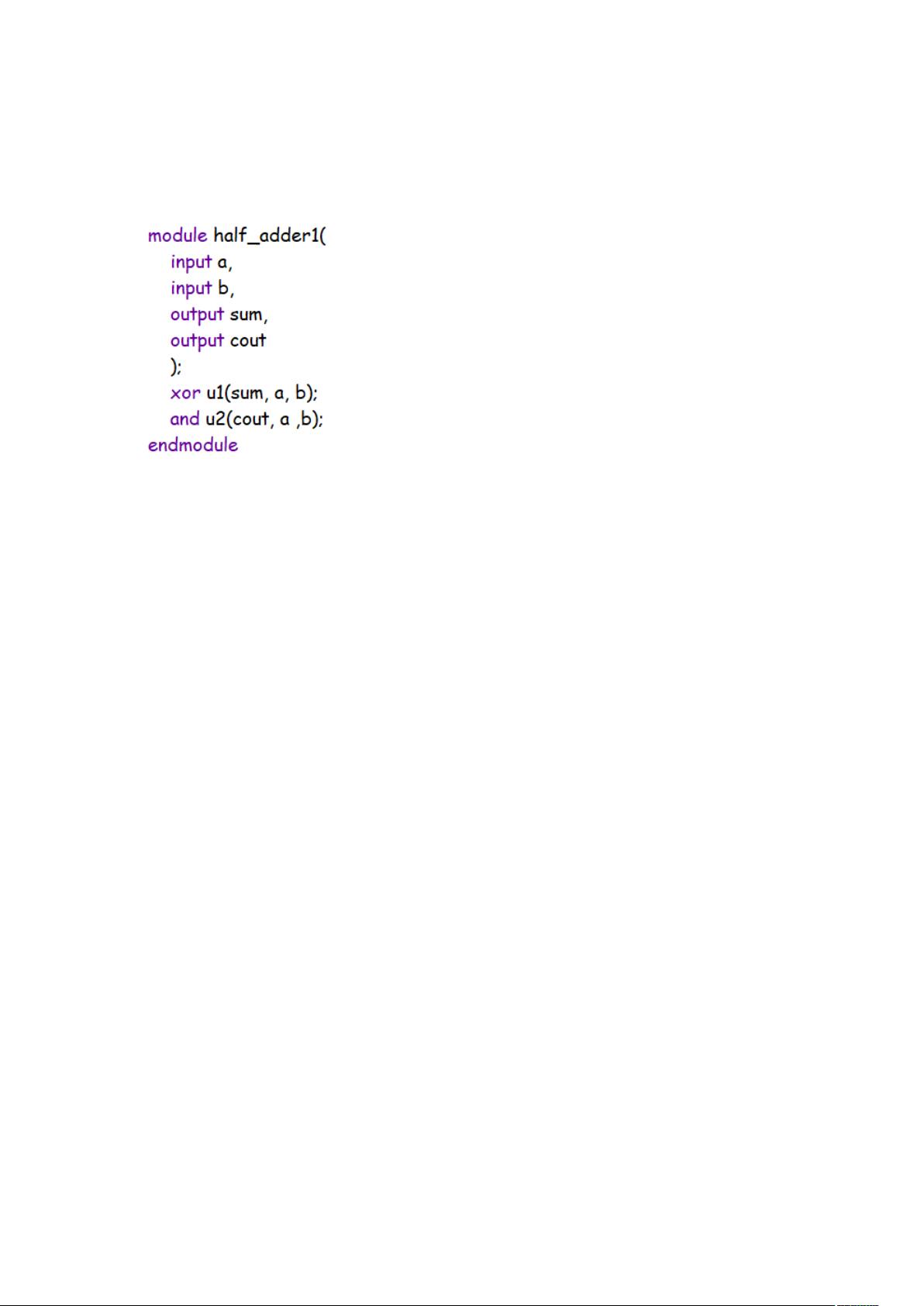

一位半加器(Half Adder)用于计算两个二进制位的和,不考虑前一位的进位。半加器有两个输入端(a和b)和两个输出端(sum和cout)。在行为描述中,半加器的和(sum)是输入a和b的异或(XOR)结果,即`Sum=a^b`,表示不同时为1时输出为1;进位输出(cout)是输入a和b的与(AND)结果,即`Cout=a&b`,表示同时为1时有进位。数据流描述则直接用布尔代数表达式实现这一逻辑功能,通过`assign`语句分配给相应的输出。在Verilog代码中,我们可以通过`always`块结合`case`语句或者直接使用逻辑运算符实现这些逻辑功能。

一位全加器(Full Adder)除了接收两个输入位(a和b)外,还有一个进位输入(cin),并产生一个和(sum)和一个进位输出(cout)。全加器可以处理三位二进制数的加法:a、b和cin。在结构描述中,全加器通过几个基本逻辑门(XOR和AND)连接来实现,如使用XOR门计算和,AND门处理进位条件,最后通过OR门决定最终的进位输出。在行为描述中,`always`块内的`case`语句根据所有输入的组合来定义输出sum和cout。全加器的输出sum是a、b和cin的异或结果,cout则是多个与门和或门的结果,考虑了所有可能的输入情况。

仿真结果通常用于验证设计的正确性,通过输入不同的二进制组合,检查半加器和全加器的输出是否符合预期的加法运算规则。

一位半加器和一位全加器是数字逻辑设计的基础,它们为构建更复杂的多位加法器和算术逻辑单元(ALU)奠定了基础。理解其工作原理和设计方法对于深入学习数字电子学至关重要。

458 浏览量

165 浏览量

点击了解资源详情

165 浏览量

1020 浏览量

2886 浏览量

523 浏览量

2023-06-06 上传

lowsapkj

- 粉丝: 1015

- 资源: 312

最新资源

- CI--EA实施

- 24L01模块原理图+PCB两种天线三块板子

- Horiseon-proyect

- SimbirSoft

- 钟摆模型:用于不同实验的 Simulink 模型-matlab开发

- shopcart.me

- 6ES7214-1AG40-0XB0_V04.04.00.zip

- hivexmlserde jar包与配套数据.rar

- KeepLayout:使自动布局更易于编码

- worldAtlas

- AdvancedPython2BA-Labo1

- lsqmultinonlin:共享参数的全局参数非线性回归-matlab开发

- STK3311-WV Preliminary Datasheet v0.9.rar

- js实现二级菜单.zip

- 微店助理 千鱼微店助理 v1.0

- tao-of-rust-codes:作者的回购