"DDR3 DFI 3.1标准详解:信号、时序、功能全面解读"

需积分: 12 68 浏览量

更新于2024-03-25

1

收藏 1.42MB PDF 举报

The DDR-PHY Interface Specification v3.1 is a document that outlines the DDR3 DFI 3.1 standard. It provides detailed information on the signal names, timing, and functions of DFI 3.1, making it easier to understand the connection between DDR3/4 controllers and PHY. The document, which was released on May 19, 2012, by Cadence Design Systems, Inc., is a valuable resource for engineers and designers working with DDR memory technology.

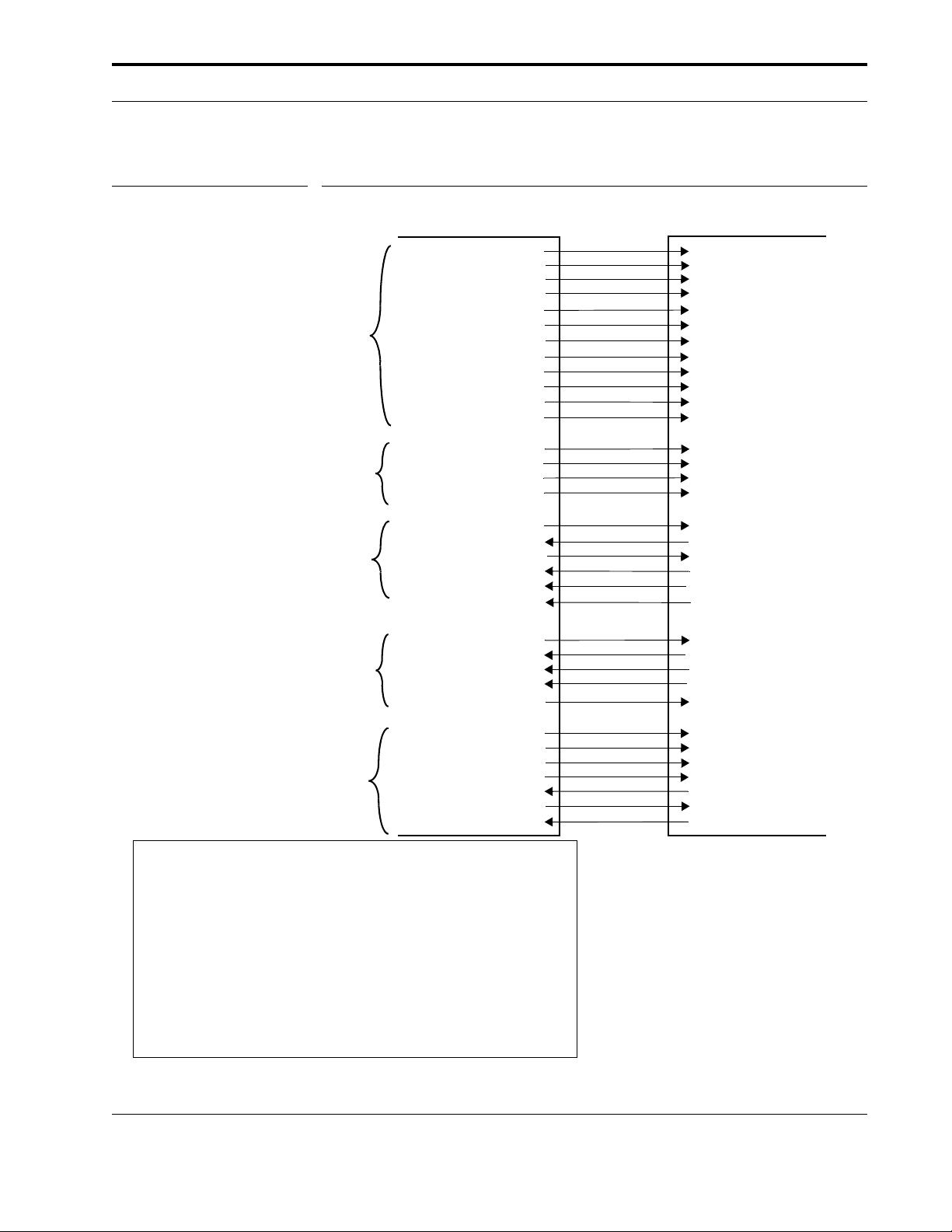

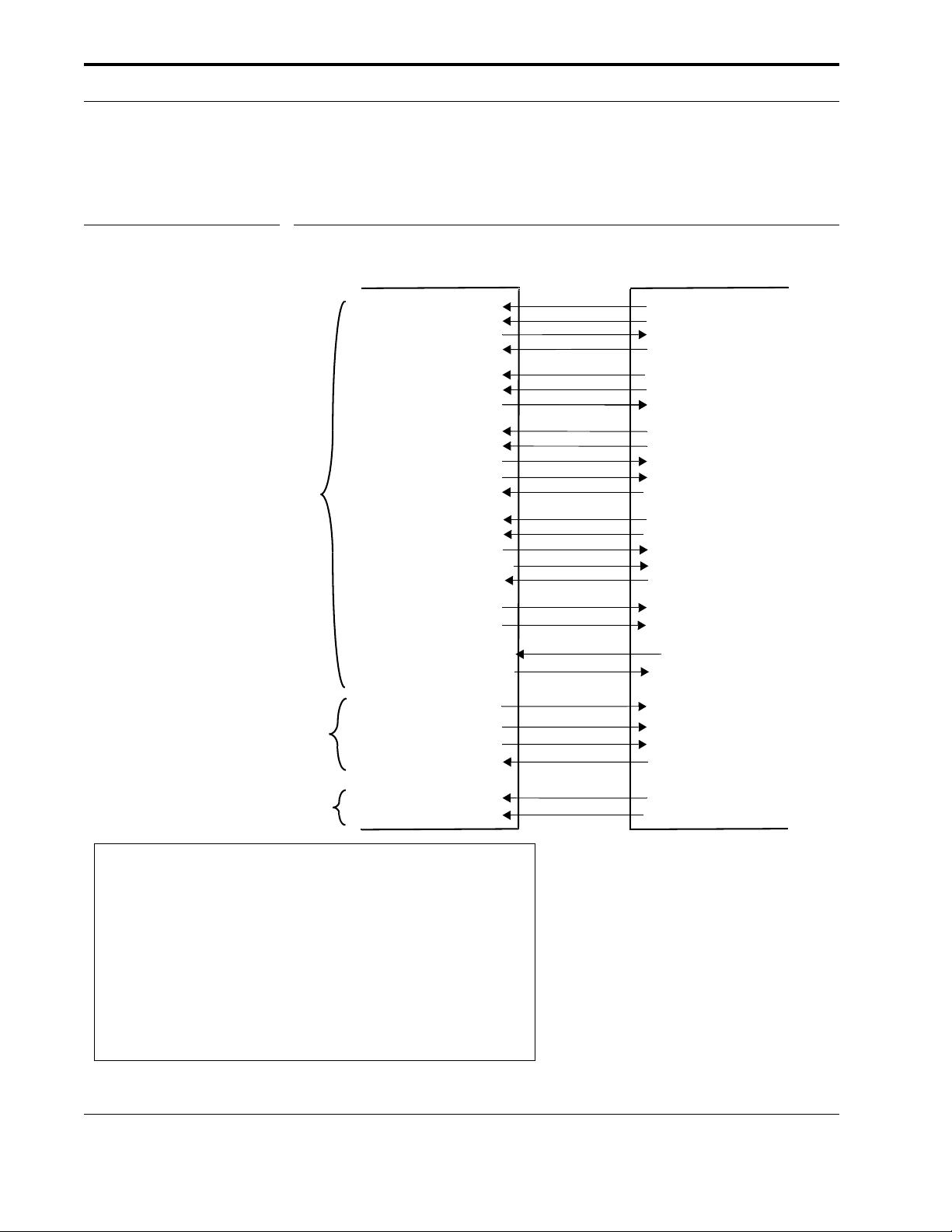

The specification details the various signal names used in DFI 3.1, such as DFI_CONTROL, DFI_DATA, and DFI_ADDRESS. It also explains the timing requirements for these signals, including the clock period, the setup and hold times, and the reset sequence. By following these specifications, designers can ensure a reliable and efficient connection between their DDR controllers and PHY.

In addition to signal names and timing parameters, the document also covers the functions of DFI 3.1. This includes the role of each signal in the data transfer process, such as data strobes, read and write commands, and power management signals. Understanding these functions is essential for optimizing the performance of DDR memory systems and ensuring compatibility between different components.

Overall, the DDR-PHY Interface Specification v3.1 is a comprehensive guide to the DFI 3.1 standard. It provides essential information on signal names, timing requirements, and functions, helping engineers and designers to create stable and efficient DDR memory systems. Whether you are designing a new DDR3/4 controller or troubleshooting an existing system, this document is an invaluable resource for achieving optimal performance and reliability.

2019-07-18 上传

2017-02-24 上传

2023-07-04 上传

2021-07-17 上传

2018-11-14 上传

2022-04-08 上传

点击了解资源详情

2024-11-14 上传

succy

- 粉丝: 2

- 资源: 7

最新资源

- 高清艺术文字图标资源,PNG和ICO格式免费下载

- mui框架HTML5应用界面组件使用示例教程

- Vue.js开发利器:chrome-vue-devtools插件解析

- 掌握ElectronBrowserJS:打造跨平台电子应用

- 前端导师教程:构建与部署社交证明页面

- Java多线程与线程安全在断点续传中的实现

- 免Root一键卸载安卓预装应用教程

- 易语言实现高级表格滚动条完美控制技巧

- 超声波测距尺的源码实现

- 数据可视化与交互:构建易用的数据界面

- 实现Discourse外聘回复自动标记的简易插件

- 链表的头插法与尾插法实现及长度计算

- Playwright与Typescript及Mocha集成:自动化UI测试实践指南

- 128x128像素线性工具图标下载集合

- 易语言安装包程序增强版:智能导入与重复库过滤

- 利用AJAX与Spotify API在Google地图中探索世界音乐排行榜