Allegro 16.3约束设置详解:线宽、线距与差分线配置

"Allegro 16.3的约束设置教程"

在Allegro 16.3中,约束设置是PCB设计的关键步骤,它确保了设计的合规性和电气性能。以下是对标题和描述中提到的知识点的详细说明:

一、普通单端线的线宽设置

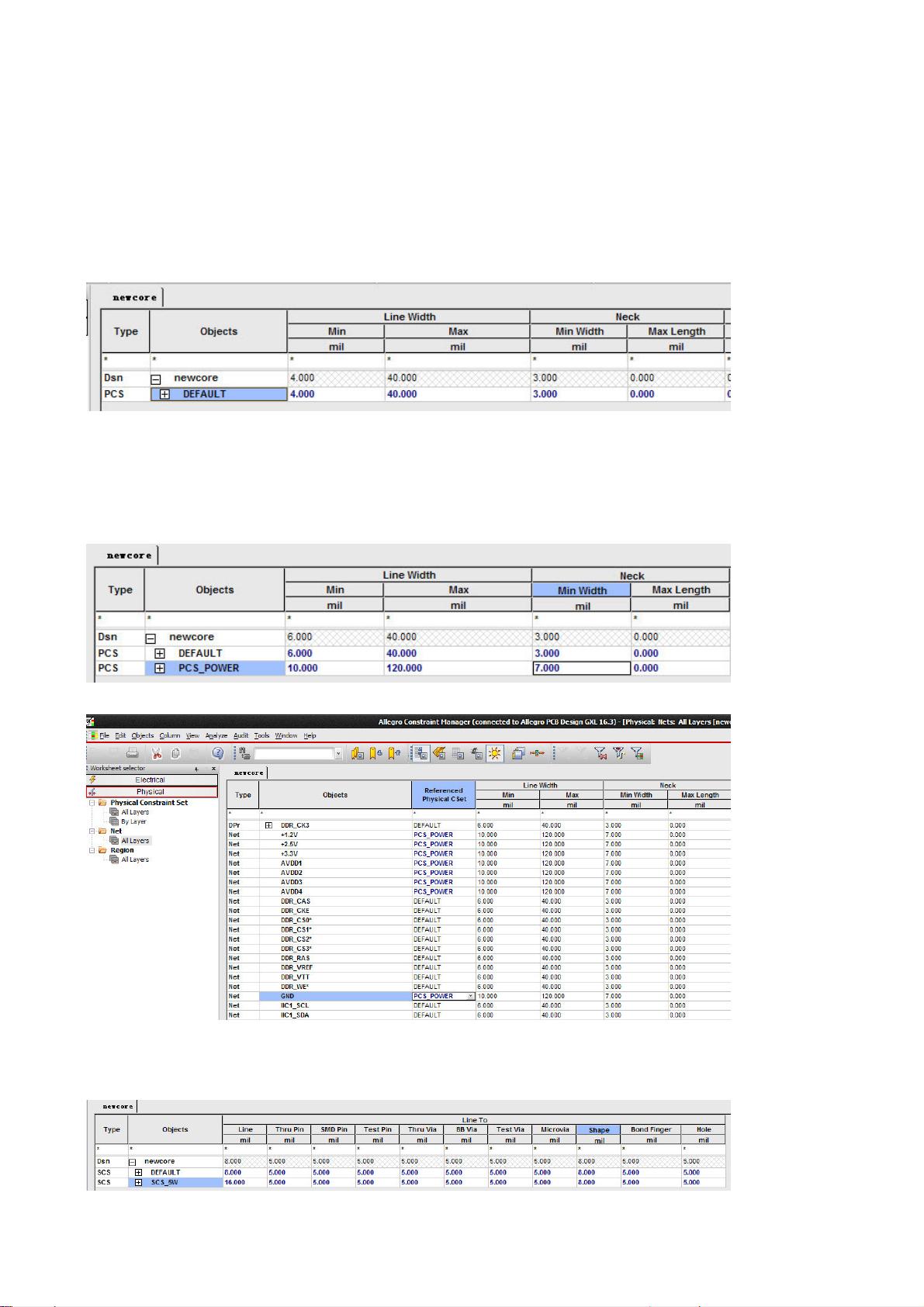

线宽设置通过Physical Constraint Set (PCS)完成。首先,从菜单中选择“physical”->“physicalconstraintset”->“alllayers”,然后右键点击并选择“create”->“physicalcset”创建一个新的PCS。例如,你可以命名为“PCS_NEWCORE”。若需针对不同层设定不同线宽,只需展开"default",修改所需层的线宽。在示例中,最小线宽设为4mil,最大为40mil,走线时默认采用最小线宽4mil。特殊情况下,如在BGA下需要更窄的线宽以适应紧密间距,可使用“NECKMODE”,通过右键选择“neckmode”切换到颈缩模式。

二、普通单端线的线距设置

线距设置由Spacing Constraint Set (SCS)控制。操作路径是“spacing”->“spacingconstraintset”->“alllayers”,同样右键创建新的SCS,例如“SCS_3W”和“SCS_5W”。3w和5w分别代表3 mil和5 mil的线距,适用于line-to-line和line-to-shape的平行距离。对于像linetohole、linetovia、linetopin等其他类型的线距,由于其特殊的物理特性,可以设置较小的值,如5mil。要为特定线应用5w规则,可以在“net”->“alllayers”中选择该线并应用“scs_5w”规则,如图所示,DDR的时钟线DDR_CK0被应用了5w规则,但这不包括差分线对内的间距。

三、差分线线宽、内线距的设置

差分线对的线宽和内部间距对信号完整性至关重要。在"physical"->"physicalconstraintset"下,创建专门的PCS规则来定义差分线对的线宽和内线距。差分对内两线之间的间距称为内线距,需要特别调整以优化信号质量。设置差分线的线宽和内线距,可以确保信号的对称性和减少串扰。

总结来说,Allegro 16.3的约束设置涵盖了单端线的线宽、线距以及差分线的特定规则,这些设置对实现高效且高质量的PCB设计至关重要。通过对这些参数的精确控制,设计者可以确保电路的电气性能和制造可行性。

相关推荐

zhao_cheng27

- 粉丝: 0

最新资源

- Cassinipp:无需安装IIS的便捷Web服务程序

- 同济第五版高等数学课本及章节答案下载

- MageSpec Magento PHP Spec工具的安装与使用

- 深入理解词法分析器的原理与应用

- 提升效率:终极输入法设置与优化工具

- STLinkV2.J28.M18固件升级及应用指南

- HTML5 canvas打造3D雪花飘落特效插件

- MySQL官方简体中文参考手册:全面数据库管理指南

- 掌握NPAPI:创建基础Firefox插件示例

- SJCL加密解密工具:页面JS实现方案

- IBM数据科学课程:完成课程10的最终项目

- 首次适应算法在操作系统课程设计中的应用分析

- C#实现的自定义图片九宫格拼图游戏

- 全屏滑动图片布局:HTML5 Flexbox网格设计

- STM32F4平台下MPU9250驱动优化与磁力计椭球拟合实例

- 谷歌地图坐标的纠偏加偏小工具使用指南