复旦大学集成电路设计导论:设计验证深度解析

需积分: 50 51 浏览量

更新于2024-07-09

收藏 1.59MB PDF 举报

“复旦大学-集成电路设计导论 第3节(7)设计验证-教程与笔记习题”

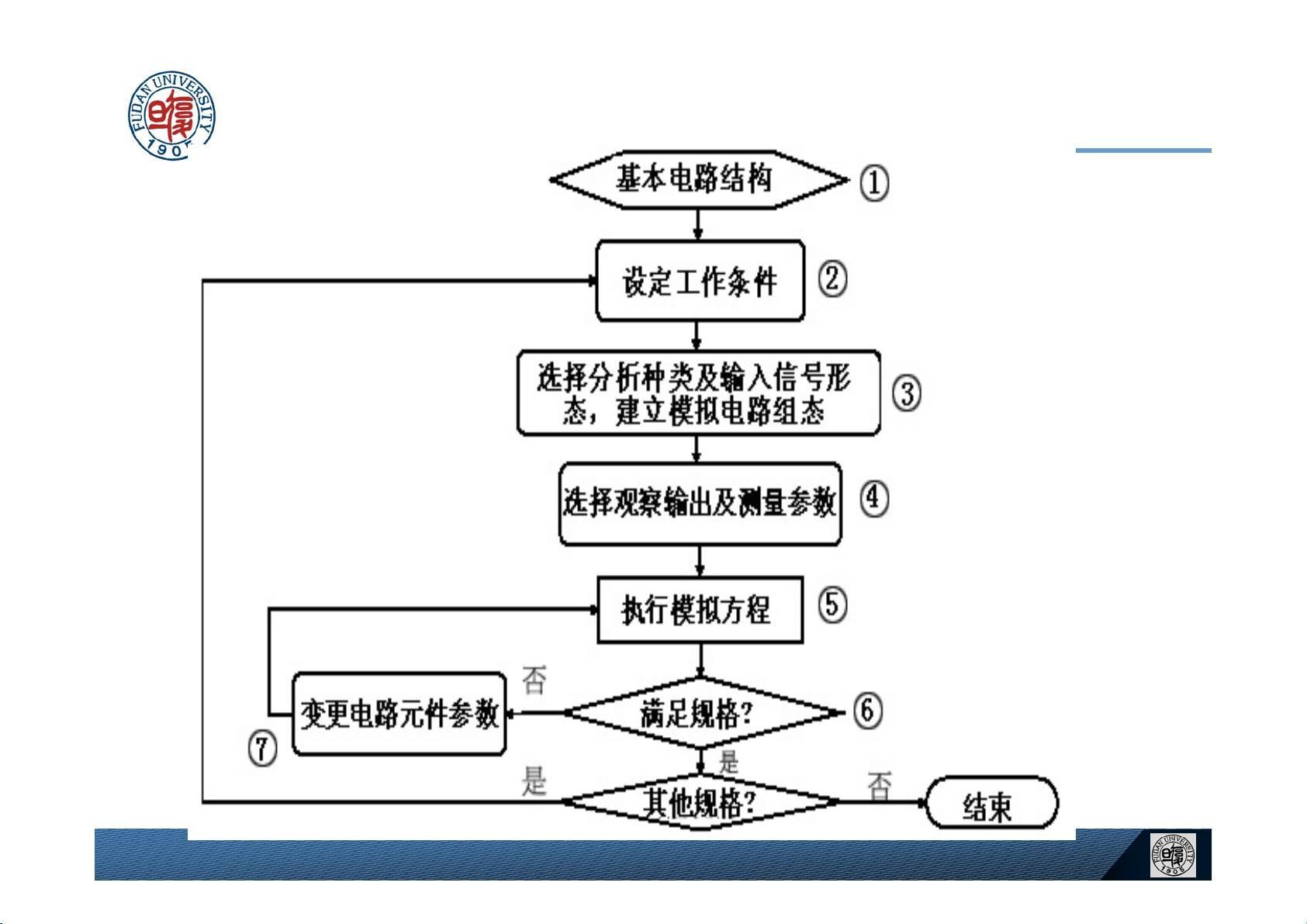

在集成电路设计领域,设计验证是一项至关重要的环节,确保设计的正确性和功能完整性。复旦大学的集成电路设计导论课程中,第三节课的第七部分详细介绍了设计验证的相关内容,包括模拟、时序验证、LVS验证、DRC和ERC、版图后仿真以及形式验证等关键步骤。

首先,设计验证可以分为设计验证和实现验证两个层面。设计验证关注的是设计是否符合预期,而实现验证则确保实际实现的设计与规格相符。在行为级,设计通常用高级语言如SystemVerilog或VHDL描述,这时的验证主要关注功能的正确性。

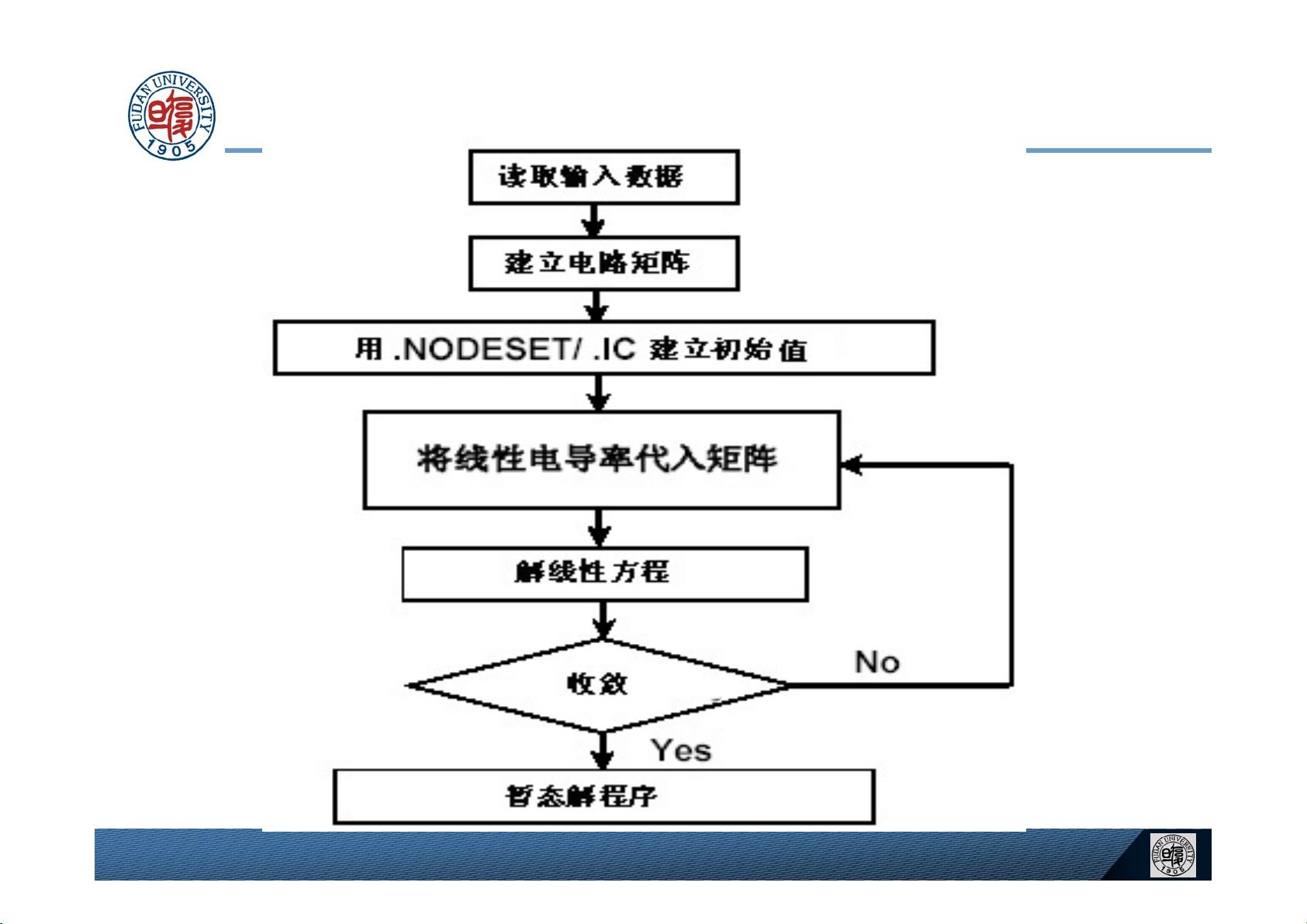

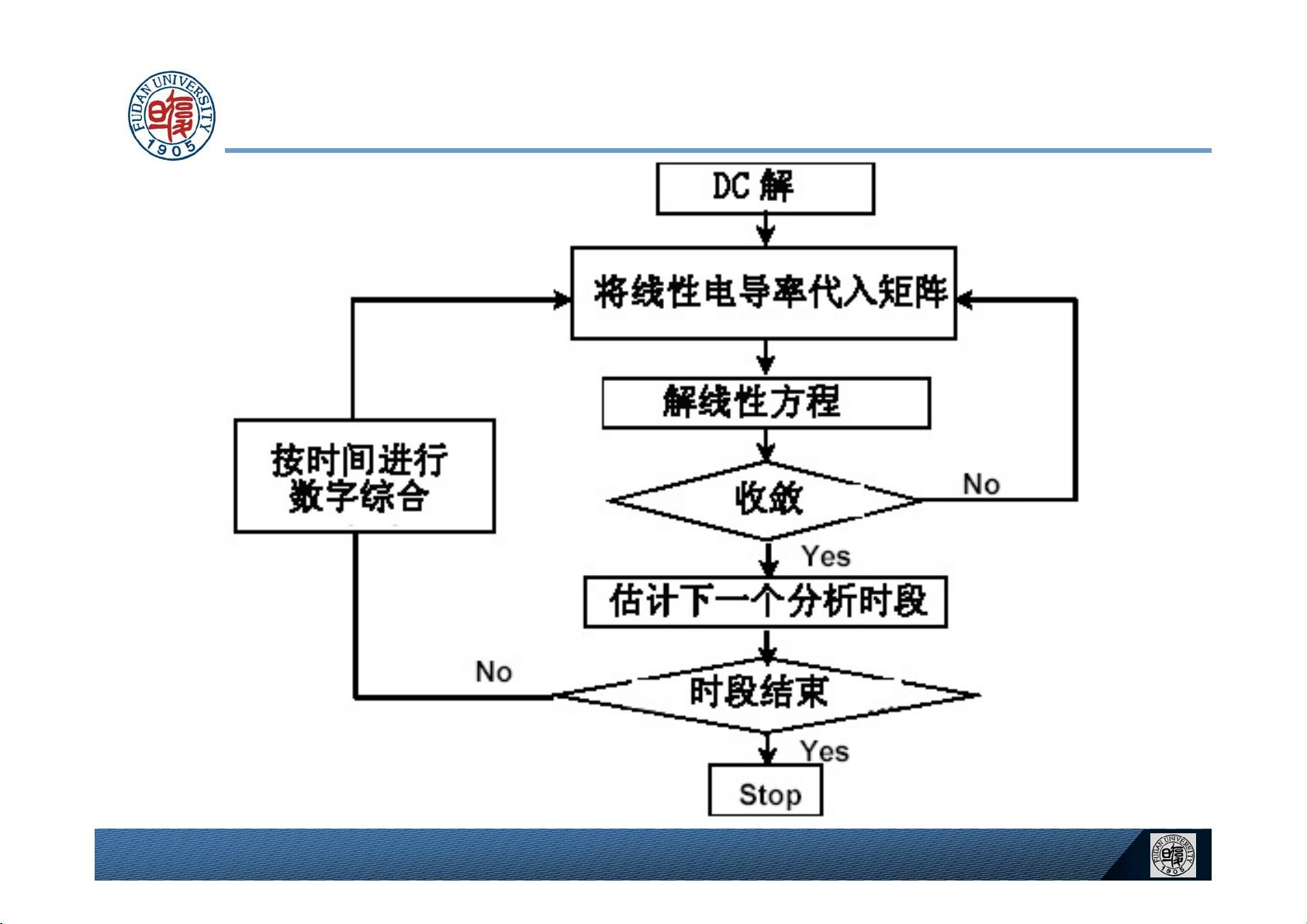

模拟是验证过程中的基础,包括电路级模拟、逻辑级模拟(门级模拟)、RTL级模拟和硬件模拟。电路级模拟关注晶体管级别的行为,适合验证基本电路单元;门级模拟在更抽象的层次上检查逻辑门的组合效果;RTL级模拟关注的是寄存器传输级的行为,与具体的物理实现无关,是最常用的设计验证方法;硬件模拟则是使用专门的硬件系统来运行设计,提供快速的性能评估。

时序验证涉及到设计的时序特性,确保设计满足速度要求,不出现时钟域交叉、竞争和冒险等问题。LVS(Layout vs. Schematic)验证是对电路布局与电路原理图的一致性检查;DRC(Design Rule Check)则用于检测设计是否违反了制造工艺的规则;ERC(Electrical Rule Check)关注电气规则,防止短路或开路等潜在问题。

版图后仿真是在版图完成之后进行的功能仿真,以确认布局布线不会影响设计的正确性。形式验证是一种数学证明的方法,通过分析设计的逻辑表达式,确定其是否满足所有可能的输入情况,能够更彻底地验证设计的正确性。

主要的验证策略包括随机测试向量生成、覆盖率驱动的验证、基于约束的随机化等,这些方法结合使用,能提高验证的效率和完备性。在编写测试平台(testbench)时,应考虑全面的测试场景,确保覆盖到设计的所有关键路径和边界条件。

设计验证是集成电路设计流程中的核心环节,通过多层面、多层次的验证手段,确保设计的高质量和可靠性。复旦大学的这堂课深入讲解了这些关键概念和技术,对于学习和理解集成电路设计验证有着重要的指导价值。

106 浏览量

147 浏览量

点击了解资源详情

178 浏览量

106 浏览量

212 浏览量

131 浏览量

186 浏览量

2021-05-20 上传

weixin_38665411

- 粉丝: 8

最新资源

- 范剑波《数据库原理及应用》教案全解

- VC代码mtl-2.1.2-21实用代码源文件分享

- 微信小程序环境下实现基本计算器功能的源代码解析

- Marlin固件升级指南与文件下载

- Lua5.1.4版本发布,官方源代码下载开启

- SSD5 Optional Exercise 4问题解答

- 可视化超级马拉松赛事Black Canyon Ultra数据

- GD Star Rating:全面强大的WordPress评分插件

- GTK+ 2.24.10版本的Windows平台压缩包介绍

- 仿头条样式WKWebView实现指南

- USB2.0万能驱动下载_安装与兼容性详细解析

- JA_CORONA:Joomla模板的设计与应用

- 提升WordPress博客互动性:推荐使用WP Thread Comment插件

- Angular项目开发与构建流程详解

- Visual C++视频技术方案宝典源码解析

- 基于逻辑回归的猫识别神经网络教程