"全定制IC设计流程:CADENCE工具应用与验证流程"

39 浏览量

更新于2024-01-05

收藏 360KB DOCX 举报

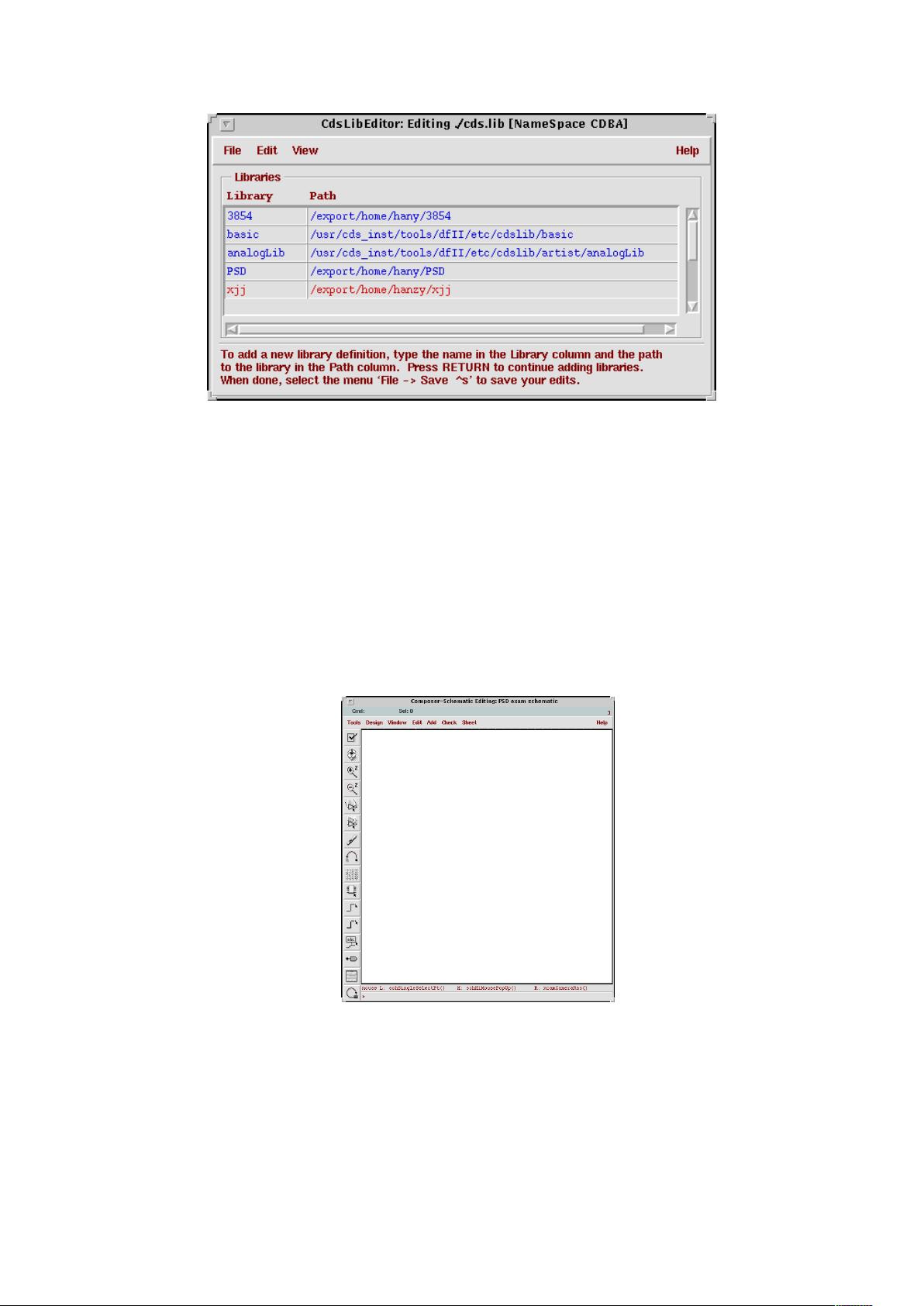

CADENCE全定制IC设计流程是一个为用户提供数字、数模及数模混合电路设计和幅员设计与幅员设计与验证的全套工具的流程。它利用Composer进行个层次的电路输入,Analog Artist仿真环境提供多种电路仿真工具与Cadence环境接口,Spectre电路仿真器则用于进行电路仿真与分析,以确保电路的正确性。Virtuoso则提供幅员编辑功能,Layout Synthesis可以进行模字MOS电路的自动幅员设计,而DLE和IC craftsman可以进行模拟或数模混合电路的幅员设计。而Diva、Dracula和Vampire三种幅员验证工具可以对不同规模的电路进行幅员验证,以确保幅员与电路的一致性。利用上述工具,用户可以很方便地将设计转化为现实。

全定制IC设计流程主要分为以下几个步骤。首先是电路仿真,用户可以使用Analog Artist和Spectre进行电路仿真和分析,确保电路的正确性。其次是设计输入,用户可以利用Composer进行个层次的电路输入。然后是幅员设计,幅员设计可以分为两种情况,一种是模字MOS电路的自动幅员设计,可以使用Layout Synthesis实现;另一种是模拟或数模混合电路的幅员设计,可以使用DLE和IC craftsman进行。接下来是幅员编辑,用户可以利用Virtuoso进行幅员编辑,对电路进行进一步的优化和调整。最后是幅员验证,用户可以使用Diva、Dracula和Vampire三种幅员验证工具对不同规模的电路进行幅员验证,确保幅员与电路的一致性。

总结起来,CADENCE全定制IC设计流程是一个为用户提供数字、数模及数模混合电路设计和幅员设计与幅员设计与验证的全套工具的流程,它利用多种工具实现了电路仿真、设计输入、幅员设计、幅员编辑和幅员验证等各个环节,使用户能够方便地将设计转化为现实。这个流程可以应用于各种全定制IC设计项目,帮助用户提高设计效率并确保电路的正确性和一致性。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-11-17 上传

2019-07-25 上传

2022-10-27 上传

2021-10-07 上传

2021-10-25 上传

2020-06-29 上传

zzzzl333

- 粉丝: 802

- 资源: 7万+

最新资源

- Java毕业设计项目:校园二手交易网站开发指南

- Blaseball Plus插件开发与构建教程

- Deno Express:模仿Node.js Express的Deno Web服务器解决方案

- coc-snippets: 强化coc.nvim代码片段体验

- Java面向对象编程语言特性解析与学生信息管理系统开发

- 掌握Java实现硬盘链接技术:LinkDisks深度解析

- 基于Springboot和Vue的Java网盘系统开发

- jMonkeyEngine3 SDK:Netbeans集成的3D应用开发利器

- Python家庭作业指南与实践技巧

- Java企业级Web项目实践指南

- Eureka注册中心与Go客户端使用指南

- TsinghuaNet客户端:跨平台校园网联网解决方案

- 掌握lazycsv:C++中高效解析CSV文件的单头库

- FSDAF遥感影像时空融合python实现教程

- Envato Markets分析工具扩展:监控销售与评论

- Kotlin实现NumPy绑定:提升数组数据处理性能