Verilog实现任意分频技术详解

"任意分频的实现(verilog)"

在数字系统设计中,分频是一种常见的时序处理任务,用于将较高频率的输入时钟转换为较低频率的输出时钟。本文主要介绍如何使用Verilog语言实现任意分频器,并探讨了不同类型的分频方法。

1. 偶数倍(2N)分频

偶数倍分频的实现相对简单,主要通过一个模N计数器实现。当计数器从0计数到N-1时,输出时钟翻转,并对计数器进行复位,使其重新从0开始计数。这个过程不断重复,即可实现2N倍的分频。例如,如果N=4,那么输入时钟的每个4个周期,输出时钟会有一个脉冲。

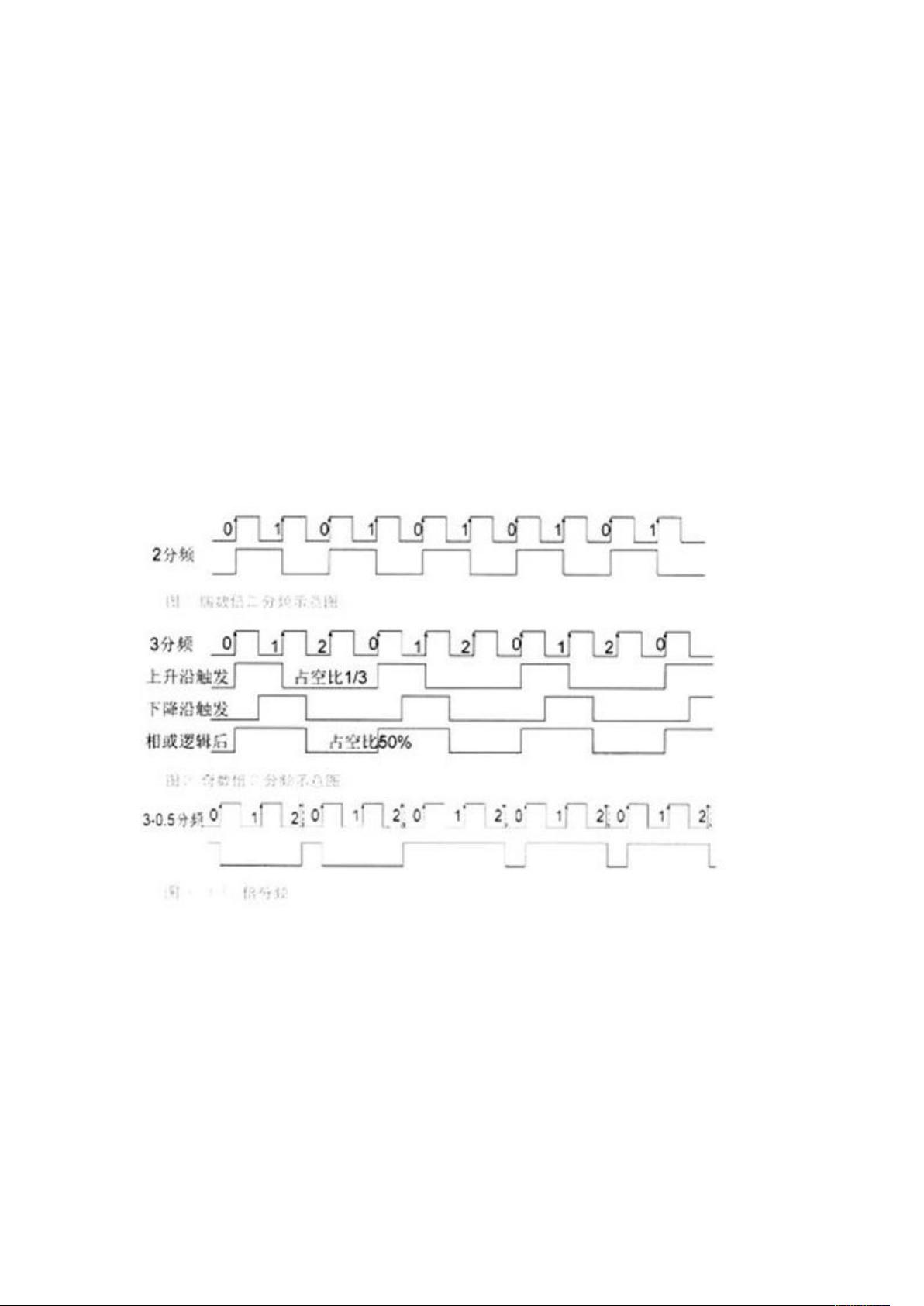

2. 奇数倍(2N+1)分频

- 非50%占空比:奇数倍分频可以实现占空比为X/(2N+1)或(2N+1-X)/(2N+1)的时钟,使用模(2N+1)计数器。当计数器从0计数到X时,输出时钟翻转,然后在计数器达到2N时再次翻转并复位计数器。

- 50%占空比:通过在输入时钟的下降沿触发计数器的翻转,可以得到占空比为50%的奇数倍分频时钟。这种方法涉及两个计数器,一个按照(1)中的方式工作,另一个则在下降沿翻转,两者通过逻辑或操作结合,得到50%占空比的时钟。

3. N-0.5倍分频

这种情况较为特殊,需要在计数器达到N-1后,经过半个周期再次翻转。可以利用计数器在CLK下降沿时接收到上升沿脉冲,使其在达到N时复位并翻转输出时钟。

4. 任意小数分频(N+A/B)

实现任意小数分频,可以结合整数分频器(N和N+1)以及脉冲计数技术。设整数分频器N出现的频率为a,则有N×a + (N+1)×(B-a) = N×B + A,解得a=B-A。因此,N+1出现的频率为A。例如,要实现7+2/5分频,选取a=3,这样7×3+8×2就能得到所需的小数分频值。然而,由于小数分频器的输出脉冲可能存在抖动,实际应用中较少使用。

在Verilog编程中,设计分频器通常包括以下几个步骤:

1. 定义计数器:使用reg类型变量创建一个计数器,初始值为0。

2. 状态机:可以使用状态机来控制计数器的计数过程和翻转输出时钟的时刻。

3. 条件判断:在时钟边沿检测条件,如计数器达到特定值时,改变输出时钟状态并复位计数器。

4. 复位和同步:确保在系统复位时,计数器能正确复位,并通过同步逻辑避免毛刺。

5. 综合和仿真:完成代码编写后,进行综合和仿真验证,确保分频器满足设计需求。

在实际设计中,除了上述基本原理外,还需要考虑电源效率、时序约束、同步设计原则以及可能的噪声影响等因素。任意分频器的设计可以为各种数字系统提供灵活的时钟管理方案,例如在通信系统、数字信号处理和时钟恢复等领域有广泛应用。

338 浏览量

398 浏览量

922 浏览量

207 浏览量

134 浏览量

createfly

- 粉丝: 2

最新资源

- 开发轻量级微服务架构--从理论到实践

- 构建高效预输入拼写检查器的Typesense技术演示

- LeetCode练习笔记:掌握数组、链表与数据结构

- 构建个人跟踪数据库的Django Rest框架项目

- VB汽车训练场收费系统毕业设计源码及完整运行系统

- Vue.js实现PDF文件功能的开发教程

- CCleaner软件安装包:优化你的电脑性能

- 全面解读Shiro在Java Web及Spring应用中的核心使用

- NMLS开源软件:自动连接ActiveDirectory扩展网络驱动器

- 深入探究算法课程:搜索、排序与高级技术

- Hacko-1-Hephaestus: Hackowasp 3.0的兼容存储库

- Infinity-ID.github.io前端开发技术解析

- PCA人脸识别技术在Matlab中的实现

- 财务人员求职简历模板下载及使用指南

- Python库missinglink_sdk-0.732-py2.py3-none-any.whl安装指南

- 浏览器选项卡间简易通信技术实现