2370 IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS–I: REGULAR PAPERS, VOL. 63, NO. 12, DECEMBER 2016

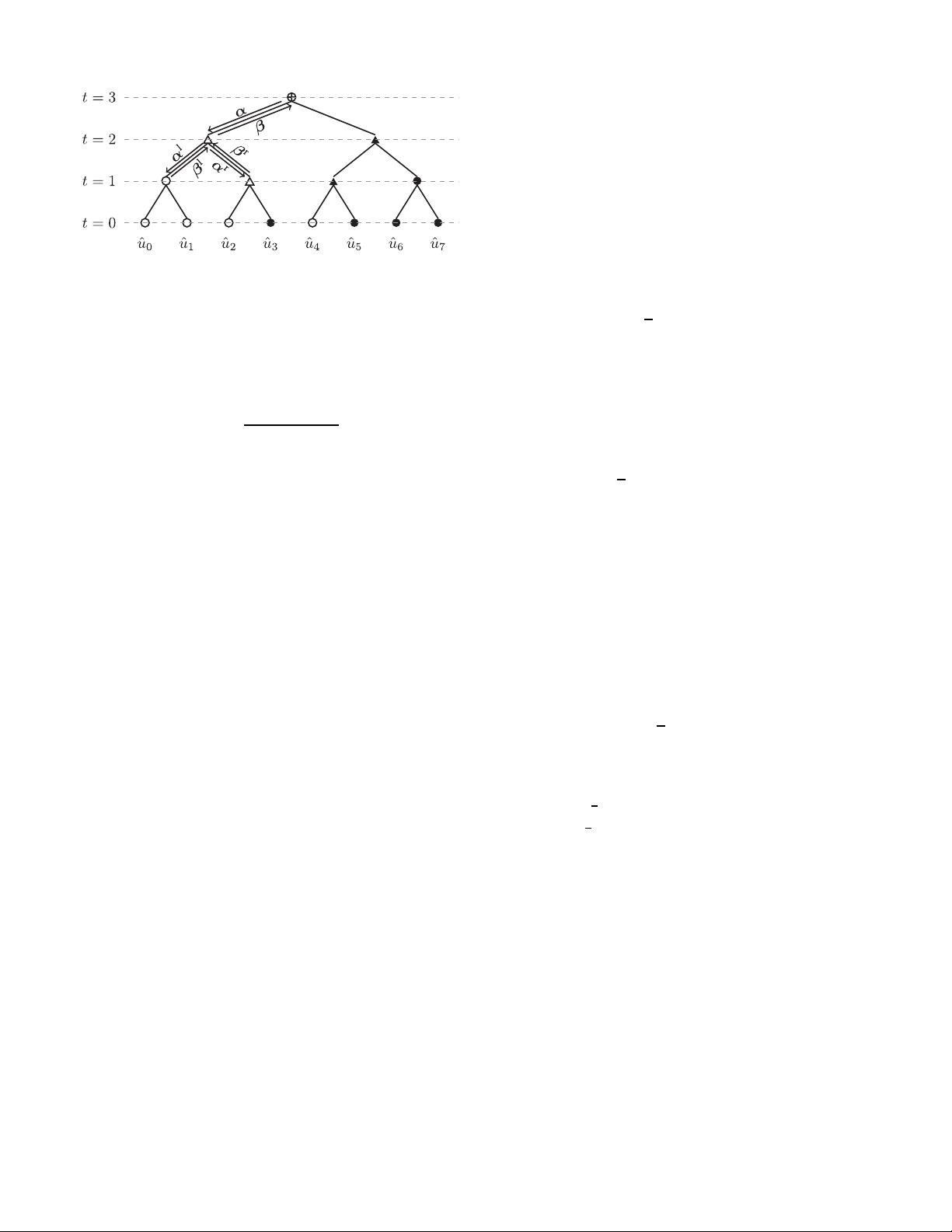

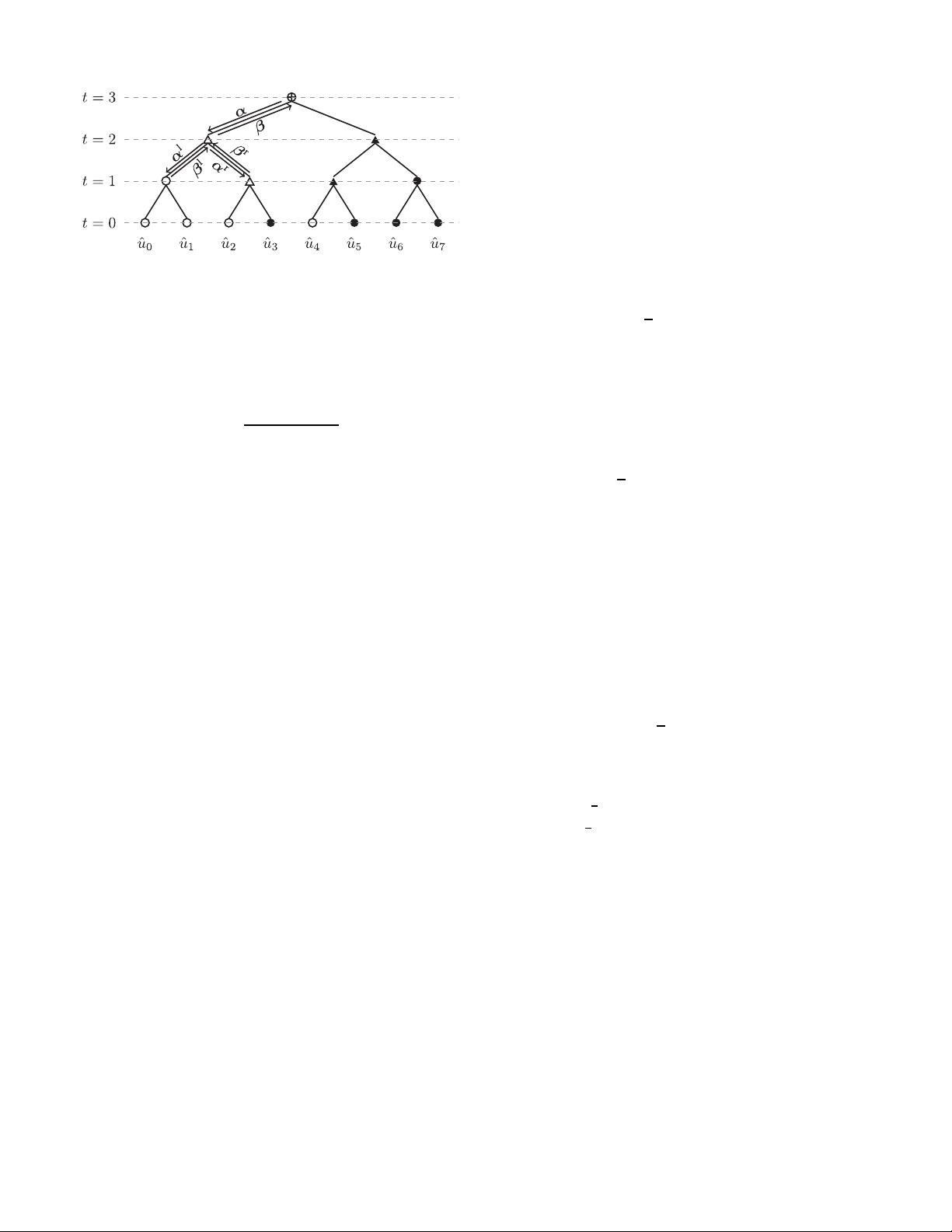

Fig. 2. SC decoding example for P(8, 4) and {u

0

, u

1

, u

2

, u

4

}∈F .

β ={β

0

,β

1

,...,β

2

t

−1

} are passed from a child node to

its parent node. The elements of the left and right messages

α

l

={α

l

0

,α

l

1

,...,α

l

2

t−1

−1

} and α

r

={α

r

0

,α

r

1

,...,α

r

2

t−1

−1

},

each a vector of 2

t−1

values, are calculated as

α

l

i

= ln

1 + e

α

i

+α

i+2

t−1

e

α

i

+ e

α

i+2

t−1

, (5)

α

r

i

= α

i+2

t−1

+ (1 − 2β

l

i

)α

i

, (6)

while the elements of β, a vector of 2

t

bits, are computed

using the left and right messages β

l

={β

l

0

,β

l

1

,...,β

l

2

t−1

−1

}

and β

r

={β

r

0

,β

r

1

,...,β

r

2

t−1

−1

}

β

i

=

β

l

i

⊕ β

r

i

, if i < 2

t−1

,

β

r

i−2

t−1

, otherwise,

(7)

where ⊕ denotes the bitwise XOR and the interval i < 2

t−1

discriminates between bits considered by the left and the right

child. At a leaf node, the i-th bit ˆu

i

is estimated as

ˆu

i

=

0, if i ∈ F or α

i

≥ 0,

1, otherwise.

(8)

Due to the data dependencies, each node receives α first,

then sends α

l

, receives β

l

, sends α

r

, receives β

r

, and finally

sends β, in this order. A hardware-friendly version of (5),

proposed in [2], can be written as

α

l

i

= sgn(α

i

) sgn(α

i+2

t−1

) min(|α

i

|, |α

i+2

t−1

|), (9)

where

sgn(α

i

) =

−1, if α

i

< 0,

1, otherwise.

(10)

C. Fast-SSC Decoding

In SC, the estimation of each bit requires the knowledge of

previously estimated bits. The serial nature of this bit by bit

estimation process limits the speed of SC decoding algorithm.

In order to increase the speed of SC, [6] and [7] observed

four different constituent codes: their decoding can be carried

out in a more efficient way than fully exploring the decoding

tree. These codes are shown in Fig. 2. White circles are Rate-0

nodes, whose leaves consist of frozen bits only, while black

circles are Rate-1 nodes, where all leaves are information

bits. All leaf nodes at t = 0 are either Rate-0 or Rate-1,

being either single frozen bits or single information bits. White

triangles represent Rep nodes, where only the rightmost leaf

is an information bit. Finally, black triangles represent SPC

nodes, i.e., nodes whose leaves are all information bits, except

for the leftmost one. Note that SPC and Rep nodes at t = 1

are equivalent.

Since Rate-0 nodes correspond to frozen bits, they can be

estimated as

β

i

= 0. (11)

Rate-1 nodes correspond to all-information bit vectors.

A direct hard estimate based on the LLR values at a Rate-1

node can be carried out as

β

i

=

1

2

(

1 − sgn

(

α

i

))

. (12)

Rep nodes have one information bit at the leaf branches and

the bit estimate of this information bit is the bit estimate of

all the bits in a Rep node. The LLR value of the information

bit in a Rep node can be calculated as

2

t

−1

i=0

α

i

. Therefore,

the bit estimates at a Rep node can be found as

β

i

=

1

2

⎛

⎝

1 − sgn

⎛

⎝

2

t

−1

i=0

α

i

⎞

⎠

⎞

⎠

. (13)

SPC nodes have the even-parity constraint. In SC decoding,

this constraint is imposed by checking the hard estimate of

the least reliable bit. If this bit does not satisfy the even-parity

constraint, then it is flipped. The least reliable bit in an SPC

node is found as

i

min

= arg min

0≤i<2

t

(|α

i

|), (14)

and the parity of it is derived as

γ =

2

t

−1

i=0

1

2

(

1 − sgn

(

α

i

))

. (15)

Finally, the bit estimate in an SPC node is calculated as

β

i

=

1

2

(

1 − sgn

(

α

i

))

⊕ γ, if i = i

min

,

1

2

(

1 − sgn

(

α

i

))

, otherwise.

(16)

The advantage of Fast-SSC is that the decoder is optimal,

i.e., it performs exactly as the original SC decoder. Since parts

of the code can be decoded in parallel, Fast-SSC can decode

a received vector with a much higher speed than SC.

D. List Decoding

To improve the error-correction performance of SC for

codes with moderate lengths, the SCL decoding algorithm

estimates a bit with both its possible values 0 and 1. In order

to control the exponential increase in the complexity of this

algorithm, a set of L codeword candidates is memorized at all

times and every new bit estimate produces 2L new candidates,

half of which must be discarded. To this purpose, a Path

Metric (PM) is associated to each codeword candidate (path)

and updated at every new estimation: it can be considered a

cost function, and the L paths with the lowest PMs are allowed