瑞泰DM642实验箱原理图分享与注意事项

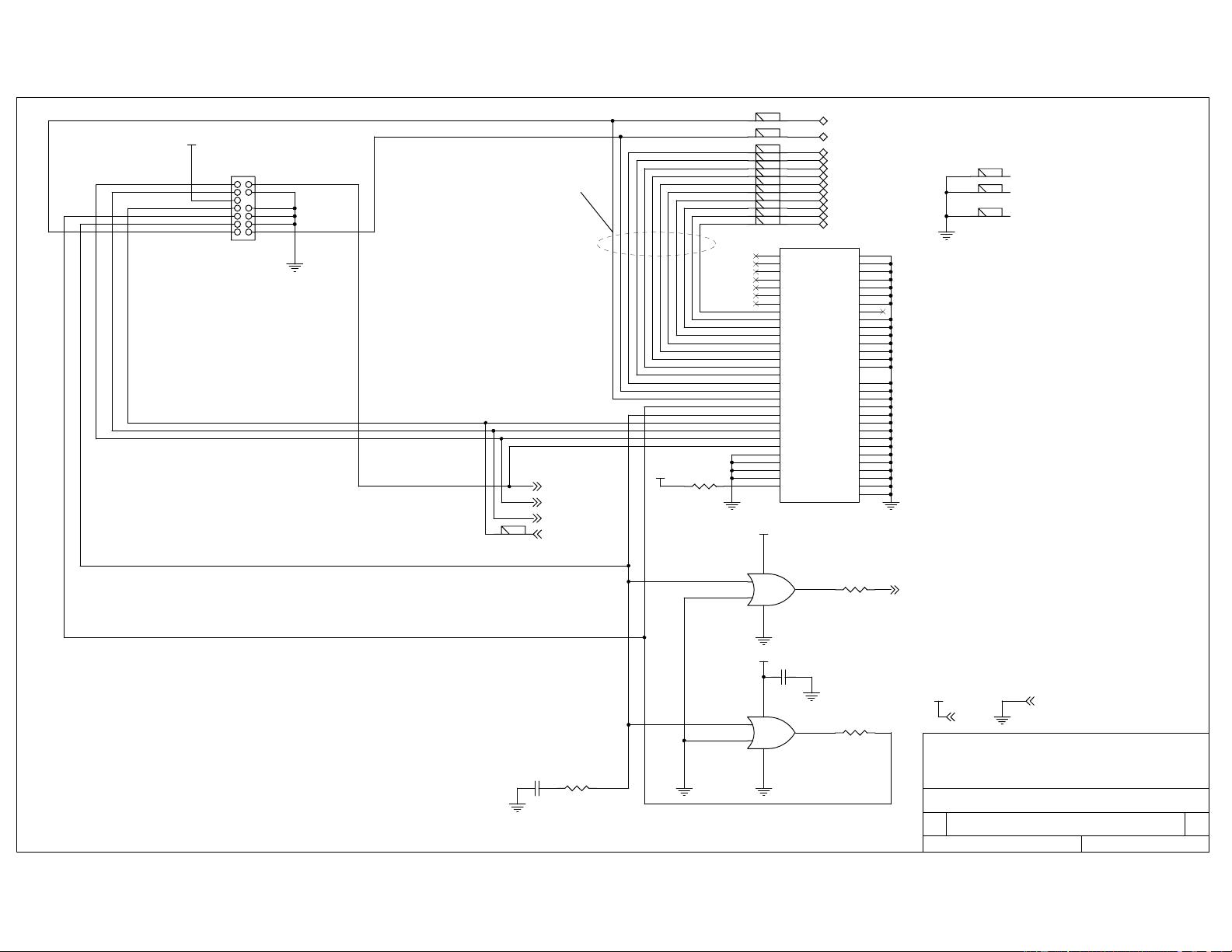

本文档分享的是瑞泰DM642的PCI接口实验箱原理图,由ICETEK提供。该原理图包含了详细的设计布局和电气特性,对于理解DM642这款嵌入式处理器在实际应用中的工作原理以及PCIE接口设计至关重要。 DM642是一款高性能的嵌入式处理器,专为工业控制、通信和多媒体应用设计,其架构包含时钟管理、复位、中断系统、定时器和IIC接口等功能。在提供的原理图中,你可以找到: 1. **信号路由**:分为顶层(TOP-SIGNALROUTING)、地平面(GROUNDPLANE)、内层1至4的信号路径,确保信号完整性,如VCC3PLANE(3.3V电源层)等,以及信号的底部路由(BOTTOM-SIGNALROUTING)。 2. **布局规范**:强调了匹配阻抗(50+/-5Ω),铜和金的镀层厚度(0.5oz Cu/W 和 0.5oz Au),以及最小的线宽和间距要求(4 mils 和 10/19 mils的Via尺寸)。 3. **层堆叠**:强调了层间的连接规则,要求线路到Manhattan距离的偏差不超过10%,以维持信号传输的精确性。 4. **功能模块**:包括详细的模块索引,如EVM(评估板)注释、用户选项和配置、时钟、复位、中断、定时器、IIC接口、EMIF(外部内存接口)、视频端口、PCI/HPI/EMAC(PCI/高速外围接口/以太网MAC)接口、电源引脚、SDRAM(静态随机存取存储器)以及扩展EMIF缓冲区等。 5. **电源管理**:特别提到了电源管理,可能涉及不同的电压供应和电路保护,这对于稳定系统运行和电源效率至关重要。 这份原理图对于电子工程师、硬件开发者以及对瑞泰DM642平台进行实验或原型设计的人来说,是宝贵的参考资料,能够帮助他们理解和实现基于DM642的系统设计,提升设计的准确性和可靠性。通过遵循其中的指导,可以优化信号路径,减少干扰,并确保组件间的电气兼容性。

剩余24页未读,继续阅读

- 粉丝: 171

- 资源: 2138

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- zlib-1.2.12压缩包解析与技术要点

- 微信小程序滑动选项卡源码模版发布

- Unity虚拟人物唇同步插件Oculus Lipsync介绍

- Nginx 1.18.0版本WinSW自动安装与管理指南

- Java Swing和JDBC实现的ATM系统源码解析

- 掌握Spark Streaming与Maven集成的分布式大数据处理

- 深入学习推荐系统:教程、案例与项目实践

- Web开发者必备的取色工具软件介绍

- C语言实现李春葆数据结构实验程序

- 超市管理系统开发:asp+SQL Server 2005实战

- Redis伪集群搭建教程与实践

- 掌握网络活动细节:Wireshark v3.6.3网络嗅探工具详解

- 全面掌握美赛:建模、分析与编程实现教程

- Java图书馆系统完整项目源码及SQL文件解析

- PCtoLCD2002软件:高效图片和字符取模转换

- Java开发的体育赛事在线购票系统源码分析

信息提交成功

信息提交成功