Xilinx ISE13.2教程:基于VerilogHDL的FPGA设计流程

需积分: 12 115 浏览量

更新于2024-07-22

收藏 3.57MB PPT 举报

"这篇教程详细介绍了使用Xilinx FPGA开发软件ISE13.2进行数字系统设计的流程,特别强调了基于Verilog HDL语言的设计步骤。教程涵盖了从启动软件、新建工程、设置工程属性到创建设计文件等多个环节,旨在帮助初学者掌握ISE13.2的使用方法。"

在数字系统设计领域,EDA(电子设计自动化)工具是必不可少的,而Xilinx ISE13.2是其中的一款重要软件,用于FPGA(现场可编程门阵列)的开发。该教程首先指导用户如何启动ISE13.2,提供了两种方法:通过开始菜单或者直接点击桌面快捷图标。

设计流程的核心是新建工程。在创建新工程时,用户需要填写工程名称,如“counter”,并选择工程的保存位置。接下来,工程配置是关键步骤,包括指定产品类别、芯片系列(Family)、具体芯片型号、封装类型、速度信息,以及选择综合工具(如XST)和仿真工具(如ISim),同时确定使用Verilog HDL语言进行设计。

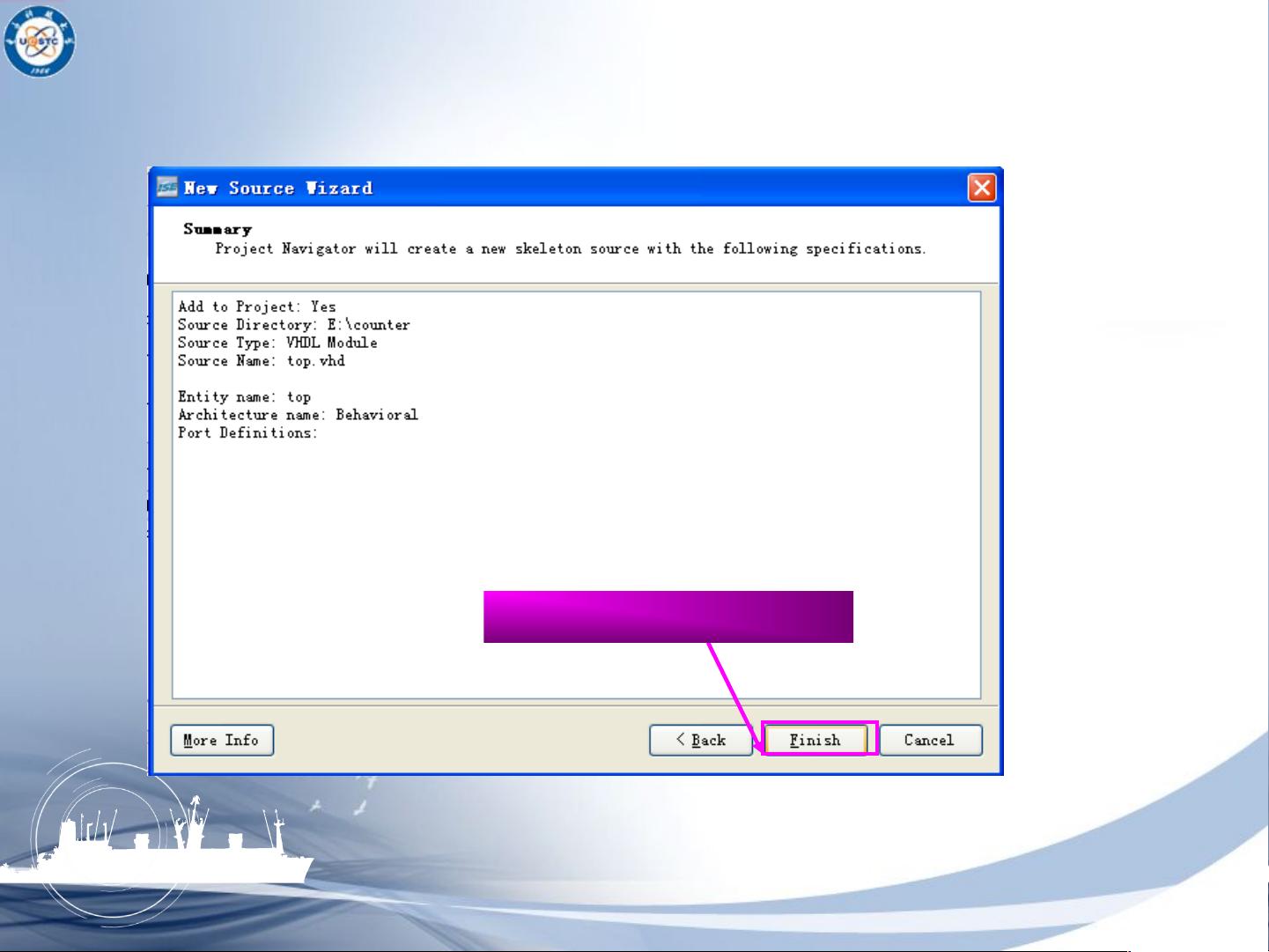

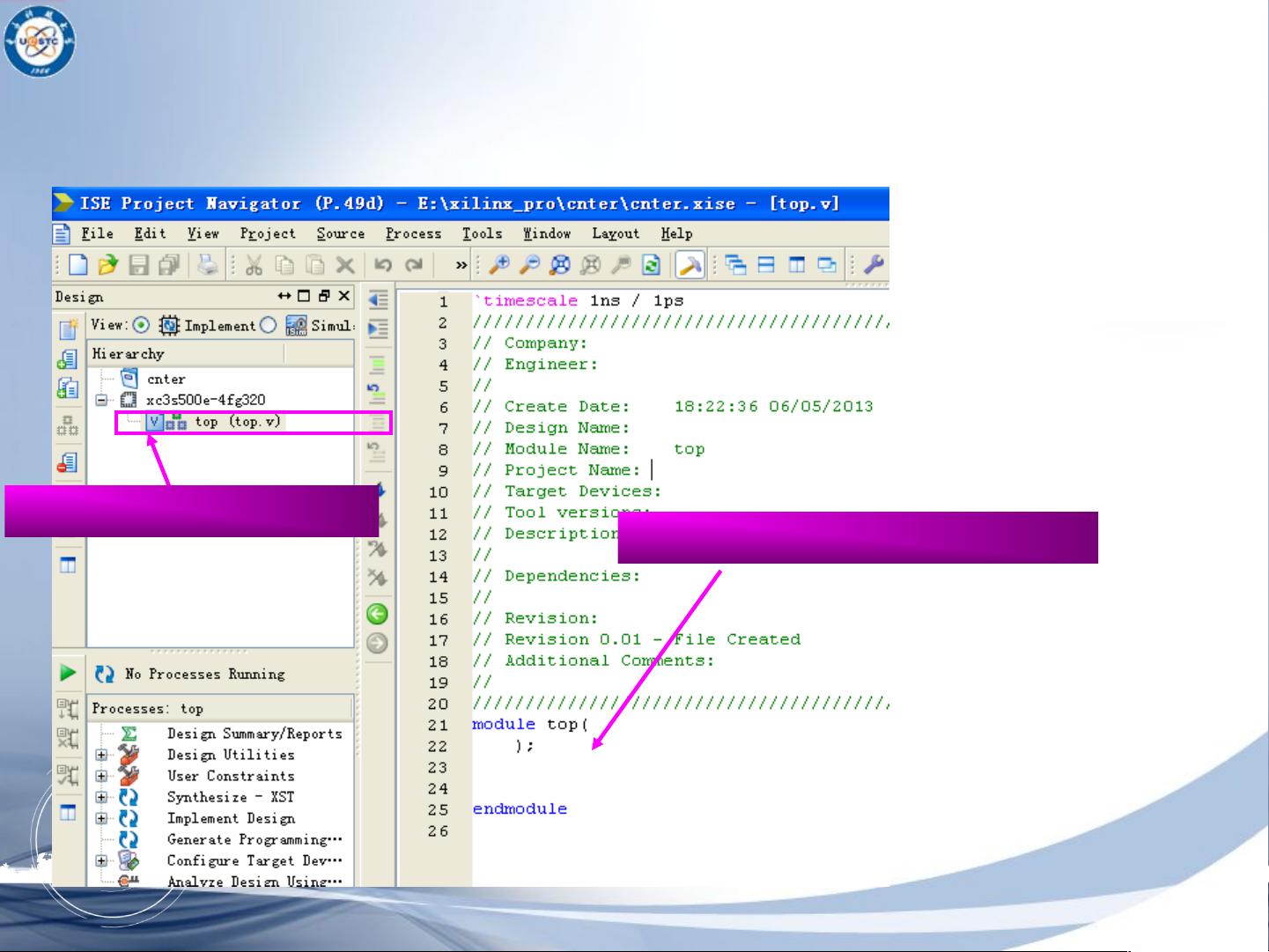

完成这些设定后,点击“Finish”按钮,系统会生成一个空的工程框架。这个框架包含了工程的基本结构,用户可以在此基础上添加设计元素。为了开始设计,用户需要创建新的设计文件。在弹出的菜单中,有多种文件类型可供选择,如块存储器映像文件、Chipscope在线逻辑分析仪定义、实现约束文件等,但本教程选择了Verilog HDL模块模板。

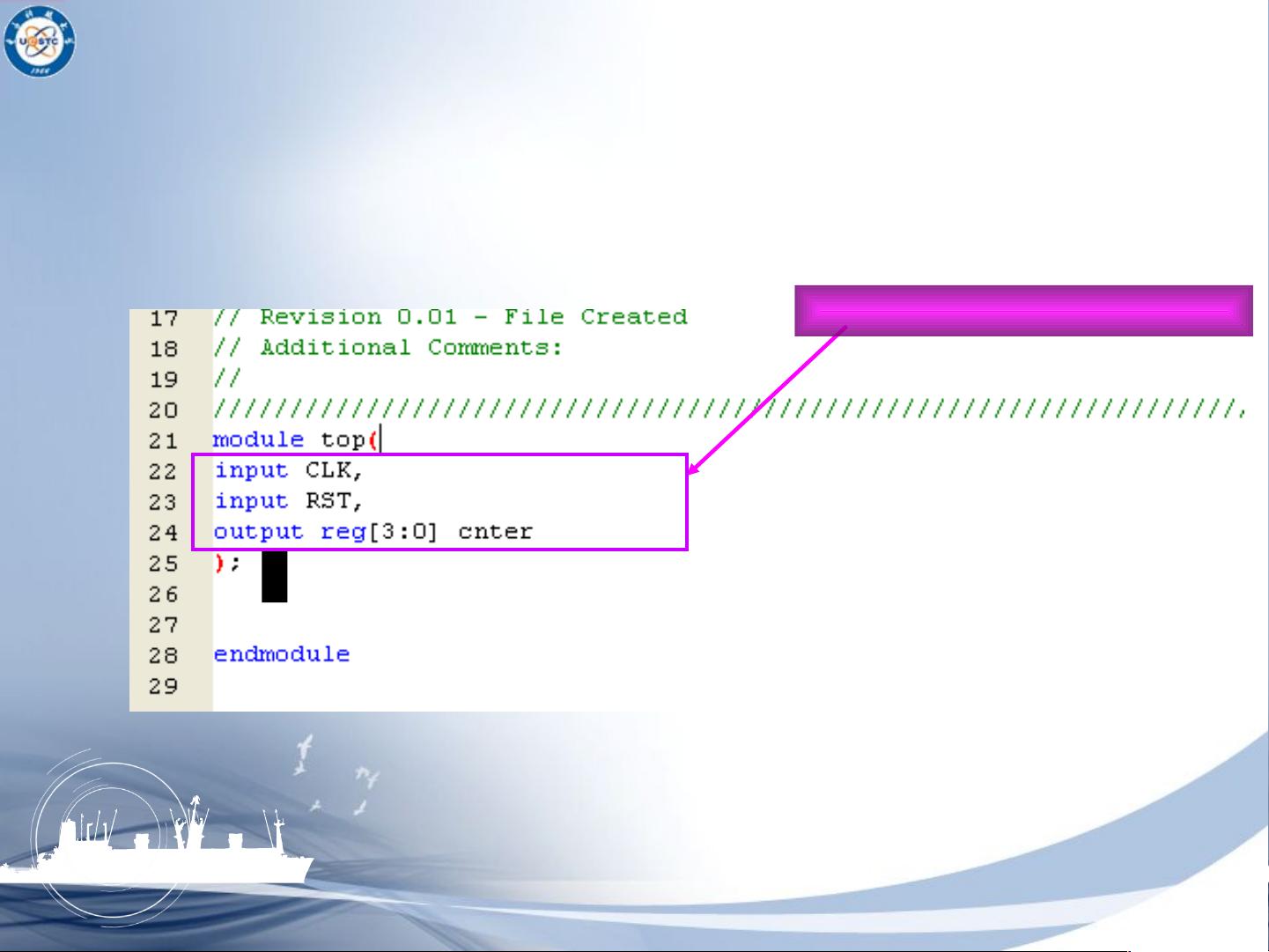

创建Verilog HDL模块时,用户需命名模块,例如“top”。确认后,继续点击“Next”按钮,系统会自动生成模板代码,用户即可在此基础上编写具体的Verilog HDL代码,实现数字系统的逻辑功能。

这个过程涵盖了从工程创建到设计文件建立的基本步骤,是理解ISE13.2工作流程的关键。通过这个教程,学习者能够逐步熟悉如何利用Verilog HDL在ISE13.2中搭建和实现数字系统,为进一步的FPGA开发打下基础。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2012-05-12 上传

105 浏览量

2014-08-18 上传

2022-07-15 上传

2015-06-09 上传

2018-11-15 上传

qweqwtrdsafdsger

- 粉丝: 2

- 资源: 6

最新资源

- 俄罗斯RTSD数据集实现交通标志实时检测

- 易语言开发的文件批量改名工具使用Ex_Dui美化界面

- 爱心援助动态网页教程:前端开发实战指南

- 复旦微电子数字电路课件4章同步时序电路详解

- Dylan Manley的编程投资组合登录页面设计介绍

- Python实现H3K4me3与H3K27ac表观遗传标记域长度分析

- 易语言开源播放器项目:简易界面与强大的音频支持

- 介绍rxtx2.2全系统环境下的Java版本使用

- ZStack-CC2530 半开源协议栈使用与安装指南

- 易语言实现的八斗平台与淘宝评论采集软件开发

- Christiano响应式网站项目设计与技术特点

- QT图形框架中QGraphicRectItem的插入与缩放技术

- 组合逻辑电路深入解析与习题教程

- Vue+ECharts实现中国地图3D展示与交互功能

- MiSTer_MAME_SCRIPTS:自动下载MAME与HBMAME脚本指南

- 前端技术精髓:构建响应式盆栽展示网站