5

4

3

2

1

D D

C C

B B

A

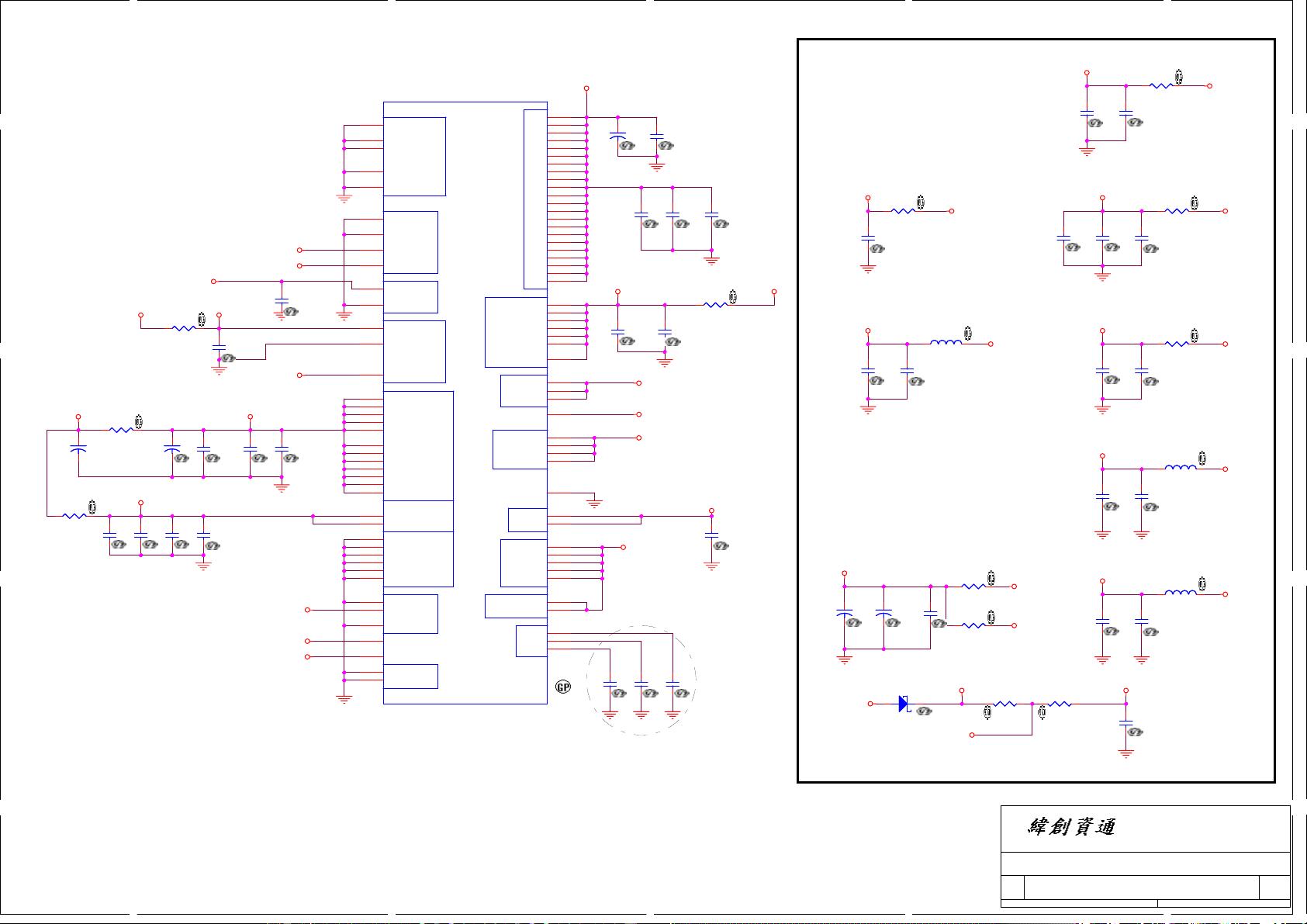

PEGCOMP

TXN13

TXN14

TXN15

TXN12

TXN2

TXN0

TXN5

TXN3

TXN4

TXP13

TXP14

TXP15

TXP12

TXP2

TXP0

TXP5

TXP3

TXP4

TXP1

TXP8

TXP6

TXP11

TXP9

TXP10

TXP7

TXN1

TXN8

TXN6

TXN11

TXN9

TXN10

TXN7

1D05V_S0

PEG_TXN8 41

PEG_TXN9 41

PEG_TXN10 41

PEG_TXN11 41

PEG_TXN12 41

PEG_TXN13 41

PEG_TXN14 41

PEG_TXN15 41

PEG_TXP8 41

PEG_TXP9 41

PEG_TXP10 41

PEG_TXP11 41

PEG_TXP12 41

PEG_TXP13 41

PEG_TXP14 41

PEG_TXP15 41

PEG_TXP0 41

PEG_TXP1 41

PEG_TXP2 41

PEG_TXP3 41

PEG_TXP4 41

PEG_TXP5 41

PEG_TXP6 41

PEG_TXP7 41

PEG_TXN0 41

PEG_TXN1 41

PEG_TXN2 41

PEG_TXN3 41

PEG_TXN4 41

PEG_TXN5 41

PEG_TXN6 41

PEG_TXN7 41

PEG_RXP3 41

PEG_RXP7 41

PEG_RXP11 41

PEG_RXP15 41

PEG_RXN3 41

PEG_RXN7 41

PEG_RXN11 41

PEG_RXN15 41

PEG_RXN4 41

PEG_RXN8 41

PEG_RXN12 41

PEG_RXN0 41

PEG_RXN5 41

PEG_RXN9 41

PEG_RXN13 41

PEG_RXN1 41

PEG_RXN2 41

PEG_RXN6 41

PEG_RXN10 41

PEG_RXN14 41

PEG_RXP4 41

PEG_RXP8 41

PEG_RXP12 41

PEG_RXP0 41

PEG_RXP5 41

PEG_RXP9 41

PEG_RXP13 41

PEG_RXP1 41

PEG_RXP2 41

PEG_RXP6 41

PEG_RXP10 41

PEG_RXP14 41

Title

Size Document Number Rev

Date: Sheet

of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Pamirs-Discrete

SA

CRESTLINE(3/6)-VGA/LVDS/TV

A3

947

Monday, December 18, 2006

<Core Design>

Title

Size Document Number Rev

Date: Sheet

of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Pamirs-Discrete

SA

CRESTLINE(3/6)-VGA/LVDS/TV

A3

947

Monday, December 18, 2006

<Core Design>

Title

Size Document Number Rev

Date: Sheet

of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Pamirs-Discrete

SA

CRESTLINE(3/6)-VGA/LVDS/TV

A3

947

Monday, December 18, 2006

<Core Design>

1 = Enable *

CFG[18:17] Reversed

SDVO_CTRLDATA 0 = No SDVO Device Present *

1 = SDVO Device Present

CFG19(DMI Lane Reversal)

0 = Normal Operation *

(Lane number in Order)

1 = Reverse lane

CFG20(PCIE/SDVO consurrent)

0 = Only PCIE or SDVO is operational *

1 = PCIE/SDVO are operating simu.

Strap Pin Table

PEGCOMP trace

width and spacing

is 20/25 mils.

CFG[2:0] FSB Freq select

010 = FSB 800MHz

011 = FSB 667MHz

Others = Reserved

0 = DMI x 2

1 = DMI x 4 *

CFG5 (DMI select)

CFG6 Reserved

CFG7 (CPU Strap)

0 = Reserved

1 = Mobile CPU *

CFG8 (Low power PCIE)

0 = Normal mode

1 = Low Power mode *

CFG9

(PCIE Graphics Lane Reversal)

0 = Reverse Lane

1 = Normal Operation *

CFG[11:10] Reserved

CFG[13:12] (XOR/ALLZ)

00 = Reserved

01 = XOR Mode Enabled

10 = All Z Mode Enabled

11 = Normal Operation (Default)*

CFG[15:14] Reserved

CFG16 (FSB Dynamic ODT)

0 = Disable

1 2

C483 SCD1U10V2KX-5GPC483 SCD1U10V2KX-5GP

1 2

C481 SCD1U10V2KX-5GPC481 SCD1U10V2KX-5GP

1 2

C194 SCD1U10V2KX-5GPC194 SCD1U10V2KX-5GP

1 2

C190 SCD1U10V2KX-5GPC190 SCD1U10V2KX-5GP

1 2

C501 SCD1U10V2KX-5GPC501 SCD1U10V2KX-5GP

1 2

C512 SCD1U10V2KX-5GPC512 SCD1U10V2KX-5GP

1 2

C506 SCD1U10V2KX-5GPC506 SCD1U10V2KX-5GP

1 2

C502 SCD1U10V2KX-5GPC502 SCD1U10V2KX-5GP

1 2

C490 SCD1U10V2KX-5GPC490 SCD1U10V2KX-5GP

1 2

C494 SCD1U10V2KX-5GPC494 SCD1U10V2KX-5GP

1 2

R398 24D9R2F-L-GPR398 24D9R2F-L-GP

1 2

C500 SCD1U10V2KX-5GPC500 SCD1U10V2KX-5GP

1 2

C507 SCD1U10V2KX-5GPC507 SCD1U10V2KX-5GP

1 2

C485 SCD1U10V2KX-5GPC485 SCD1U10V2KX-5GP

1 2

C189 SCD1U10V2KX-5GPC189 SCD1U10V2KX-5GP

1 2

C495 SCD1U10V2KX-5GPC495 SCD1U10V2KX-5GP

1 2

C480 SCD1U10V2KX-5GPC480 SCD1U10V2KX-5GP

1 2

C499 SCD1U10V2KX-5GPC499 SCD1U10V2KX-5GP

1 2

C488 SCD1U10V2KX-5GPC488 SCD1U10V2KX-5GP

1 2

C479 SCD1U10V2KX-5GPC479 SCD1U10V2KX-5GP

1 2

C515 SCD1U10V2KX-5GPC515 SCD1U10V2KX-5GP

1 2

C486 SCD1U10V2KX-5GPC486 SCD1U10V2KX-5GP

L_BKLT_CTRL

J40

L_BKLT_EN

H39

L_CTRL_CLK

E39

L_CTRL_DATA

E40

L_DDC_CLK

C37

L_DDC_DATA

D35

L_VDD_EN

K40

LVDS_IBG

L41

LVDS_VBG

L43

LVDS_VREFL

N40

LVDS_VREFH

N41

LVDSA_CLK

C45

LVDSB_CLK#

D44

LVDSA_CLK#

D46

LVDSB_CLK

E42

LVDSB_DATA2

A45

LVDSB_DATA1

A47

LVDSB_DATA#2

B45

LVDSB_DATA#1

B47

LVDSB_DATA0

E44

LVDSA_DATA1

E50

LVDSA_DATA#1

E51

LVDSA_DATA2

F48

LVDSA_DATA#2

F49

LVDSB_DATA#0

G44

LVDSA_DATA0

G50

LVDSA_DATA#0

G51

TVA_DAC

E27

TVA_RTN

F27

TVB_DAC

G27

TVB_RTN

J27

TVC_DAC

K27

TVC_RTN

L27

TV_DCONSEL0

M35

TV_DCONSEL1

P33

CRT_RED#

E29

CRT_VSYNC

E33

CRT_TVO_IREF

C32

CRT_RED

F29

CRT_HSYNC

F33

CRT_BLUE#

G32

CRT_DDC_DATA

G35

CRT_BLUE

H32

CRT_GREEN#

J29

CRT_GREEN

K29

CRT_DDC_CLK

K33

PEG_COMPI

N43

PEG_COMPO

M43

PEG_RX#2

N47

PEG_RX1

L50

PEG_RX#1

L51

PEG_RX2

M47

PEG_RX5

T41

PEG_RX#3

T45

PEG_RX4

T49

PEG_RX#4

T50

PEG_RX#5

U40

PEG_RX3

U44

PEG_RX#7

Y40

PEG_RX#6

Y44

PEG_RX9

Y48

PEG_RX8

AB50

PEG_RX#8

AB51

PEG_RX7

W41

PEG_RX6

W45

PEG_RX#9

W49

PEG_RX11

AC41

PEG_RX10

AC45

PEG_RX#11

AD40

PEG_RX#10

AD44

PEG_RX#15

AG41

PEG_RX15

AG42

PEG_RX#14

AG45

PEG_RX#12

AG46

PEG_RX13

AG49

PEG_RX0

J50

PEG_RX#0

J51

PEG_RX14

AH45

PEG_RX12

AH47

PEG_RX#13

AH49

PEG_TX#6

Y43

PEG_TX#8

W38

PEG_TX#7

W46

PEG_TX#12

AC42

PEG_TX#10

AC46

PEG_TX#11

AC49

PEG_TX#9

AD39

PEG_TX#14

AE49

PEG_TX#13

AH39

PEG_TX#15

AH44

PEG_TX#0

N45

PEG_TX#3

N51

PEG_TX#4

R50

PEG_TX#5

T42

PEG_TX#1

U39

PEG_TX#2

U47

PEG_TX8

Y39

PEG_TX7

Y47

PEG_TX6

W42

PEG_TX9

AC38

PEG_TX11

AC50

PEG_TX12

AD43

PEG_TX10

AD47

PEG_TX14

AE50

PEG_TX13

AG39

PEG_TX15

AH43

PEG_TX3

N50

PEG_TX0

M45

PEG_TX4

R51

PEG_TX1

T38

PEG_TX2

T46

PEG_TX5

U43

3 OF 10

LVDS

TV VGA

PCI_EXPRESS GRAPHICS

U23C

CRESTLINE-GP-U

3 OF 10

LVDS

TV VGA

PCI_EXPRESS GRAPHICS

U23C

CRESTLINE-GP-U

1 2

C487 SCD1U10V2KX-5GPC487 SCD1U10V2KX-5GP

1 2

C195 SCD1U10V2KX-5GPC195 SCD1U10V2KX-5GP

1 2

C484 SCD1U10V2KX-5GPC484 SCD1U10V2KX-5GP

1 2

C492 SCD1U10V2KX-5GPC492 SCD1U10V2KX-5GP

1 2

C482 SCD1U10V2KX-5GPC482 SCD1U10V2KX-5GP

1 2

C197 SCD1U10V2KX-5GPC197 SCD1U10V2KX-5GP

1 2

C196 SCD1U10V2KX-5GPC196 SCD1U10V2KX-5GP

1 2

C192 SCD1U10V2KX-5GPC192 SCD1U10V2KX-5GP

1 2

C491 SCD1U10V2KX-5GPC491 SCD1U10V2KX-5GP

1 2

C489 SCD1U10V2KX-5GPC489 SCD1U10V2KX-5GP

1 2

C191 SCD1U10V2KX-5GPC191 SCD1U10V2KX-5GP