"基于FPGA的等精度频率计设计:8051 IP核应用"

145 浏览量

更新于2024-01-08

收藏 773KB DOC 举报

本论文基于单片机IP核的等精度频率计设计,借助FPGA和8051IP核的优点,旨在克服传统测频原理频率计的局限性,实现较高的测量精度和恒定的测试精度。本论文通过将一些常用但复杂的功能模块设计成可修改参数的IP核,并结合FPGA和8051单片机,实现了一个精确测量频率的等精度频率计。

FPGA是一种可编程逻辑器件,目前广受欢迎。IP核是将一些在数字电路中常用但比较复杂的功能模块设计成可修改参数的模块,以便用户可以直接调用这些模块。随着FPGA规模的不断扩大,使用IP核已成为一种发展趋势。传统测频原理的频率计的测量精度受到被测信号频率的下降而降低,局限性较大。而等精度频率计具有较高的测量精度,并能保持恒定的测试精度,因此被广泛使用。

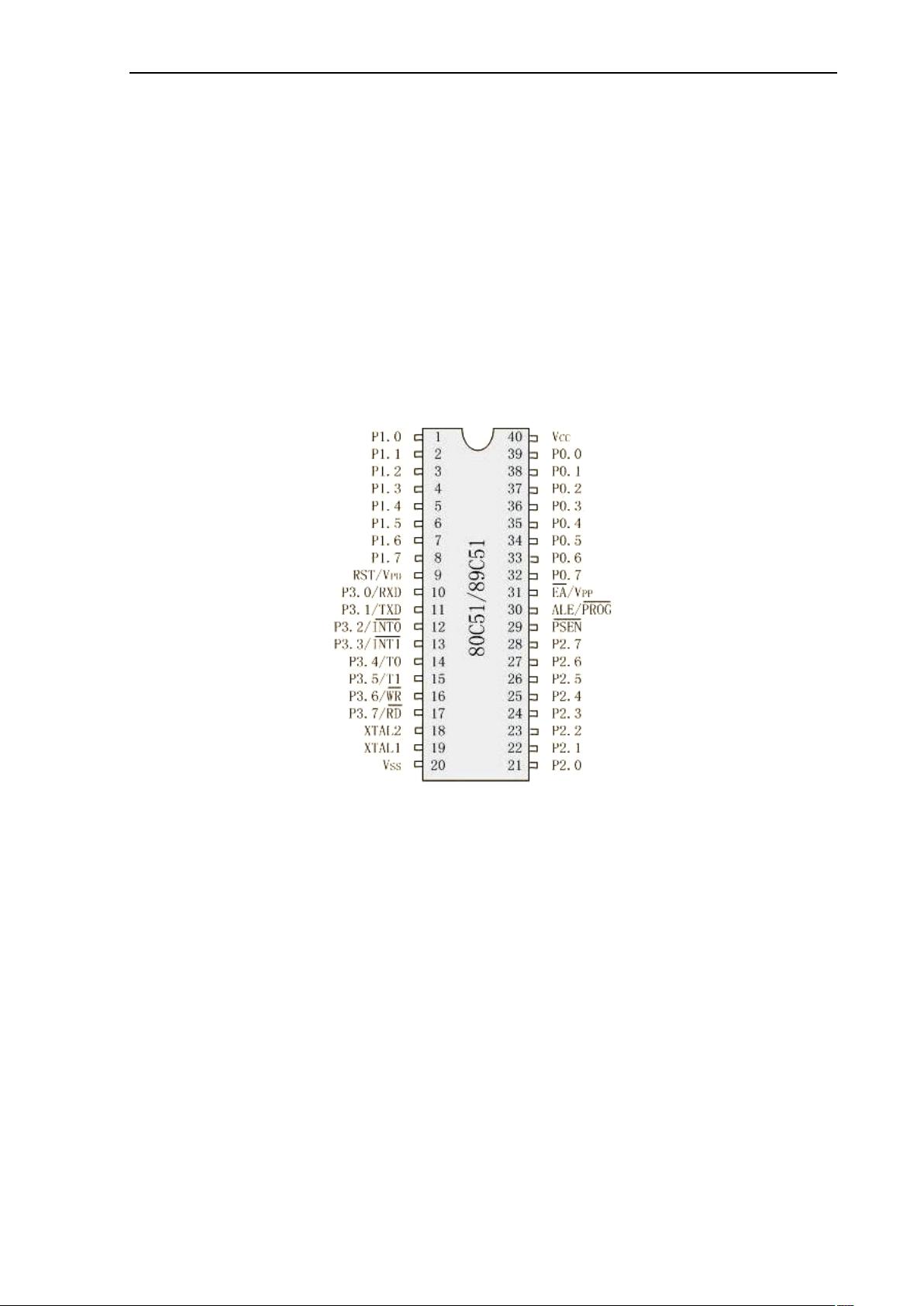

本文针对传统测频原理的局限性,通过利用FPGA和8051单片机的优点设计了一个基于单片机IP核的等精度频率计。该设计结合了FPGA的可编程性和8051IP核的灵活性,可以实现较高的测量精度和恒定的测试精度。在实现过程中,首先将一些常用但复杂的功能模块设计成可修改参数的IP核,然后通过调用这些IP核,实现了等精度频率计的功能。

本文的主要工作包括以下几个方面:首先,通过研究现有的测频原理,分析了传统测频原理的局限性以及等精度频率计的优势。其次,设计了基于单片机IP核的等精度频率计的硬件电路,并对其进行了详细的描述。然后,利用FPGA和8051IP核,实现了硬件电路的功能,并对其进行了验证。最后,对设计的等精度频率计进行了性能测试和实验验证,验证了其测量精度和测试精度都达到了预期的要求。

本文的研究成果具有一定的理论和实际意义。通过设计基于单片机IP核的等精度频率计,使得测量频率的精度得到了较大的提高,有效地突破了传统测频原理的局限性。该等精度频率计具有较高的测量精度和恒定的测试精度,可广泛应用于各种领域的频率测量和调试中。

总之,本论文通过结合FPGA和8051单片机的优点,设计了一个基于单片机IP核的等精度频率计。该等精度频率计具有较高的测量精度和恒定的测试精度,可以有效地克服传统测频原理频率计的局限性。本论文的研究成果对于提高频率测量的精度和测试的可靠性具有重要的理论和实践意义。同时,本文的研究也为基于单片机IP核的相关研究提供了一定的参考和借鉴。

2023-07-01 上传

2023-07-11 上传

2023-07-01 上传

2023-07-01 上传

智慧安全方案

- 粉丝: 3837

- 资源: 59万+