多相滤波FPGA实现的宽带数字下变频器优化策略

PDF格式 | 662KB |

更新于2024-08-29

| 145 浏览量 | 举报

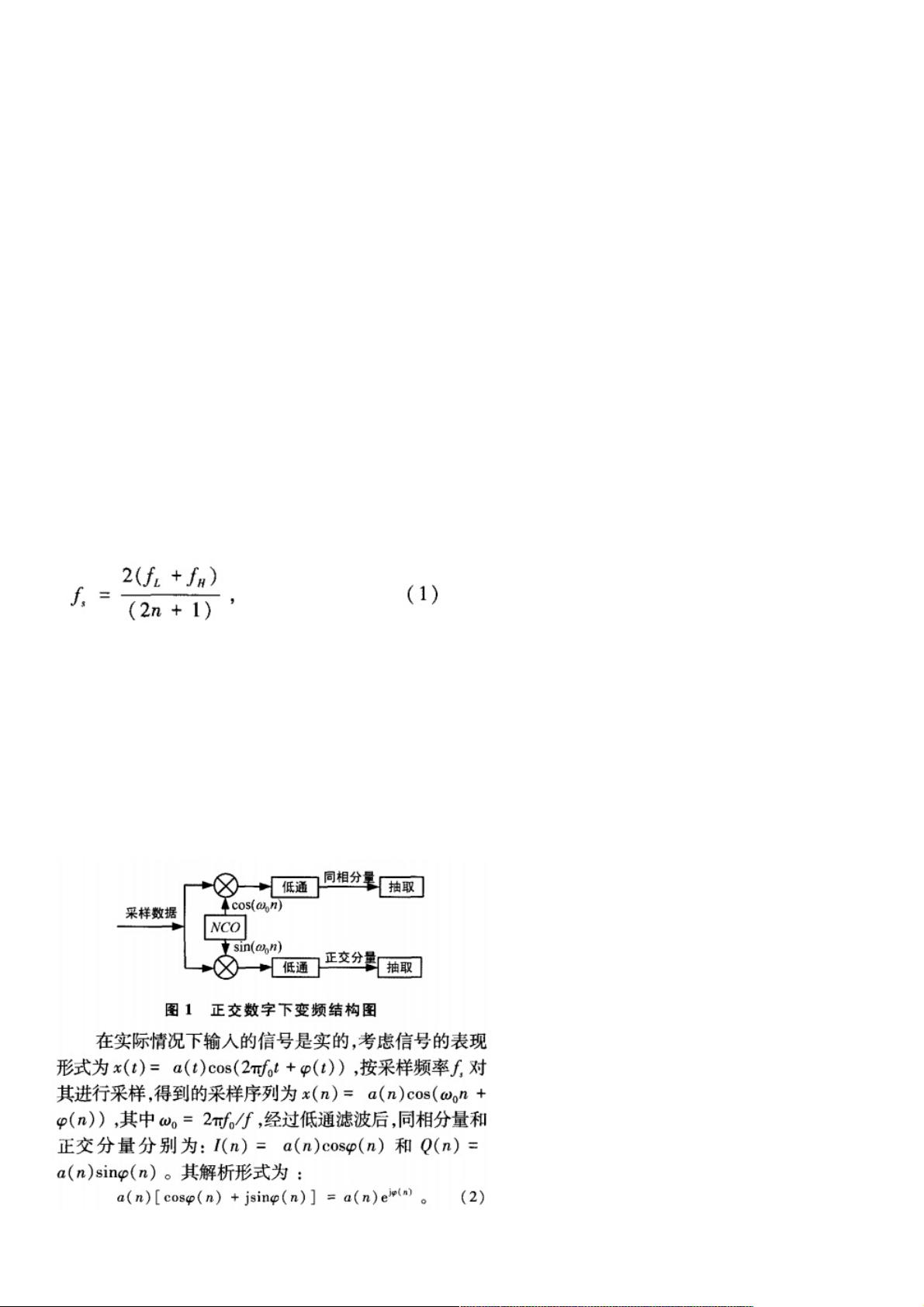

宽带数字下变频器的FPGA实现是现代通信系统中的关键组件,它利用了软件无线电理论的最新进展,特别是在军用和民用通信系统中。数字下变频技术(DDC)作为软件无线电的核心技术,其作用在于将输入的模拟中频信号转换为数字信号,通过改变信号频率到零中频,便于后续的数字信号处理,降低采样速率以适应后端处理单元的需求。

传统的数字信号处理面临着高速采样带来的挑战,尤其是在射频前端的A/D变换过程中,高速采样率对数字信号处理单元和整个系统协调性提出了巨大压力。为解决这一问题,研究者提出了一种创新的解决方案,即基于多相滤波的宽带数字下变频结构。这种结构利用并行处理的优势,通过多相滤波下变频的方式,将数据处理过程分解为多个部分,从而提高实时处理速度,缓解了高速采样与现有DSP器件处理能力之间的不匹配。

多相滤波的实现遵循带通采样定理,该定理指出,对于频率带限信号,只要采样频率fS大于信号带宽B的两倍,就可以确保信号不失真恢复。在实际应用中,为了节省资源,通常采用低于Nyquist采样率的策略,但依然保持足够的信息捕获,这就依赖于高效的滤波技术。

在FPGA设计中,这种基于多相滤波的宽带数字下变频器被成功集成,通过优化的硬件架构,不仅提高了处理效率,还确保了信号质量和系统整体性能。设计人员通过原理分析和实际的FPGA板卡验证,证实了这种方法能够有效地将处理后的数据速率控制在现有DSP器件的处理范围内,满足实际应用需求。

总结来说,宽带数字下变频器的FPGA实现是一种创新的解决方案,它通过并行化和多相滤波技术,解决了高速采样带来的数据处理挑战,为软件无线电通信系统提供了高效、灵活和实时的信号处理能力,对于提升通信系统的整体性能和适应性具有重要意义。

相关推荐

weixin_38689338

- 粉丝: 9

最新资源

- iOS平台内存泄漏问题的调试解决方案

- ASP.NET三层架构选课管理系统实现与实践

- 实用的图书馆管理系统ASP毕业设计项目

- WjXamlPad源码开放——Xaml编辑神器

- TestNG自动化测试框架6.8.5版本发布

- 构建高效的部门与人员组织目录树

- C#编程实现PC喇叭控制发声方法

- 安卓平台完美运行的扫雷游戏评测

- 基于JSP和MySQL的网上成绩录入系统设计与实现

- Linux网络工具源码解析与移植指南

- Android全面图表绘制指南:表格、柱形、圆形、折线

- 武汉大学DSP开发技巧深度解析与关键难点

- xskinexp源代码版本1至2010编译教程

- Java中Json处理常用库的介绍

- Eclipse Juno SR2汉化包下载:助力Java新手入门

- iOS日期时间选择器控件使用与自定义实现