PCI总线协议详解:信号定义与接口控制

需积分: 0 19 浏览量

更新于2024-08-05

收藏 777KB PDF 举报

"PCI总线标准协议概述"

PCI(Peripheral Component Interconnect)总线是一种广泛应用于个人计算机中的局部总线标准,它允许不同设备如显卡、声卡、网卡等与主板进行高速数据交换。PCI总线协议规定了一系列信号线,以确保设备间通信的高效和准确。

1. 系统引线:

- CLKin:时钟输入,是PCI总线上的所有设备同步的基础,频率范围为0Hz(DC)到66MHz,是PCI工作频率。

- RST#:复位信号,用于初始化PCI设备,将特性寄存器和定时器重置为默认状态,所有输出信号在复位期间变为三态。

2. 地址和数据引线:

- AD0~AD31t/s:这些是双向三态信号,用于传输地址和数据。在地址周期中,它们传输地址信息;在数据周期,当C/BE#[n](数据选择/字节使能)有效时,它们传输数据。

3. 接口控制信号:

- C/BE#[n]:数据选择/字节使能,指示哪些数据线上的数据有效,用于数据宽度的选择。

- DEVSEL#:设备选择信号,表明当前选定的目标设备。

- TRDY#(Target Ready):目标设备准备好的信号,表明目标设备已准备好接收或发送数据。

- PAR:奇偶校验信号,用于检测数据传输中的错误。

- ERR#(Error):错误报告信号,用于指示总线上的错误情况。

- IRDY#( Initiator Ready):发起设备准备好信号,表明主设备可以发送或接收数据。

- STB#(Strobe):锁存使能,由主设备发出,表明数据线上的数据是有效的。

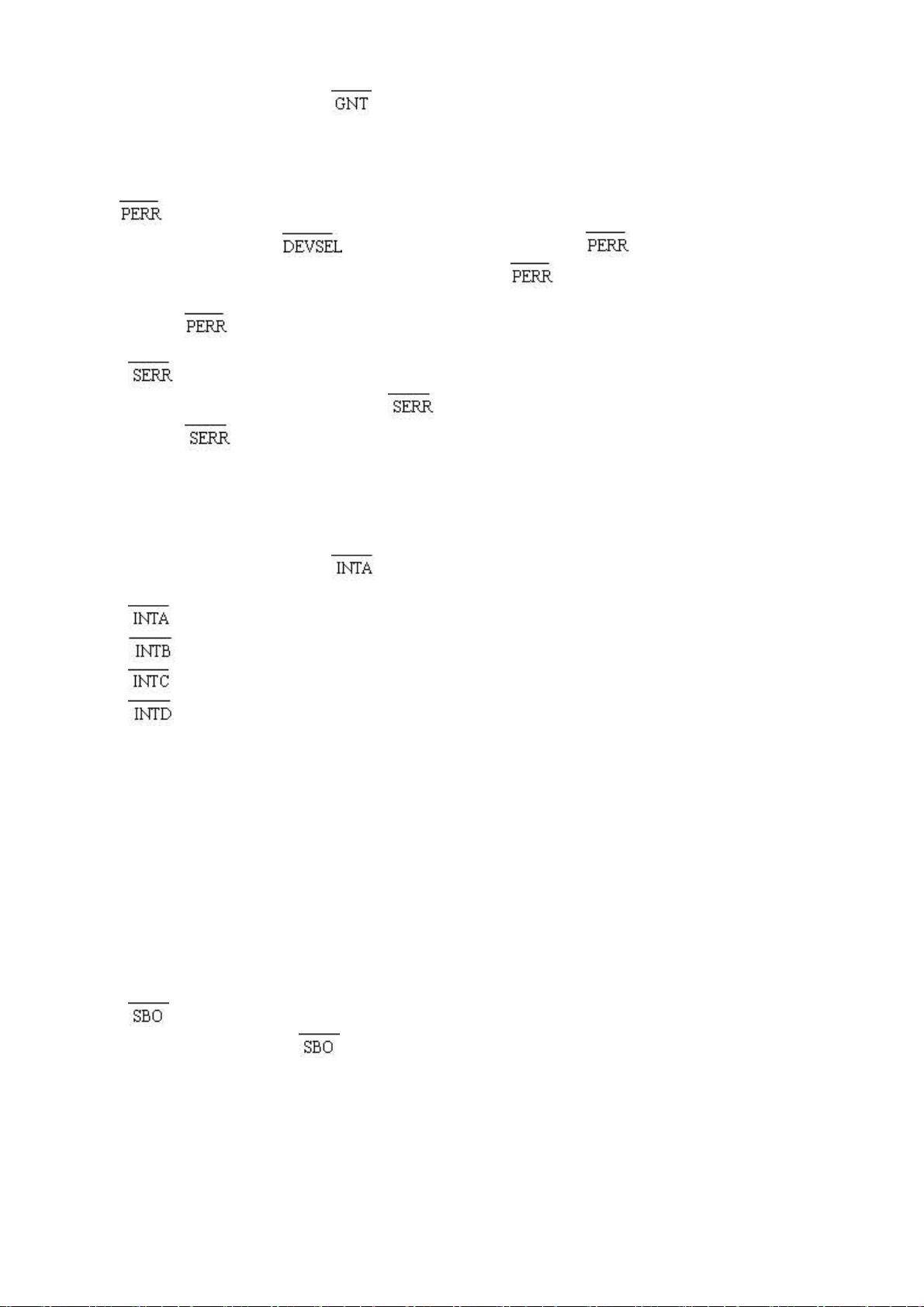

4. 仲裁信号:

- REQ#(Request):主设备请求总线使用权。

- GNT#(Grant):总线使用权授予信号,由仲裁器给出,允许主设备使用总线。

- ATRN#(Attention):仲裁请求,用于在主设备之间进行总线使用权的仲裁。

5. 错误报告信号:

- SERR#(System Error):系统错误信号,用于报告非致命错误。

- PERR#(Parity Error):奇偶校验错误信号,用于报告致命的总线错误。

6. 中断信号:

- INT[A-D]:中断请求线,设备通过这些线向主设备发送中断请求。

7. 高速缓存支持信号:

- CACHES#:高速缓存使能,允许主设备和从设备使用高速缓存进行数据交换。

PCI总线信号线分为必需和可选两种,主设备和目标设备的引脚数有所不同,以满足不同的功能需求。例如,持续三态信号(s/t/s)的管理确保了多个主设备之间的协调,避免信号冲突。漏极开路信号(o/d)则允许多个设备共享同一线路,实现线或操作。

PCI总线协议通过精细设计的信号线和控制机制,保证了系统中不同组件间的高效、可靠通信,同时支持多种类型的设备共存,是现代计算机体系结构中的重要组成部分。

354 浏览量

2022-01-23 上传

2014-01-24 上传

2013-01-02 上传

2022-01-23 上传

2012-02-10 上传

2023-12-22 上传

2010-05-11 上传

2011-09-24 上传

chenbtravel

- 粉丝: 29

- 资源: 296

最新资源

- SSM Java项目:StudentInfo 数据管理与可视化分析

- pyedgar:Python库简化EDGAR数据交互与文档下载

- Node.js环境下wfdb文件解码与实时数据处理

- phpcms v2.2企业级网站管理系统发布

- 美团饿了么优惠券推广工具-uniapp源码

- 基于红外传感器的会议室实时占用率测量系统

- DenseNet-201预训练模型:图像分类的深度学习工具箱

- Java实现和弦移调工具:Transposer-java

- phpMyFAQ 2.5.1 Beta多国语言版:技术项目源码共享平台

- Python自动化源码实现便捷自动下单功能

- Android天气预报应用:查看多城市详细天气信息

- PHPTML类:简化HTML页面创建的PHP开源工具

- Biovec在蛋白质分析中的应用:预测、结构和可视化

- EfficientNet-b0深度学习工具箱模型在MATLAB中的应用

- 2024年河北省技能大赛数字化设计开发样题解析

- 笔记本USB加湿器:便携式设计解决方案

已收录资源合集

已收录资源合集