Verilog行为仿真与ModelSim应用指南

需积分: 9 13 浏览量

更新于2024-07-31

收藏 1.87MB PPT 举报

"该资源包含了关于EDA技术的详细讲解,特别是使用VHDL语言的方面。文件以科学出版社的PDF/PPT形式呈现,涵盖了Verilog行为仿真的具体步骤以及Verilog中的系统任务和预编译语句。"

在电子设计自动化(EDA)领域,VHDL是一种广泛使用的硬件描述语言,用于设计和验证数字系统。本资料深入探讨了使用Verilog进行行为仿真的过程,这对于理解和调试复杂的数字电路设计至关重要。行为仿真允许工程师在实际硬件制造之前预测和分析设计的功能。

10.1 Verilog行为仿真流程:

行为仿真主要分为以下几个步骤:

1. 启动仿真工具,如ModelSim。

2. 创建仿真工程项目,这是组织设计文件和测试平台的基础。

3. 编译仿真文件,将VHDL代码转化为可执行的仿真模型。

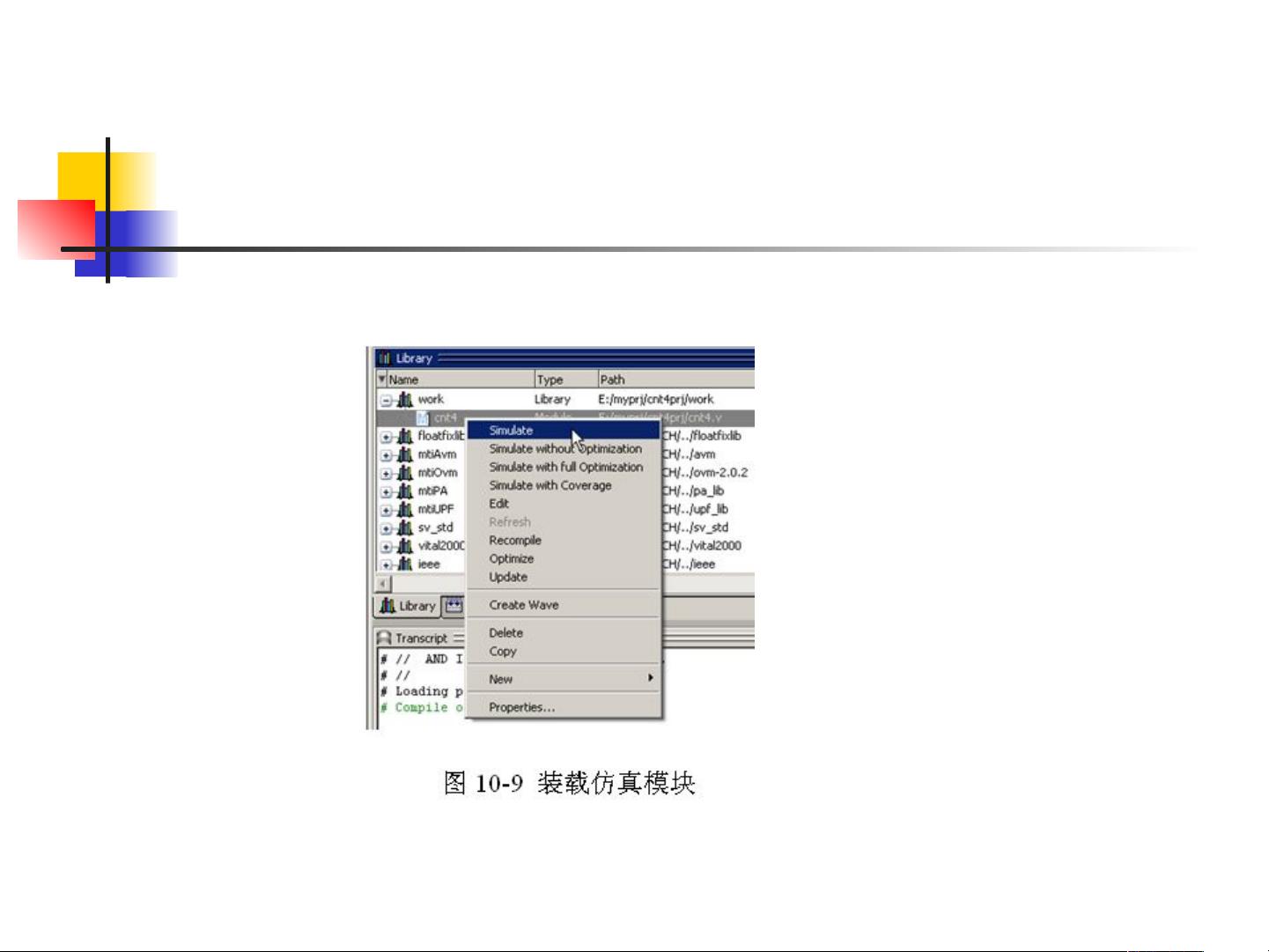

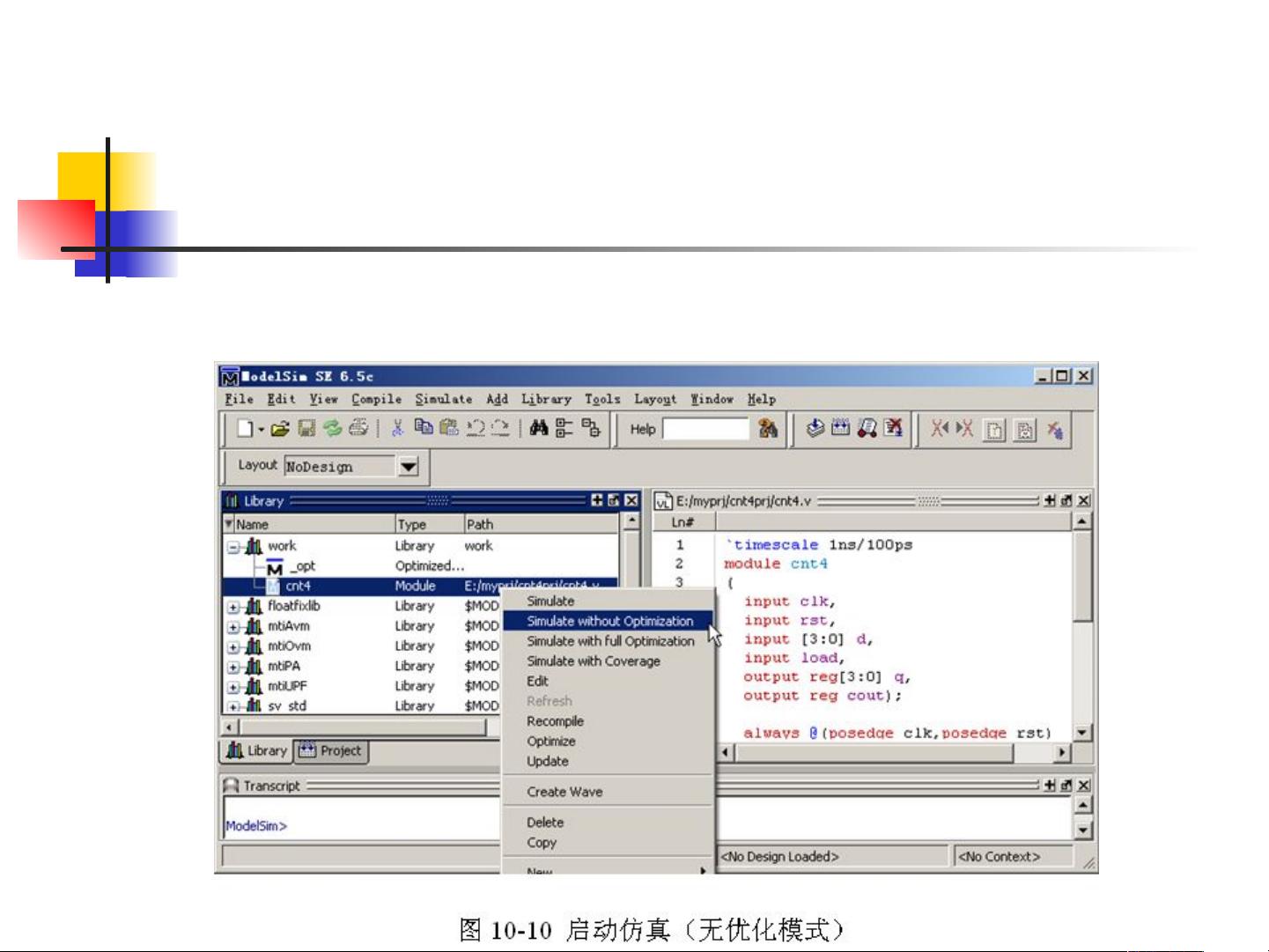

4. 装载仿真模块和仿真库,确保所有必要的设计单元都已准备就绪。

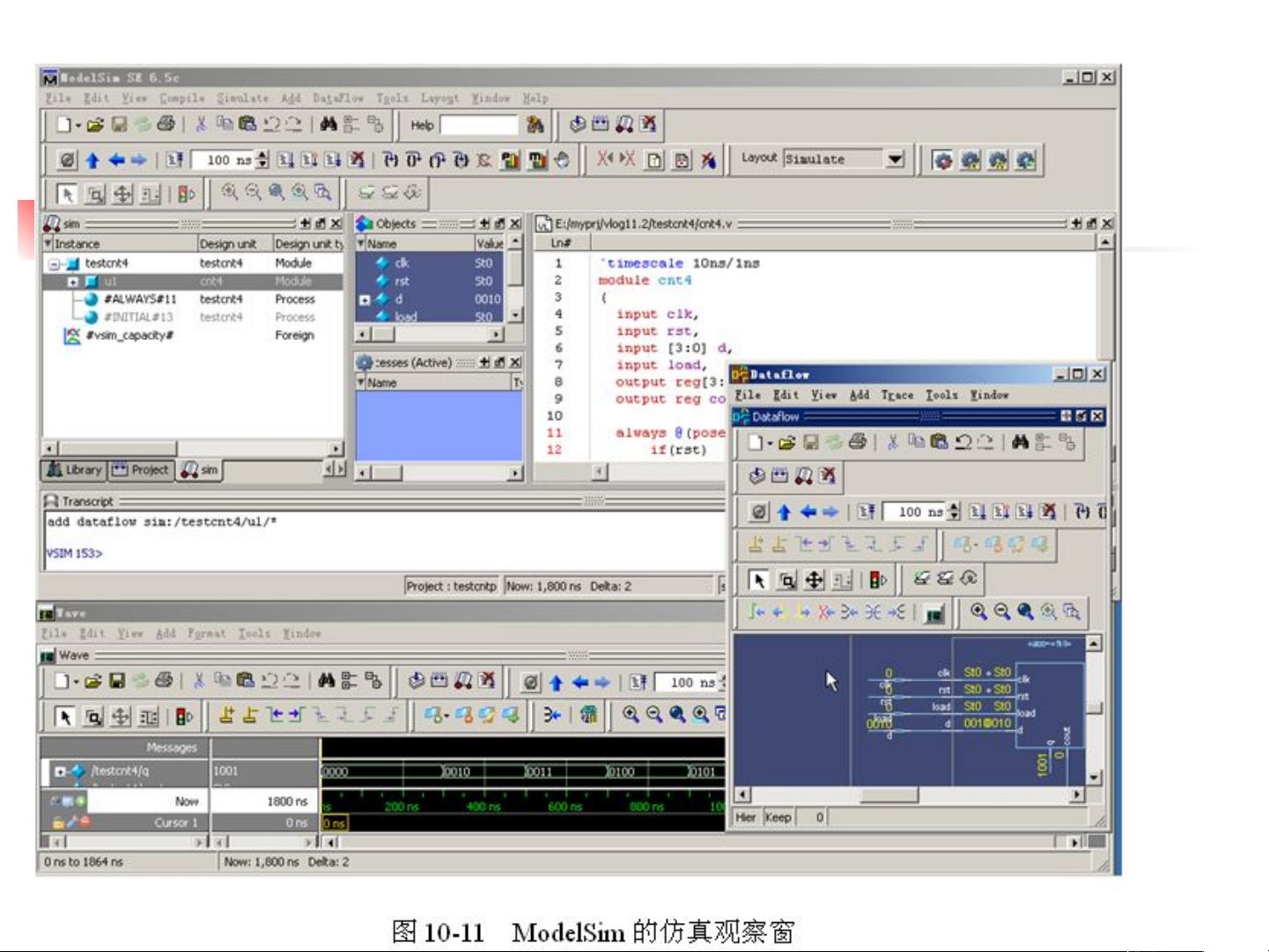

5. 执行仿真,运行设计并观察结果,以验证设计的正确性。

10.2 ModelSim应用向导:

ModelSim是一款强大的VHDL和Verilog仿真器,它提供了直观的用户界面和强大的仿真功能。使用ModelSim进行仿真,用户需要按照上述步骤操作,确保每个阶段都顺利完成,以达到有效的仿真效果。

10.3 Verilog系统任务和预编译语句:

系统任务和预编译语句是Verilog中的重要组成部分,它们在仿真过程中起到了关键作用:

1. `$display`:用于在终端打印变量或表达式的值,帮助调试。

2. `$write`:类似`$display`,但可以控制输出格式。

3. `$strobe`和`$monitor`:周期性地输出信号状态,便于观察信号变化。

4. `$finish`和`$stop`:结束仿真,`$finish`通常在设计完成时调用,`$stop`则用于临时停止仿真。

5. `$time`:返回当前仿真时间,用于时间相关的计算和显示。

6. 文件操作:包括读写文件,用于记录仿真数据或与其他工具交换信息。

7. ``define`宏定义:创建用户自定义的文本替换,简化代码。

8. ``include`文件包含:将一个文件的内容插入到另一个文件中,便于代码复用。

9. `translate_on`与`translate_off`:控制预处理阶段的代码处理,例如忽略某些代码段。

10.4 基本元件与用户自定义元件(UDP):

这部分内容可能涉及Verilog中基本逻辑门的使用,以及如何定义和使用用户自定义的并行元件,以实现更复杂的逻辑功能。UDP是提高设计效率和重用性的重要手段。

通过学习这些内容,工程师可以更有效地利用EDA工具,如ModelSim,进行Verilog设计的验证和调试,确保硬件设计在实际实现前满足预期功能。这份资料对于想要深入理解VHDL和Verilog行为仿真以及EDA技术的读者来说,是一份宝贵的资源。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2024-12-21 上传

2024-12-21 上传

2024-12-21 上传

2024-12-21 上传

qingpendayuWXY

- 粉丝: 0

- 资源: 23

最新资源

- JavaScript实现的高效pomodoro时钟教程

- CMake 3.25.3版本发布:程序员必备构建工具

- 直流无刷电机控制技术项目源码集合

- Ak Kamal电子安全客户端加载器-CRX插件介绍

- 揭露流氓软件:月息背后的秘密

- 京东自动抢购茅台脚本指南:如何设置eid与fp参数

- 动态格式化Matlab轴刻度标签 - ticklabelformat实用教程

- DSTUHack2021后端接口与Go语言实现解析

- CMake 3.25.2版本Linux软件包发布

- Node.js网络数据抓取技术深入解析

- QRSorteios-crx扩展:优化税务文件扫描流程

- 掌握JavaScript中的算法技巧

- Rails+React打造MF员工租房解决方案

- Utsanjan:自学成才的UI/UX设计师与技术博客作者

- CMake 3.25.2版本发布,支持Windows x86_64架构

- AR_RENTAL平台:HTML技术在增强现实领域的应用