FPGA时序设计揭秘:数字电路开发实战

需积分: 33 89 浏览量

更新于2024-07-29

收藏 929KB PDF 举报

“FPGA设计经验谈是一本针对工程师的书籍,着重分享了在FPGA/CPLD数字电路设计中的实战经验和技巧,强调了时序设计的重要性,并提到了建立时间、保持时间的概念,以及如何处理竞争和冒险现象。”

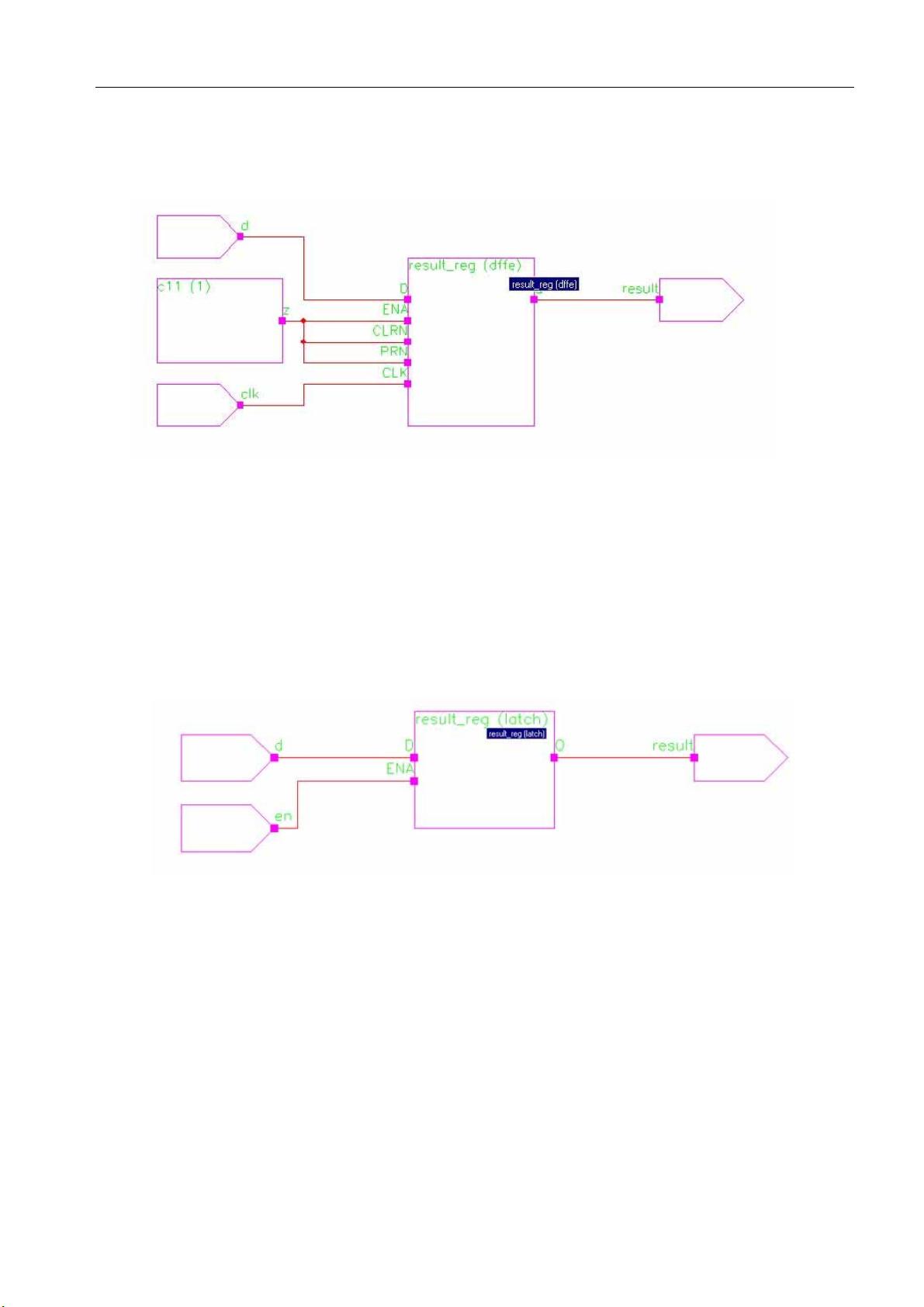

在FPGA(现场可编程门阵列)和CPLD(复杂可编程逻辑器件)的数字电路设计中,时序设计是确保系统性能和稳定性的重要环节。建立时间和保持时间是时序设计的核心概念。建立时间(setuptime)规定了在时钟上升沿到来前数据必须稳定不变的时间,确保数据能够正确地被触发器捕获。若建立时间不足,可能会导致数据丢失。保持时间(holdtime)则是在时钟上升沿之后数据需保持稳定的时间,以避免数据在触发器内部发生错误变化。这两个参数是确保数字系统正确工作的关键,尤其是在高速设计中。

时序设计还涉及到时钟树的偏斜问题,即时钟信号从源头到各个触发器的延迟差异。在设计中,应考虑到最大延迟用于检查建立时间,最小延迟用于检查保持时间。建立时间与时钟周期直接相关,可以通过降低时钟频率来缓解建立时间的问题。然而,保持时间与时钟周期无关,一旦设计不合理,即使改变时钟频率也无法解决问题,可能需要对整个设计进行大规模调整,这对设计效率影响显著。

FPGA中的竞争和冒险现象是另一个需要关注的问题。当多个信号同时变化时,由于路径延迟和信号转换时间,可能会导致组合逻辑输出的瞬时不稳定,出现尖峰或毛刺。这种现象可能导致逻辑错误,需要通过添加适当的同步器、优化布线或者调整逻辑结构来消除。

在进行FPGA设计时,合理利用设计工具的自动计算功能,如计算输入之间的建立和保持时间,可以有效地预防这些问题。同时,理解并掌握时序分析和优化技术,如静态时序分析(Static Timing Analysis, STA),是提高设计质量和效率的关键。此外,良好的代码风格和设计习惯,比如避免深度扇出和使用适当的时钟分频,也能帮助优化时序性能。

FPGA设计不仅要求工程师具备扎实的数字电路基础,还需要熟悉时序分析、竞争冒险的处理以及利用设计工具的能力。《FPGA设计经验谈》这本书提供了一手的实践经验,对于希望深入理解和提升FPGA设计技能的工程师来说,是一份宝贵的参考资料。

huolipaopao

- 粉丝: 1

- 资源: 5

最新资源

- 酒店大堂装饰模型设计

- delivery-upptime:Math Mathieu Leplatre的正常运行时间监控器和状态页面,由@upptime提供支持

- ComputationalPhysics2019

- 神领物流 微服务项目实战-课程学习

- 非光学太阳能跟踪器(东塔2.4KW)-项目开发

- SpinConv:从旋转表示类型转换为另一种-matlab开发

- 现代简约沙发模型设计

- 临时岗位津贴申请单excel模版下载

- Calculadora

- Benchworks

- redis-lesson:我的laravel教程“带有Socket.io的实时Laravel”版本

- 圣诞节的漂亮小程序圣诞节漂亮的小程序

- trab_calc_num_ufsc:TrabalhoPrático1 deCálculoNúmerico

- 绿色田园家居模型

- 1D、2D 或 3D 中的拉普拉斯算子:具有精确特征对的矩形网格上的稀疏 (1-3)D 拉普拉斯算子。-matlab开发

- 正常运行时间:Jul Julien Jourdain的正常运行时间监控和状态页面,由@upptime提供支持