Xilinx ISE 10.1快速入门与Verilog模块创建教程

需积分: 50 123 浏览量

更新于2024-07-26

收藏 727KB DOC 举报

本文档详细介绍了如何使用Xilinx ISE 10.1进行FPGA设计流程,包括创建新项目、添加Verilog源文件、编写并运行行为仿真。以下是关键步骤的详细说明:

1. **新项目创建**:

- 打开Xilinx ISE 10.1工程管理器(Project Navigator),通常通过双击桌面上的快捷方式实现。

- 在Project Navigator中,选择"File" -> "New Project",输入工程名称和存放位置,避免使用中文字符以防止潜在的兼容性问题。

2. **器件设置**:

- 设定器件特性,根据目标FPGA开发板型号(例如Virtex-2P系列中的XC2VP30,采用ff896封装,-7速度等级),在新建工程对话框中进行配置。完成这些设置后,点击"Next"直至完成工程的初始配置。

3. **添加源文件**:

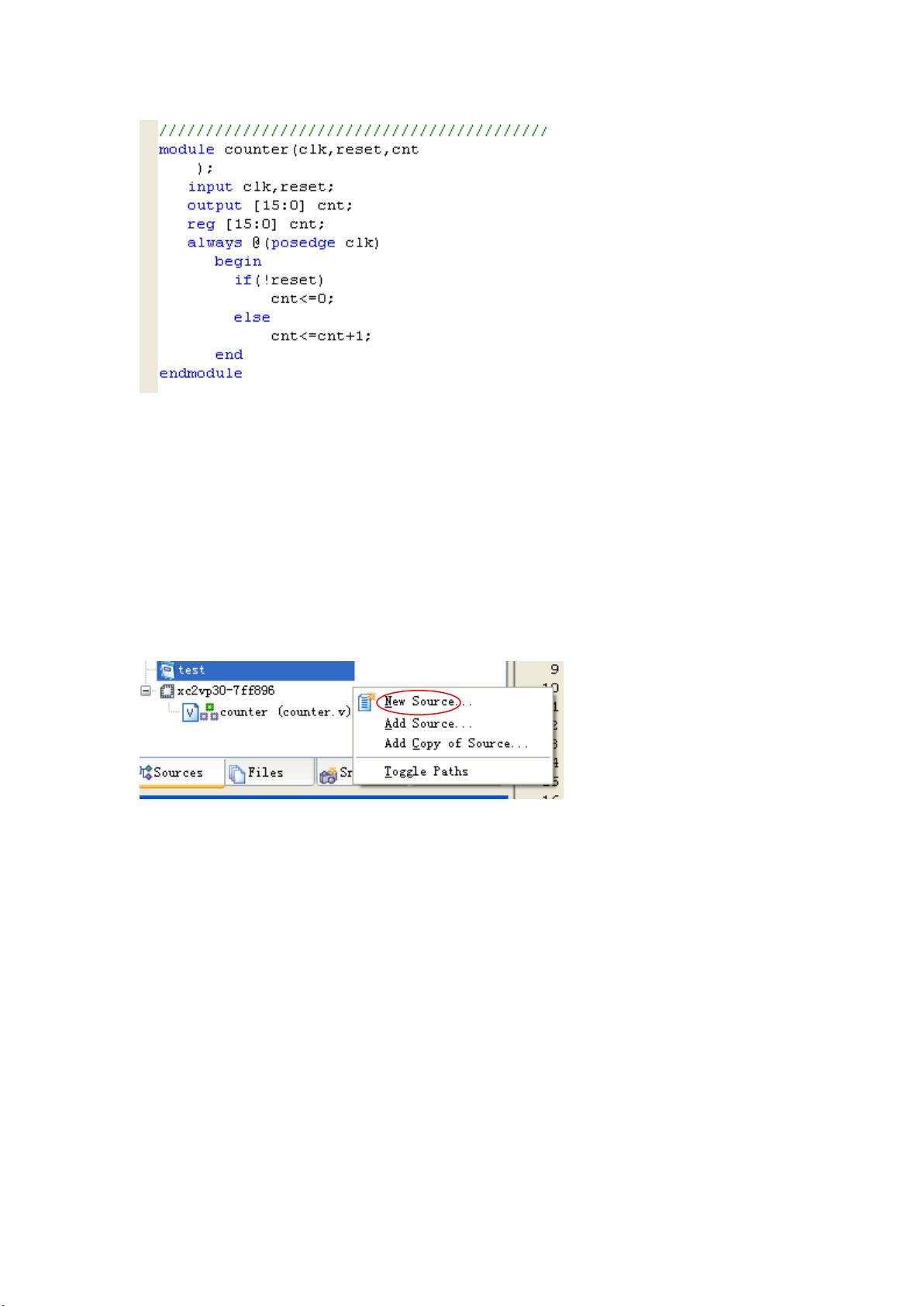

- 在Source for目录下创建新源文件:右键单击并选择"New Source" -> "Verilog Module",输入模块名称,可选择是否自定义输入/输出端口,一般建议默认。

4. **编写源代码**:

- 打开编写Verilog代码的.v文件(如counter.v),在源代码编辑框中编写设计逻辑,保存代码。

5. **行为仿真**:

- 在Source窗口,右键单击空白处,选择"New Source" -> "TestBench WaveForm",创建测试脚本。

- 选择对应的源文件作为测试对象,确保测试脚本能覆盖设计的所有功能。

- 配置时钟参数,如果涉及组合逻辑,记得选择"combinatorial"选项。

- 设置激励波形,确保波形能够验证电路的功能,例如,输入信号和期望的输出响应。

6. **功能仿真**:

- 双击".tbw"文件,启动仿真器,进入processes窗口,选择"simulator behavioral model"进行功能仿真。

- 观察仿真结果,评估设计的正确性和性能,必要时进行调试。

通过以上步骤,您可以利用ISE 10.1工具进行FPGA项目的完整流程,从设计到验证,以确保电路的正确实现。每个步骤都是设计过程中不可或缺的一部分,理解和熟练掌握它们对于成功进行FPGA设计至关重要。

1192 浏览量

297 浏览量

点击了解资源详情

2024-11-02 上传

2024-11-02 上传

2024-10-31 上传

2024-11-02 上传

2024-10-31 上传

2022-06-20 上传

songqisheng

- 粉丝: 0

- 资源: 1