没有合适的资源?快使用搜索试试~ 我知道了~

首页2015年Altera Quartus II Volume1:设计与综合指南

"《Quartus II Handbook Volume 1:设计与综合》是一份重要的Altera芯片设计指南,针对的是2015年的系列手册第一部。该手册详细介绍了Quartus II软件如何组织和管理设计项目,包括设计层次结构、库、约束以及项目设置。用户可以通过点击'File > New Project Wizard'快速创建新项目并设定基础配置。 在Quartus II项目中,统一的GUI界面整合了项目信息,如项目导航器允许查看和编辑设计元素,而消息窗口则列出关于项目处理的重要通知。该软件支持多版本项目保存,以便设计师能够尝试不同的设置来达成设计目标。此外,Quartus II项目还支持团队协作和分布式工作流程,以及脚本编程接口,这使得设计过程更加灵活高效。 新项目 wizard 提供了一个快速入门途径,用户可以使用它来创建项目并设定基本参数,这是通过版权Altera Corporation于2015年发布的功能。该手册涵盖的内容包括但不限于ARRIA、CYCLON等Altera芯片的特定设计流程,适用于硬件工程师进行高级逻辑设计、硬件描述语言(HDL)编写、时序分析以及综合等各个环节。理解并熟练运用这些工具和方法对于Altera芯片的设计者来说至关重要,它有助于提升设计效率,确保最终产品满足性能和功能需求。"

资源详情

资源推荐

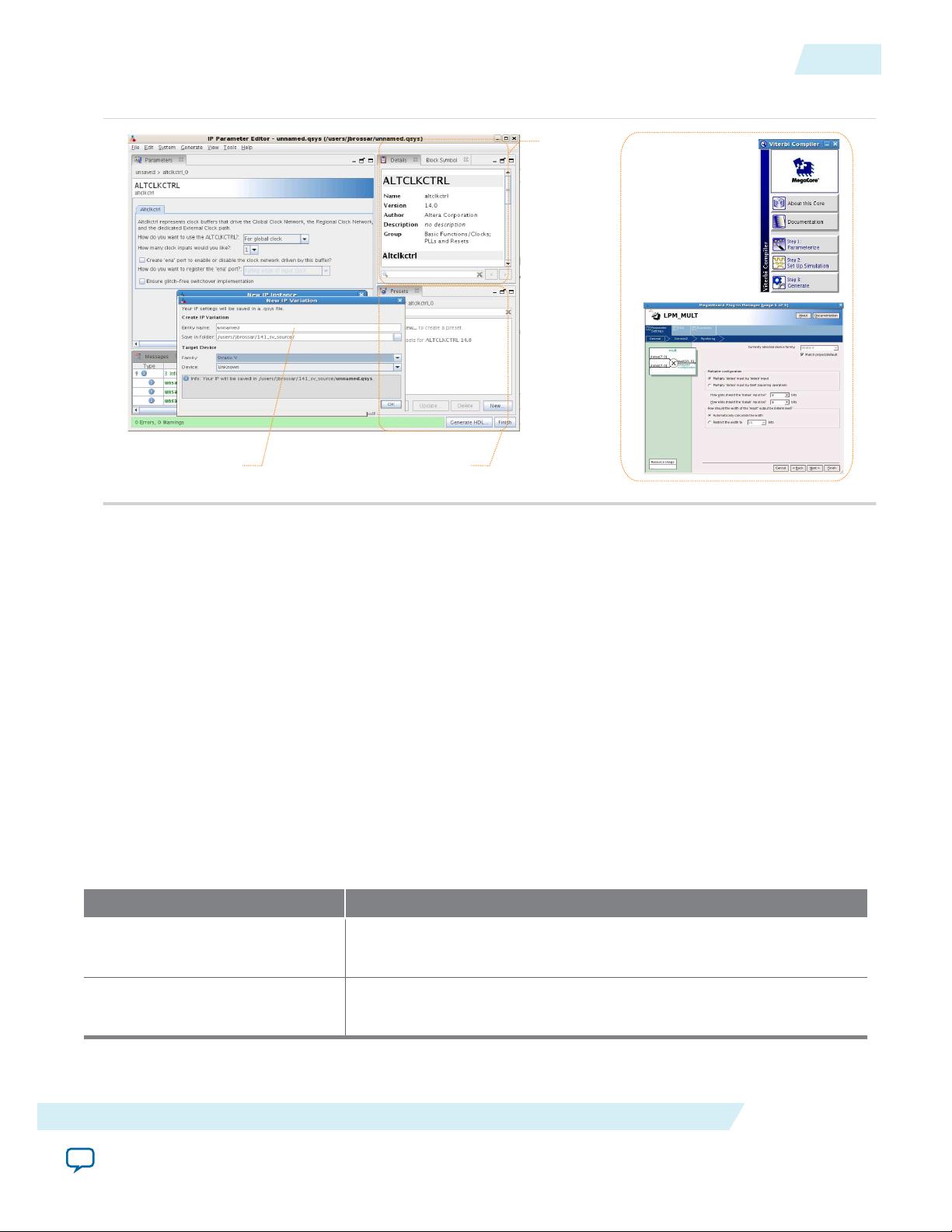

Figure 1-13: IP Parameter Editors

View IP port

and parameter

details

Apply preset parameters for

specific applications

Specify your IP variation

name and target device

Legacy parameter

editors

Adding IP Cores to IP Catalog

The IP Catalog automatically displays Altera IP cores found in the project directory, in the Altera

installation directory, and in the defined IP search path. The IP Catalog can include Altera-provided IP

components, third-party IP components, custom IP components that you provide, and previously

generated Qsys systems.

You can use the IP Search Path option (Tools > Options) to include custom and third-party IP

components in the IP Catalog. The IP Catalog displays all IP cores in the IP search path. The Quartus II

software searches the directories listed in the IP search path for the following IP core files:

• Component Description File (_hw.tcl)—Defines a single IP core.

• IP Index File (.ipx)—Each .ipx file indexes a collection of available IP cores, or a reference to other

directories to search. In general, .ipx files facilitate faster searches.

The Quartus II software searches some directories recursively and other directories only to a specific

depth. When the search is recursive, the search stops at any directory that contains an _hw.tcl or .ipx file.

In the following list of search locations, a recursive descent is annotated by **. A single * signifies any file.

Table 1-2: IP Search Locations

Location Description

PROJECT_DIR/*

Finds IP components and index files in the Quartus II project

directory.

PROJECT_DIR/ip/**/*

Finds IP components and index files in any subdirectory of the /ip

subdirectory of the Quartus II project directory.

QII5V1

2015.05.04

Adding IP Cores to IP Catalog

1-15

Managing Quartus II Projects

Altera Corporation

Send Feedback

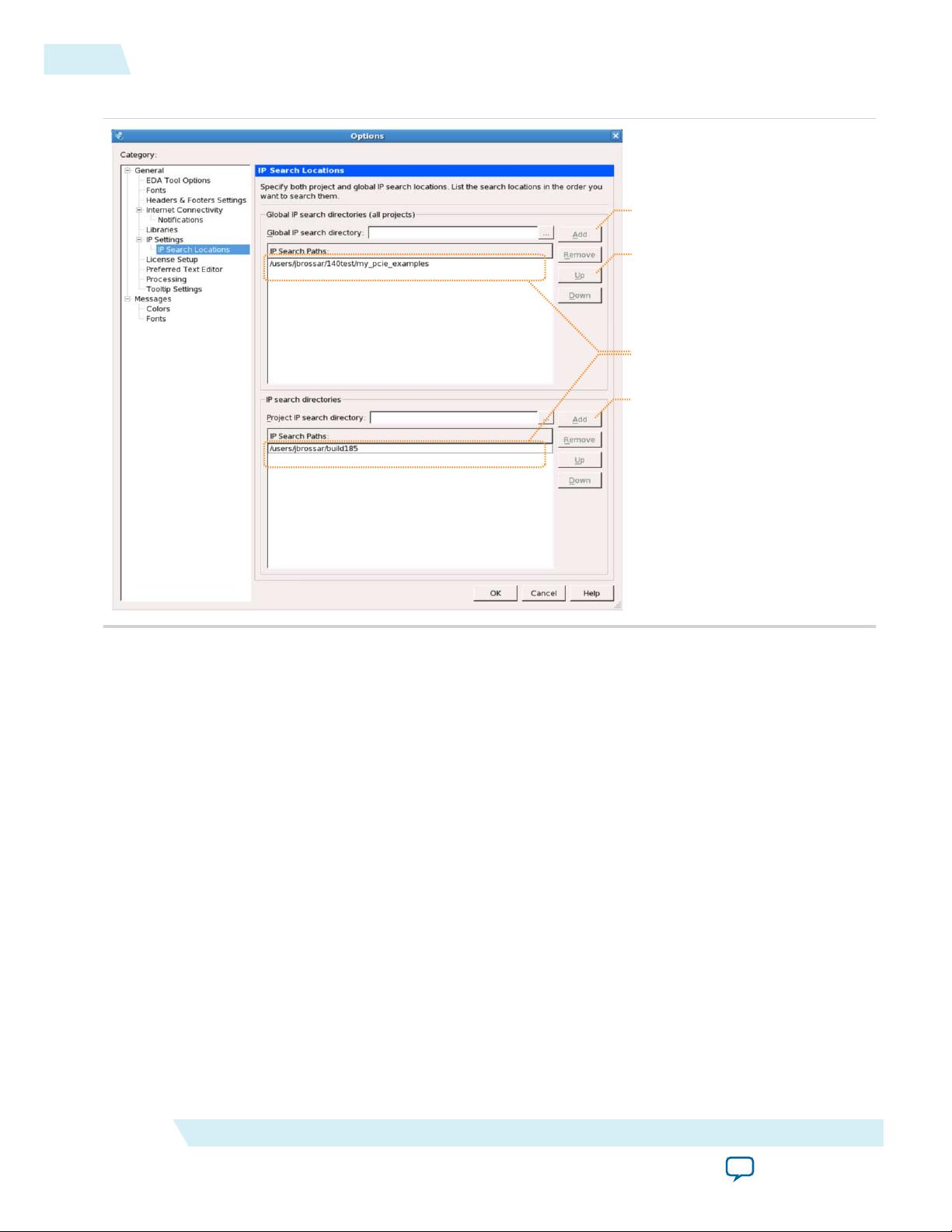

Figure 1-14: Specifying IP Search Locations

Adds new global IP search paths

Changes search path order

Adds new project-specific IP search paths

Lists current project and global search paths

If the Quartus II software recognizes two IP cores with the same name, the following search path

precedence rules determine the resolution of files:

1. Project directory.

2. Project database directory.

3. Project IP search path specified in IP Search Locations, or with the SEARCH_PATH assignment in the

Quartus II Settings File (.qsf) for the current project revision.

4. Global IP search path specified in IP Search Locations, or with the SEARCH_PATH assignment in the

quartus2.ini file.

5. Quartus software libraries directory, such as <Quartus Installation>\libraries.

Note:

If you add a component to the search path, you must refresh your system by clicking File > Refresh

to update the IP Catalog.

General Settings for IP

You can use the following settings to control how the Quartus II software manages IP cores in your

project.

1-16

General Settings for IP

QII5V1

2015.05.04

Altera Corporation

Managing Quartus II Projects

Send Feedback

Table 1-3: IP Core General Setting Locations

Setting Location Description

Tools > Options > IP

Settings

Or

Assignments > Settings >

IP Settings (only enabled

with open project)

• Specify your IP generation HDL preference. The parameter editor

generates IP files in your preferred HDL by default.

• Increase Maximum Qsys memory usage size if you experience slow

processing for large systems, or if Qsys reports an Out of Memory error.

• Specify whether to Automatically add Quartus II IP files to all projects.

Disable this option to control addition of IP files manually. You may

want to experiment with IP before adding to a project.

• Use the IP Regeneration Policy setting to control when synthesis files

are regenerated for each IP variation. Typically you Always regenerate

synthesis files for IP cores after making changes to an IP variation.

Tools > Options > IP

Catalog Search Locations

Or

Assignments > Settings >

IP Catalog Search

Locations

• Specify project and global IP search locations. The Quartus II software

searches for IP cores in the project directory, in the Altera installation

directory, and in the IP search path.

Assignments > Settings >

Simulation

• NativeLink Settings allow you to automatically compile testbenches for

supported simulators. You can also specify a script to compile the

testbench, and a script to set up the simulation.

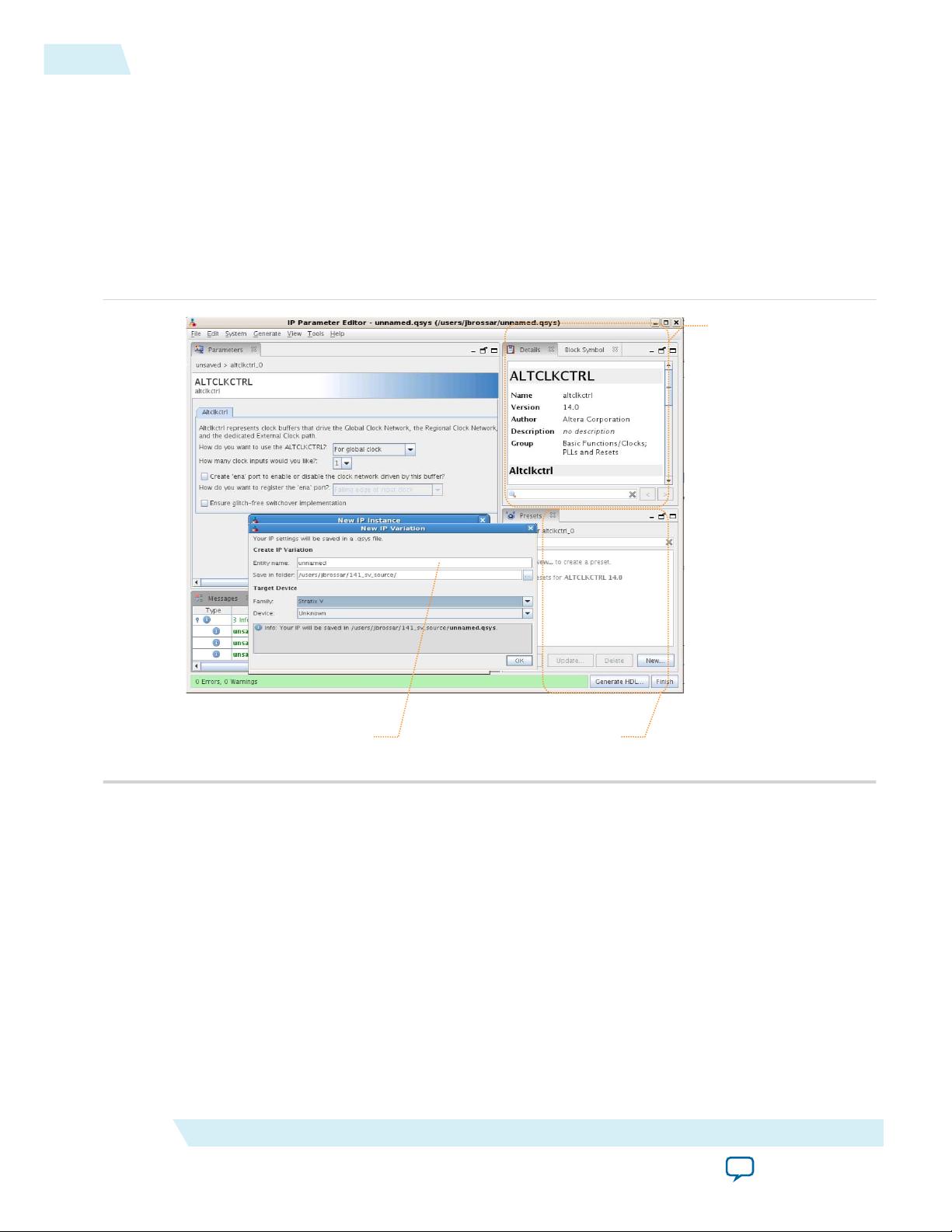

Specifying IP Core Parameters and Options

You can quickly configure a custom IP variation in the parameter editor. Use the following steps to

specify IP core options and parameters in the parameter editor. Refer to Specifying IP Core Parameters

and Options (Legacy Parameter Editors) for configuration of IP cores using the legacy parameter editor.

1. In the IP Catalog (Tools > IP Catalog), locate and double-click the name of the IP core to customize.

The parameter editor appears.

2. Specify a top-level name for your custom IP variation. The parameter editor saves the IP variation

settings in a file named <your_ip>.qsys. Click OK.

3. Specify the parameters and options for your IP variation in the parameter editor, including one or

more of the following. Refer to your IP core user guide for information about specific IP core

parameters.

• Optionally select preset parameter values if provided for your IP core. Presets specify initial

parameter values for specific applications.

• Specify parameters defining the IP core functionality, port configurations, and device-specific

features.

• Specify options for processing the IP core files in other EDA tools.

4. Click Generate HDL, the Generation dialog box appears.

5. Specify output file generation options, and then click Generate. The IP variation files generate

according to your specifications.

QII5V1

2015.05.04

Specifying IP Core Parameters and Options

1-17

Managing Quartus II Projects

Altera Corporation

Send Feedback

6. To generate a simulation testbench, click Generate > Generate Testbench System.

7. To generate an HDL instantiation template that you can copy and paste into your text editor, click

Generate > HDL Example.

8. Click Finish. The parameter editor adds the top-level .qsys file to the current project automatically. If

you are prompted to manually add the .qsys file to the project, click Project > Add/Remove Files in

Project to add the file.

9. After generating and instantiating your IP variation, make appropriate pin assignments to connect

ports.

Figure 1-15: IP Parameter Editor

View IP port

and parameter

details

Apply preset parameters for

specific applications

Specify your IP variation name

and target device

Files Generated for Altera IP Cores

The Quartus II software generates the following IP core output file structure:

1-18

Files Generated for Altera IP Cores

QII5V1

2015.05.04

Altera Corporation

Managing Quartus II Projects

Send Feedback

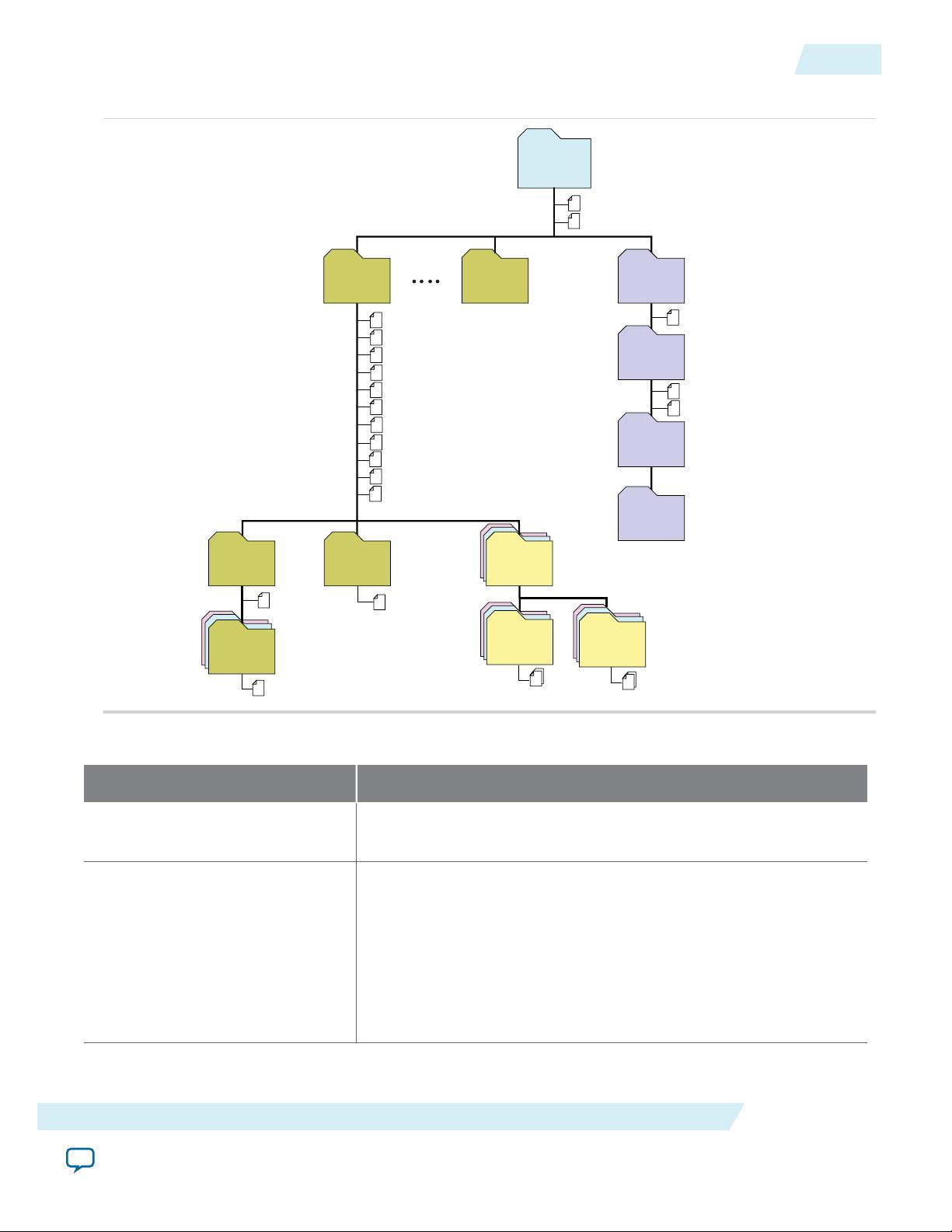

Figure 1-16: IP Core Generated Files

<your_testbench>_tb.csv

<your_testbench>_tb.spd

<your_ip>.cmp - VHDL component declaration file

<your_ip>.ppf - XML I/O pin information file

<your_ip>.qip - Lists IP synthesis files

<your_ip>.sip - Contains assingments for IP simulation files

<your_ip>.v or .vhd

Top-level IP synthesis file

<your_ip>.v or .vhd

Top-level simulation file

<simulator_setup_scripts>

<your_ip>.qsys - System or IP integration file

<your_ip>_bb.v - Verilog HDL black box EDA synthesis file

<your_ip>_inst.v or .vhd - Sample instantiation template

<your_ip>_generation.rpt - IP generation report

<your_ip>.debuginfo - Contains post-generation information

<your_ip>.html - Connection and memory map data

<your_ip>.bsf - Block symbol schematic

<your_ip>.spd - Combines simulation scripts for multiple cores

<your_ip>_tb.qsys

Testbench system file

<your_ip>.sopcinfo - Software tool-chain integration file

<project directory>

<EDA tool setup

scripts>

<your_ip>

IP variation files

<testbench>_tb

testbench system

sim

Simulation files

synth

IP synthesis files

sim

simulation files

<EDA tool name>

Simulator scripts

<testbench>_tb

<ip subcores> n

Subcore libraries

sim

Subcore

Simulation files

synth

Subcore

synthesis files

<HDL files>

<HDL files>

<your_ip> n

IP variation files

testbench files

Table 1-4: IP Core Generated Files

File Name Description

<my_ip>.qsys

The Qsys system or top-level IP variation file. <my_ip> is the name

that you give your IP variation.

<system>.sopcinfo Describes the connections and IP component parameterizations in

your Qsys system. You can parse its contents to get requirements

when you develop software drivers for IP components.

Downstream tools such as the Nios II tool chain use this file.

The .sopcinfo file and the system.h file generated for the Nios II tool

chain include address map information for each slave relative to each

master that accesses the slave. Different masters may have a different

address map to access a particular slave component.

QII5V1

2015.05.04

Files Generated for Altera IP Cores

1-19

Managing Quartus II Projects

Altera Corporation

Send Feedback

剩余1799页未读,继续阅读

JAD7998

- 粉丝: 58

- 资源: 30

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- C++标准程序库:权威指南

- Java解惑:奇数判断误区与改进方法

- C++编程必读:20种设计模式详解与实战

- LM3S8962微控制器数据手册

- 51单片机C语言实战教程:从入门到精通

- Spring3.0权威指南:JavaEE6实战

- Win32多线程程序设计详解

- Lucene2.9.1开发全攻略:从环境配置到索引创建

- 内存虚拟硬盘技术:提升电脑速度的秘密武器

- Java操作数据库:保存与显示图片到数据库及页面

- ISO14001:2004环境管理体系要求详解

- ShopExV4.8二次开发详解

- 企业形象与产品推广一站式网站建设技术方案揭秘

- Shopex二次开发:触发器与控制器重定向技术详解

- FPGA开发实战指南:创新设计与进阶技巧

- ShopExV4.8二次开发入门:解决升级问题与功能扩展

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功