CPLD驱动的高效能数字信号发生器:DDFS与单片机协作设计

67 浏览量

更新于2024-08-28

1

收藏 205KB PDF 举报

本文主要探讨的是基于CPLD(复杂可编程逻辑器件)的函数信号发生器设计,这是一种创新的解决方案,旨在克服传统模拟信号源设计的局限性。传统的设计通常依赖于模拟分立元件或单片压控函数发生器MAX038,这类方法存在元件分散性大、频率稳定性差、精度低、抗干扰能力弱、成本高且灵活性有限的问题。

DDFS(直接数字频率合成)技术的引入是本文的核心。DDFS利用单片机控制CPLD,显著提升了信号发生器的性能。CPLD的可编程重置特性使得设计更加灵活,可以方便地调整控制方式和波形数据,从而实现多种波形生成和波形运算输出。这不仅提高了系统的精度和稳定性,还简化了系统升级流程,具有较高的性价比。

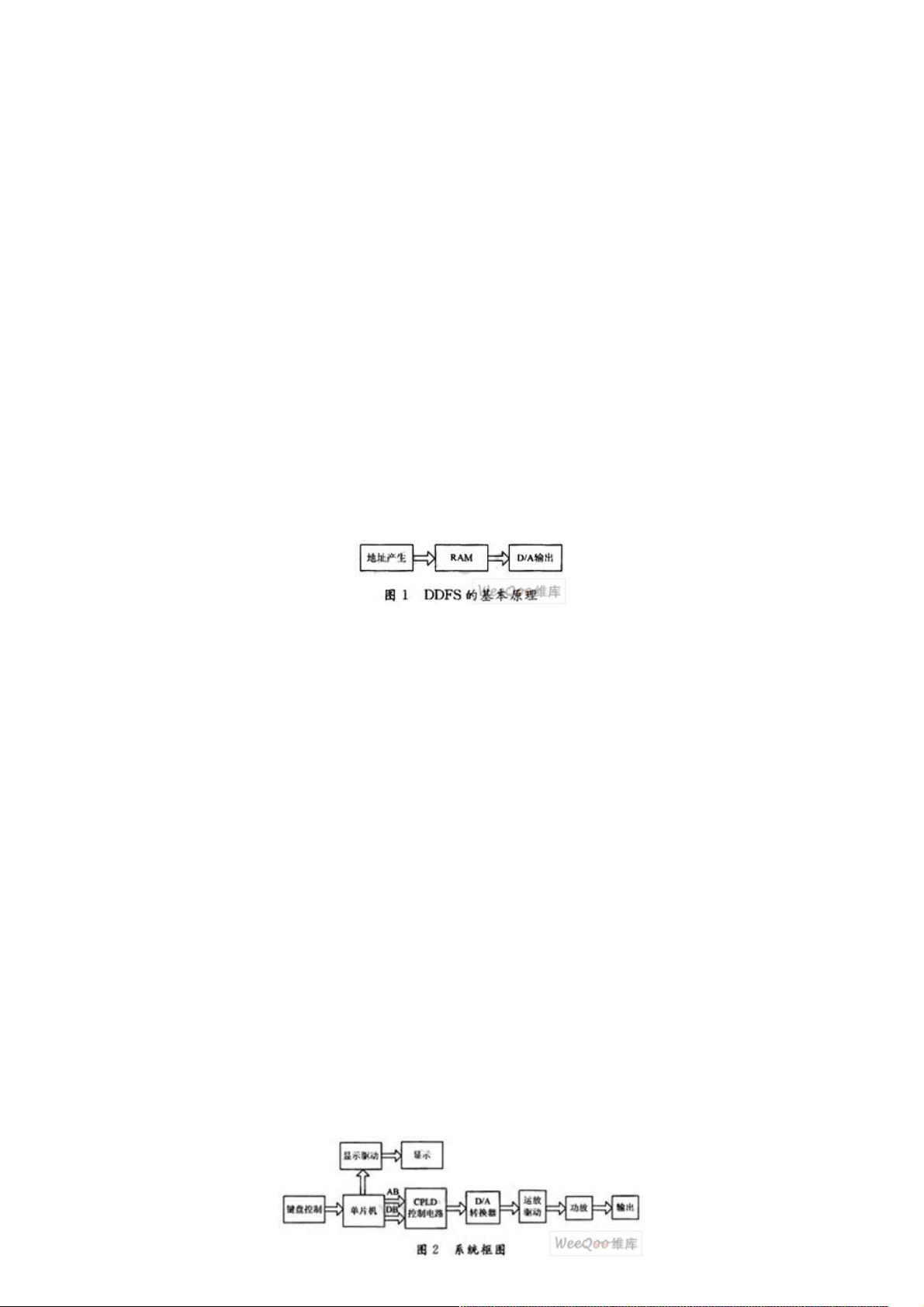

DDFS的基本原理涉及将一个高稳定度和高精度的标准频率进行数字处理,通过相位累加技术控制输出波形的频率。具体来说,输出波形的周期和幅度被存储在随机访问存储器(RAM)中,随着RAM地址的变化,数字到模拟转换器(DAC)将这些数据转换成对应的电压波形,而波形的频率则由RAM地址变化的速度决定。通过改变相位累加寄存器(Phase Increment Register, PIR)中的常数,可以精确控制每周期内的采样点数,从而实现不同频率的输出。

基于CPLD的函数信号发生器设计通过结合DDFS技术和CPLD的可编程能力,不仅提高了信号发生器的性能,如频率准确性和灵活性,还降低了成本和复杂性,为现代电子系统提供了一个高效且经济的信号源解决方案。这种设计方法对于电子工程师来说,具有很高的实用价值和研究价值。

467 浏览量

120 浏览量

2024-11-01 上传

108 浏览量

373 浏览量

2024-11-01 上传

2024-11-01 上传

2024-11-02 上传

weixin_38730840

- 粉丝: 2

- 资源: 968

最新资源

- SDE工具包-最新版

- undertow-cdi-jaxrs-rest-api-json:JEE应用程序示例+ CDI +具有Undertow + REST + JSON的嵌入式Servlet容器

- cubeJSgames-开源

- 你抓不到我

- lpc13-exploit:Golang中的最小UART客户端,可转储锁定在CRP1的LPC1343芯片

- sciencewarp-unexpo:专为UNEXPO Vicerrectorado波多黎各奥尔达斯大学的社区服务项目而开发的项目

- ORMDroid是适用于您的Android应用程序的简单ORM持久性框架。-Android开发

- roxLife-开源

- Sqlite 数据库文件更新机制

- 经文汇编软件,自学的好帮手

- securityjwt-old.zip

- git-rdm:Git版本控制系统的研究数据管理插件

- matlab标注字体代码-ScientificFigurePlot:Matlab代码,用于方便地绘制2Dcuves(包括颜色,标签,字体等)

- EmployeeManagement-java

- interactive-coding-tutorial:交互式js,画布

- 长按碎屏效果