FPGA开发:外设子板蜂鸣器与LED电路详解

PDF格式 | 306KB |

更新于2024-09-02

| 105 浏览量 | 举报

FPGA开发外设子板模块电路设计是一门涉及硬件工程和软件编程的重要技术,它主要利用FPGA这种高度灵活的可编程逻辑器件来构建定制化的电子系统。FPGA起源于可编程门阵列(PAL)、全局可编程逻辑阵列(GAL)和复杂可编程逻辑器件(CPLD)的升级,它在ASIC(专用集成电路)领域扮演着半定制化解决方案的角色,既能避免定制电路成本高、周期长的问题,又能提供比传统可编程器件更丰富的逻辑门电路资源。

与传统的PC或单片机(如基于冯诺依曼架构或哈佛架构的处理器)相比,FPGA的开发模式迥异。FPGA侧重于并行处理,采用硬件描述语言(HDL,如Verilog或 VHDL)进行逻辑电路的描述和设计,这使得它在处理大规模数据并行任务时展现出优势,但同时也对开发者的硬件设计和编程技能提出了更高的要求。由于其独特的编程方式,FPGA的上手难度相对较大,需要一定的专业知识和实践经验。

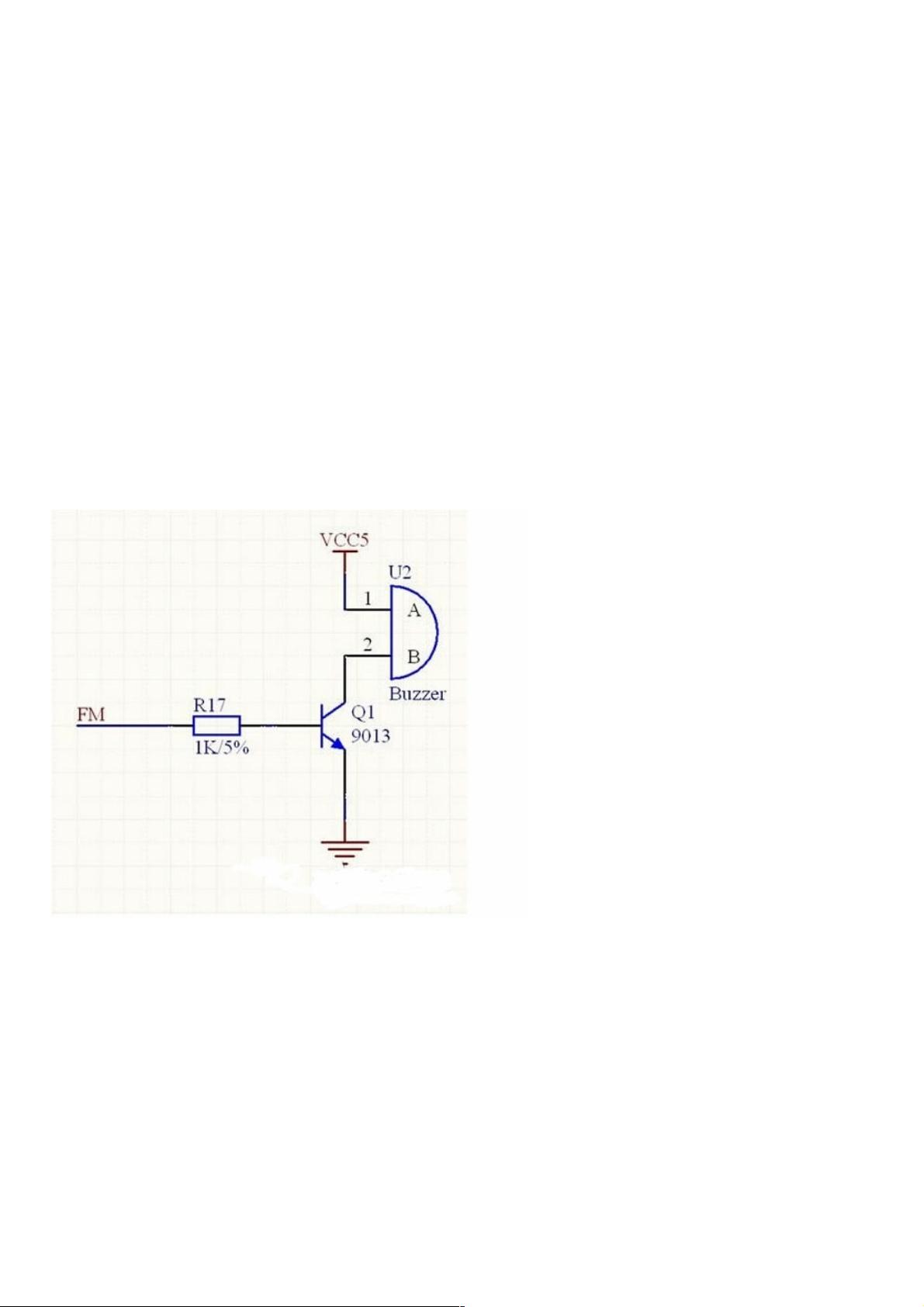

在具体的应用实例中,如图3.47所示的蜂鸣器电路设计是FPGA开发中的一个基础项目。蜂鸣器通过FPGA的输入输出(I/O)接口进行控制。当输入的FM信号为高电平时,通过晶体管Q1的BE引脚导通,使控制引脚CE接通,形成5V电源和地(GND)之间的闭合回路,从而驱动蜂鸣器发声。相反,当FM信号为低电平时,Q1的BE引脚断开,CE引脚也随之断开,蜂鸣器不再有电流通过,停止发声。

在实验中,可以通过脉宽调制(PWM)信号控制Q1的导通与截止,这意味着蜂鸣器会在固定的时间间隔内被开启和关闭,从而产生不同频率的声音,这是FPGA灵活运用数字信号处理能力的一个体现。同时,电路中还包括8个LED灯,这些LED灯可能与FPGA的其他I/O口相连,用于显示状态或作为其他功能的指示灯。

FPGA开发外设子板模块电路设计是一个结合硬件描述、数字逻辑、信号处理和接口控制的综合实践过程,对于提升电子系统的灵活性和性能有着重要作用。对于想要深入学习和应用FPGA的工程师来说,理解并掌握这些原理和技巧是至关重要的。

相关推荐

weixin_38558623

- 粉丝: 4

- 资源: 930