DWM1000: 高精度UWB无线通信模块

需积分: 9 186 浏览量

更新于2024-07-17

收藏 1.57MB PDF 举报

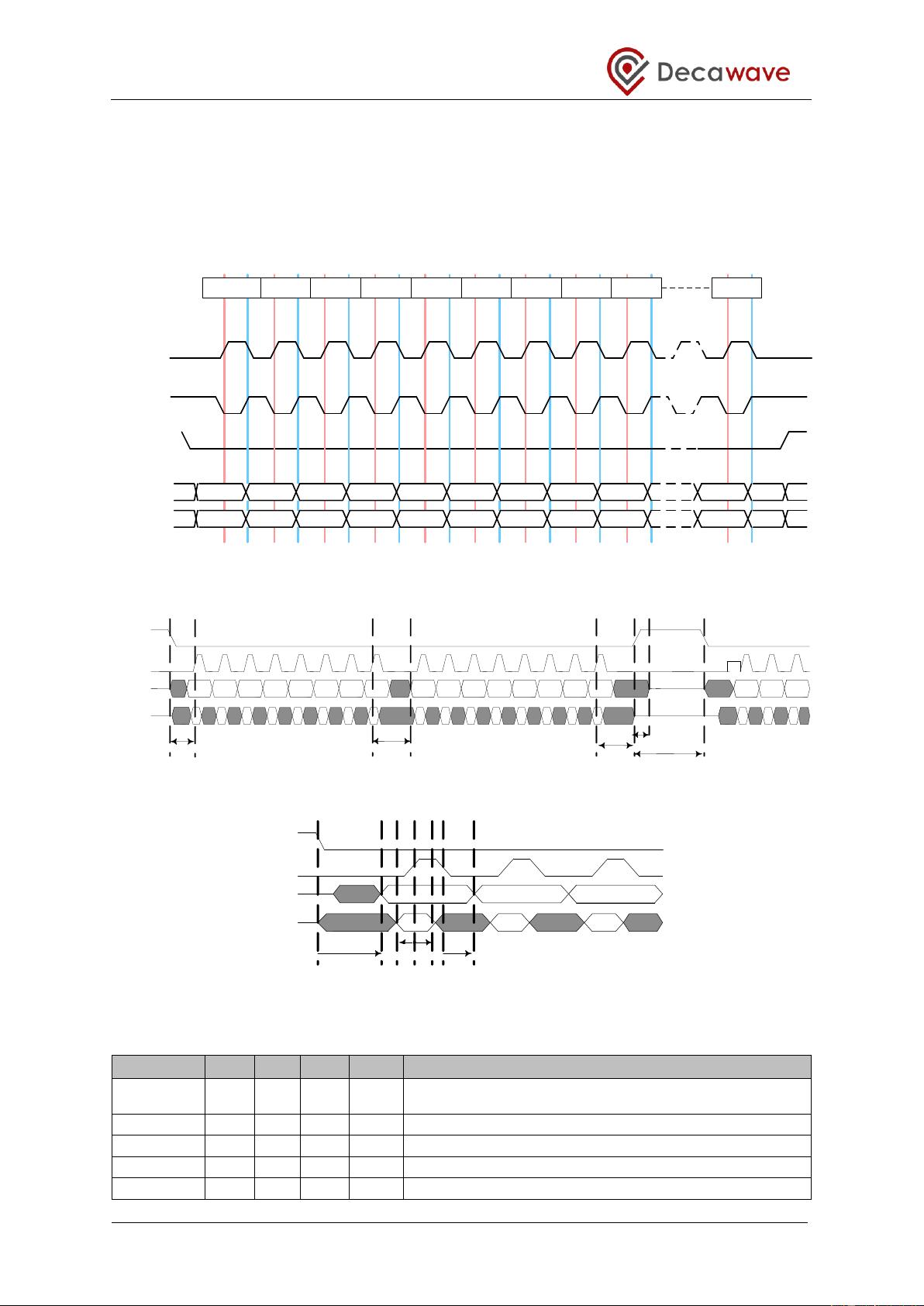

"DWM1000是一款基于Decawave的DW1000超宽带(UWB)收发器IC的模块,适用于2-way ranging或TDOA定位系统,可实现10厘米精度的资产定位,并支持最高6.8Mbps的数据速率。该模块集成了天线、所有射频电路、电源管理和时钟电路。它符合IEEE 802.15.4-2011标准,支持4个频率范围从3.5GHz到6.5GHz的RF频段,具有可编程的发射功率和全相干接收器以确保最大范围和准确性。此外,DWM1000设计符合FCC和ETSI的UWB频谱掩模要求,工作电压为2.8V至3.6V,低功耗,数据速率可达110kbps、850kbps和6.8Mbps,最大包长度为1023字节,适合高数据吞吐量应用。它还集成了MAC支持功能,支持双向测距和TDOA,通过SPI接口与主机处理器通信,采用23mm x 13mm x 2.9mm的24-pin侧卡封装。"

DWM1000模块的主要特点和优势如下:

1. **符合标准**:DWM1000符合IEEE 802.15.4-2011超宽带标准,这意味着它在设计和功能上遵循了这一国际认可的技术规范,保证了与其他兼容设备的互操作性。

2. **频率支持**:模块支持4个不同的RF频段,从3.5GHz到6.5GHz,这提供了更广泛的频谱选择,适应不同的应用场景。

3. **可编程发射功率**:用户可以根据具体需求调整发射功率,以优化传输距离和功耗平衡。

4. **全相干接收器**:全相干接收器的设计提高了接收信号的准确性和接收范围,对提高定位精度至关重要。

5. **法规合规**:DWM1000设计符合FCC(美国联邦通信委员会)和ETSI(欧洲电信标准协会)的UWB频谱掩模要求,可以在全球范围内合法使用。

6. **电源管理**:工作电压范围2.8V至3.6V,表明它能够在较低的电源条件下运行,有利于降低系统的整体能耗。

7. **数据速率**:支持高达6.8Mbps的数据速率,使得快速传输大量数据成为可能,适用于高数据流量的应用场景。

8. **大容量数据包**:最大包长度为1023字节,适合需要大量数据交换的高数据吞吐量应用。

9. **集成MAC功能**:内置MAC层支持,简化了网络协议的处理,降低了系统复杂性。

10. **双向测距和TDOA**:支持两种定位方法,不仅可以进行单点定位,还可以通过时间差到达(TDOA)实现多点定位,提高了定位精度和灵活性。

11. **SPI接口**:通过SPI接口与主处理器通信,简化了系统集成,减少了外部组件的需求。

12. **紧凑封装**:23mm x 13mm x 2.9mm的小型封装尺寸,使DWM1000适合空间有限的嵌入式系统设计。

DWM1000模块因其集成度高、性能优越、符合标准、功耗低以及支持多种定位技术而被广泛应用于室内定位、物联网(IoT)设备、无线传感器网络等场景。它简化了设计流程,无需复杂的RF设计,可以快速、精确地定位物体,从而提高企业效率,降低成本,并扩展通信范围,减少对基础设施的需求。

2024-03-01 上传

2024-03-01 上传

2024-03-01 上传

2024-03-01 上传

2022-07-15 上传

2024-03-01 上传

小鹿的洋花园

- 粉丝: 169

最新资源

- 深入探讨V2C控制Buck变换器稳定性分析及仿真验证

- 2012款途观怡利导航破解方法及多图功能实现

- Vue.js图表库vuetrend:简洁优雅的动态数据展示

- 提升效率:仓库管理系统中的算法与数据结构设计

- Matlab入门必读教程——快速上手指南

- NARRA项目可视化工具集 - JavaScript框架解析

- 小蜜蜂天气预报查询系统:PHP源码与前端后端应用

- JVM运行机制深入解析教程

- MATLAB分子结构绘制源代码免费分享

- 掌握MySQL 5:《权威指南》第三版中文版

- Swift框架:QtC++打造的易用Web服务器解决方案

- 实现对话框控件自适应的多种效果

- 白镇奇士推出DBF转EXCEL高效工具:hap-dbf2xls-hyy

- 构建简易TCP路由器的代码开发指南

- ElasticSearch架构与应用实战教程

- MyBatis自动生成MySQL映射文件教程