DSP+CPLD结合的智能电力监测系统设计

18 浏览量

更新于2024-08-31

收藏 151KB PDF 举报

"基于DSP+CPLD的新型智能监测系统设计与开发"

本文主要探讨了如何利用数字信号处理器(DSP)和复杂可编程逻辑器件(CPLD)相结合的技术,构建一个高级智能化的监测系统,特别是在电力系统大型设备的智能在线监测中的应用。这种结合为测控仪器的智能化发展开辟了新的道路。

一、背景与需求

电动机作为电力系统中的关键设备,其运行状况直接影响到整个系统的稳定性和经济效益。传统的基于单片机的保护装置在处理能力、实时性以及系统灵活性方面存在局限,无法满足日益增长的智能化需求。而DSP处理器凭借其独特的哈佛结构,具备强大的计算能力和出色的实时性能,可以高效处理大量数据。同时,CPLD和现场可编程门阵列(FPGA)的发展,提供了高度灵活的硬件配置方案,使得系统设计更具可扩展性和定制性。

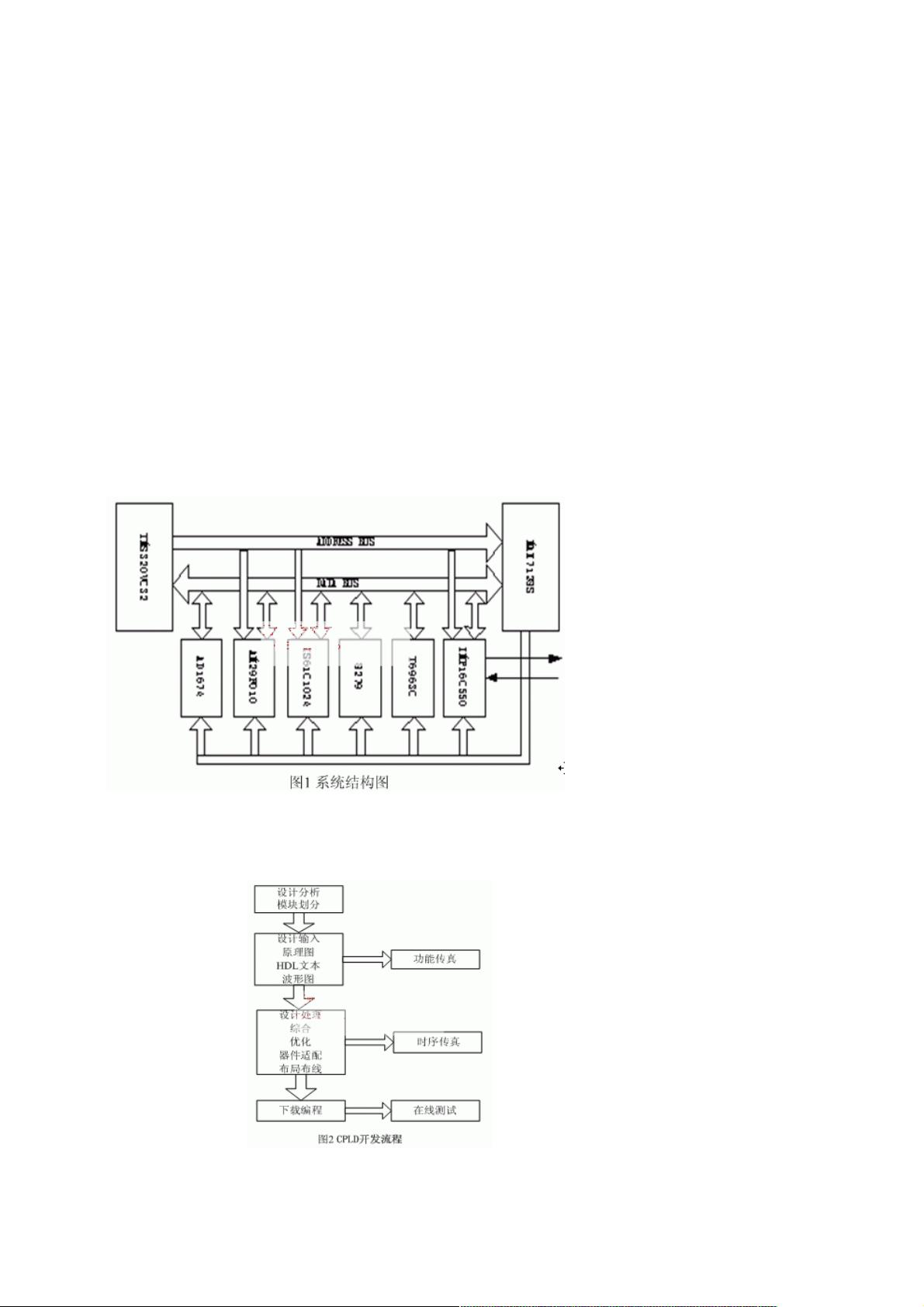

二、系统架构

该智能监测系统选用美国德州仪器(TI)公司的浮点型DSP作为核心处理器,它能够快速处理复杂的算法和实时数据。CPLD作为辅助处理器,用于实现系统控制逻辑和接口功能,以提高系统的响应速度和整体性能。这种结合使得系统在处理大量实时数据的同时,还能进行复杂的决策和控制,满足智能监测的需求。

三、CPLD开发流程

CPLD的开发涉及从设计概念到硬件实现的全过程。首先,开发者需要根据系统需求,使用硬件描述语言(如VHDL或Verilog)编写逻辑设计。接着,使用专用的开发软件进行编译和仿真,验证设计的正确性。随后,将编译后的配置文件下载到CPLD中,实现硬件逻辑。这个过程包括设计输入、逻辑综合、布局布线、配置下载等多个步骤,确保CPLD能够按照预期执行用户设计的功能。

四、液晶显示模块设计

系统采用内置T6963C控制器的液晶显示模块,该模块具有指令锁存器、数据锁存器等组件,可以实现CPU与T6963C之间的通信协调。接口设计确保了CPU的指令和数据能够在不影响其他操作的情况下正确传输到液晶屏上,同时处理内部时序和CPU操作时序的匹配问题,保证了显示的实时性和准确性。

总结,本文提出的基于DSP+CPLD的智能监测系统设计,不仅克服了传统单片机系统的局限,还充分利用了DSP的高性能计算能力和CPLD的高度可配置性,为电力系统设备的智能在线监测提供了高效、灵活的解决方案。这样的设计思路对于未来智能监测系统的发展具有重要的参考价值。

188 浏览量

点击了解资源详情

106 浏览量

188 浏览量

2021-09-21 上传

105 浏览量

125 浏览量

2021-09-21 上传

2021-05-10 上传

weixin_38622427

- 粉丝: 0

- 资源: 951

最新资源

- GameProjectOne

- OpenHU:Android Auto的开源主机应用程序的延续,该应用程序最初由已故的Mike Reid创建。 在使用或提交代码之前,请查阅许可文档,并访问控制台Wiki以获取完整的文档。-Android application source code

- es6-walkthroughs:ECMAscript 6 中新功能的演练

- PHP实例开发源码—php盾灵广告联盟系统.zip

- go-nix

- VisionFaceDetection:在iOS 11中使用Vision框架进行人脸标志检测的示例

- Quiz-application:测验申请包括5个问题

- prometheus-alert-rules:普罗米修斯警报规则的收集

- 秒

- 基于STM32的智能逆变电源设计.zip

- 21世纪信息经济增长的主体效应

- do_something_express_part4:[表示]

- gatsby-conf-main

- leetcode答案-Leetcode:力码

- 清华大学ADAMS基础教程.zip

- 记录:可能永远不应该跟踪的可疑事物的记录