S3C2440中断机制详解:寄存器与流程深入解析

需积分: 9 39 浏览量

更新于2024-07-24

1

收藏 303KB DOCX 举报

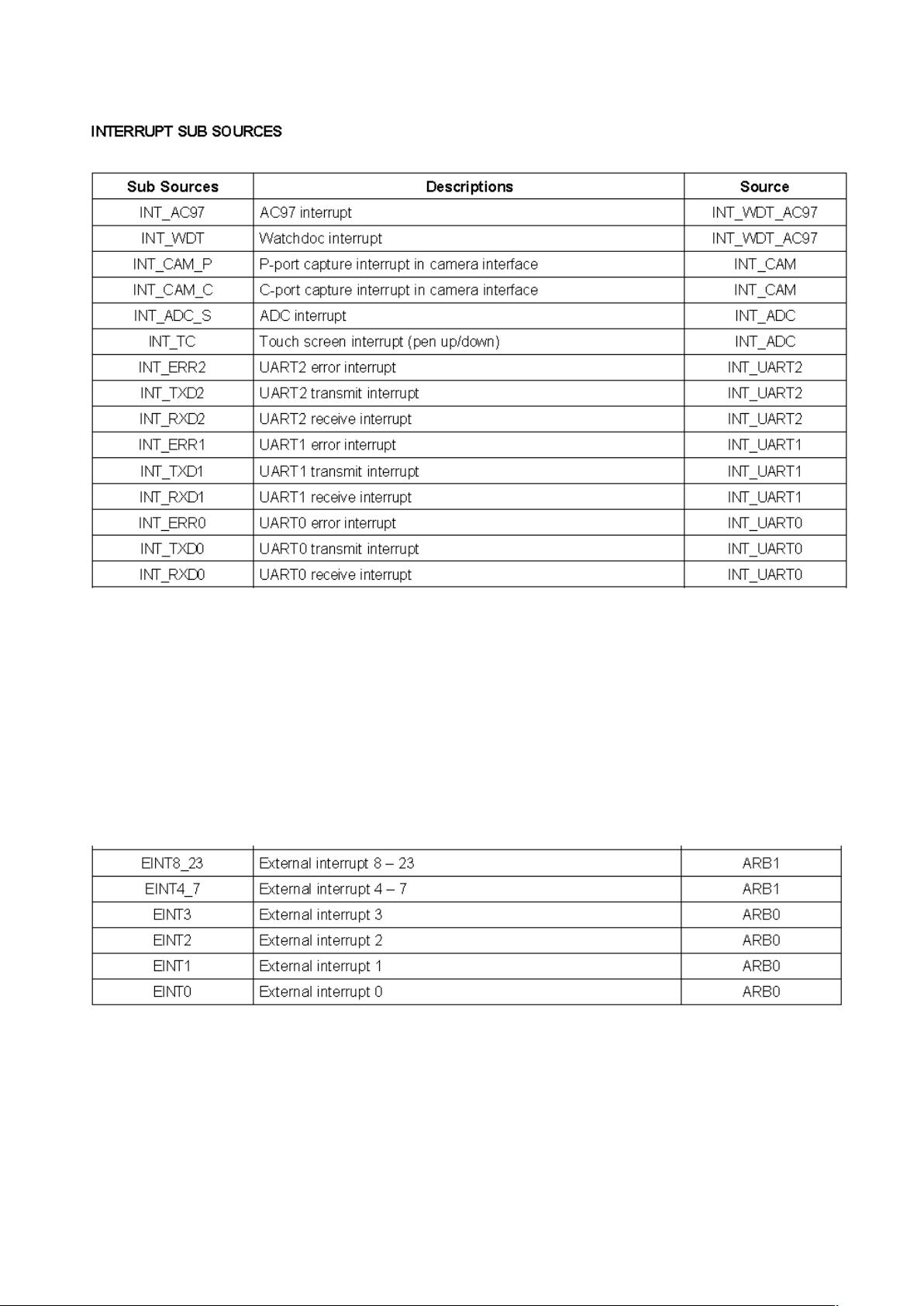

本文档深入解析了三星S3C2440处理器的中断系统,这是一种基于ARM920T架构的嵌入式微控制器,其中断机制对于理解和优化系统性能至关重要。S3C2440总共拥有60个中断源,分为外部中断和内部中断两部分。

外部中断主要来自GPF0至GPF7(EINT0至EINT7)和GPG0至GPG15(EINT8至EINT23)的输入引脚,可以配置为各种触发方式,如高电平、低电平、上升沿或下降沿触发。EINTFLT寄存器用于控制外部中断的滤波时钟和宽度,确保中断信号的准确性。EINTPEND寄存器用于挂起中断,通过写1来清除中断标志,但EINT0至EINT3由SRCPND寄存器的后四位控制,不直接通过EINTPEND管理。

内部中断则涉及到SUBSRCPND、INTSUBMSK、SRCPND、INTMSK、INTMOD、PRIORITY和INTPND等寄存器。SUBSRCPND和SRCPND寄存器分别记录了子中断和主中断的发生情况,INTSUBMSK和INTMSK则是用来屏蔽中断,前者针对子中断,后者针对SRCPND标识的中断,但不能屏蔽FIQ中断。INTMOD允许用户选择中断类型,当设置为FIQ时,CPU将立即响应。PRIORITY用于设置IRQ中断的优先级,INTPND寄存器负责中断优先级仲裁,只保留优先级最高的中断,而INTOFFSET则记录INTPND中被触发的中断位置。

理解并有效利用这些中断寄存器,开发者能够灵活地管理设备的各种中断事件,提高系统的响应速度和效率。在实际应用中,需要根据具体需求配置中断触发条件、屏蔽和优先级,以实现最优的硬件资源管理和系统行为控制。通过学习和实践S3C2440的中断机制,开发人员能够更好地设计出响应迅速、功能强大的嵌入式系统。

117 浏览量

117 浏览量

117 浏览量

点击了解资源详情

109 浏览量

2022-09-20 上传

2022-09-22 上传

2022-09-24 上传

2022-09-19 上传

zDarkBlue

- 粉丝: 122

- 资源: 44

最新资源

- FonePaw_Video_Converter_Ultimate_2.9.0.93447.zip

- 162100头像截图程序 4.1

- subclass-dance-party

- JavaScript:Curso完成JavaScript

- Medical_Payment_Classification:确定医疗付款是用于研究目的还是用于一般用途

- P1

- javascript-koans

- 保险行业培训资料:寿险意义与功用完整版本

- ChandyMishraHaasOrAlgo

- maven-repo

- react-as-space

- eclipse-inst-mac64.dmg.zip

- bearsunday.github.io

- ks

- lazytoby.github.io

- 0.96寸OLED(IIC接口)显示屏的图像显示应用