20

TLV320DAC3101

ZHCSIV8B –JANUARY 2010–REVISED OCTOBER 2018

www.ti.com.cn

Submit Documentation Feedback

Product Folder Links: TLV320DAC3101

Detailed Description Copyright © 2010–2018, Texas Instruments Incorporated

6.3.2 Reset

The internal logic must be initialized to a known condition for proper device function. To initialize the

device to its default operating condition, the hardware reset pin (RESET) must be pulled low for at least 10

ns. For this initialization to work, both the IOVDD and DVDD supplies must be powered up. TI

recommends that while the DVDD supply powers up, the RESET pin is pulled low.

The device can also be reset via software reset. Writing a 1 into page 0 / register 1, bit D0 resets the

device.

6.3.3 Device Start-Up Lockout Times

After the is initialized through hardware reset at power up or software reset, the internal memories are

initialized to default values. This initialization takes place within 1 ms after pulling the RESET signal high.

During this initialization phase, no register-read or register-write operation should be performed on DAC

coefficient buffers. Also, no block within the codec should be powered up during the initialization phase.

6.3.4 PLL Start-Up

Whenever the PLL is powered up, a start-up delay of approximately of 10 ms occurs after the power-up

command of the PLL and before the clocks are available to the codec. This delay is to ensure stable

operation of the PLL and clock-divider logic.

6.3.5 Power-Stage Reset

The power-stage-only reset is used to reset the device after an overcurrent latching shutdown has

occurred. Using this reset re-enables the output stage without resetting all of the registers in the device.

Each of the four power stages has its own dedicated reset bit. The headphone power-stage reset is

performed by setting page 1 / register 31, bit D7 for HPL and by setting page 1 / register 31, bit D6 for

HPR. The speaker power-stage reset is performed by setting page 1 / register 32, bit D7 for SPLP and

SPLM, and by setting page 1 / register 32, bit D6 for SPRP and SPRM.

6.3.6 Software Power Down

By default, all circuit blocks are powered down following a reset condition. Hardware power up of each

circuit block can be controlled by writing to the appropriate control register. This approach allows the

lowest power-supply current for the functionality required. However, when a block is powered down, all of

the register settings are maintained as long as power is still being applied to the device.

6.3.7 Audio Analog I/O

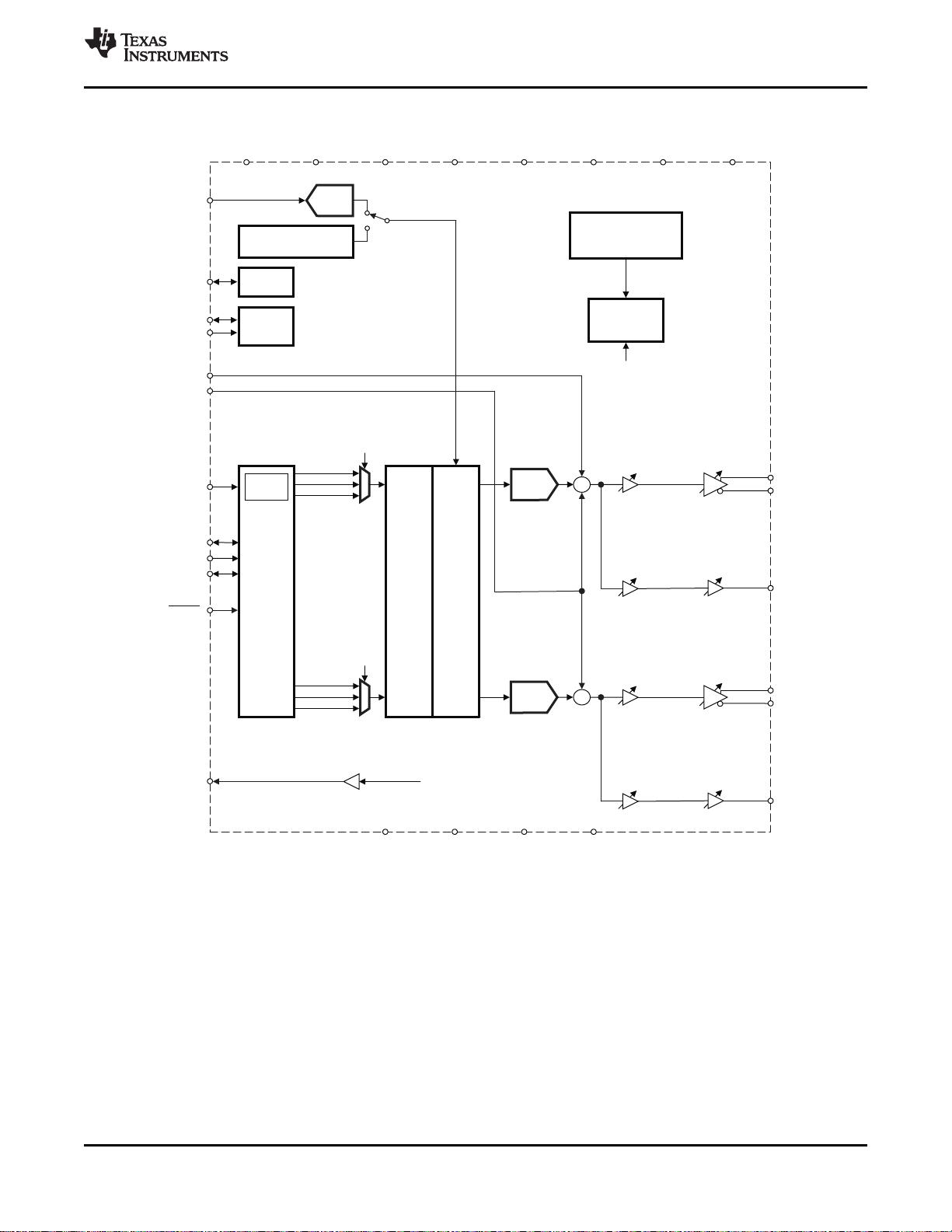

The has a stereo audio DAC. The device supports a wide range of analog interfaces to support different

headsets and analog outputs. The has features to interface output drivers (8-Ω, 16-Ω, 32-Ω). A special

circuit has also been included in the to insert a short key-click sound into the stereo audio output. The key-

click sound is used to provide feedback to the user when a particular button is pressed or item is selected.

The specific sound of the keyclick can be adjusted by varying several register bits that control its

frequency, duration, and amplitude (see Section 6.3.10.7).

6.3.8 Digital Processing Low-Power Modes

The device can be tuned to minimize power dissipation, to maximize performance, or to an operating point

between the two extremes to best fit the application. The choice of processing blocks, PRB_P1 to

PRB_P25 for stereo playback, also influences the power consumption. In fact, the numerous processing

blocks have been implemented to offer a choice among configurations having a different balance of power

optimization and signal-processing capabilities.

6.3.8.1 DAC Playback on Headphones, Stereo, 48 kHz, DVDD = 1.8 V, AVDD = 3.3 V,

HPVDD = 3.3 V

DOSR = 128, Processing Block = PRB_P7 (Interpolation Filter B)