cadence原理图设计步骤详解

147 浏览量

更新于2024-09-02

收藏 979KB PDF 举报

"CADENCE原理图设计流程的详细步骤解析,适用于初学者的教程。"

CADENCE是一款广泛应用于电子设计自动化(EDA)领域的软件,尤其在硬件设计中,其原理图设计功能深受工程师们的青睐。本篇文章将深入探讨CADENCE原理图设计流程,帮助初学者快速上手。

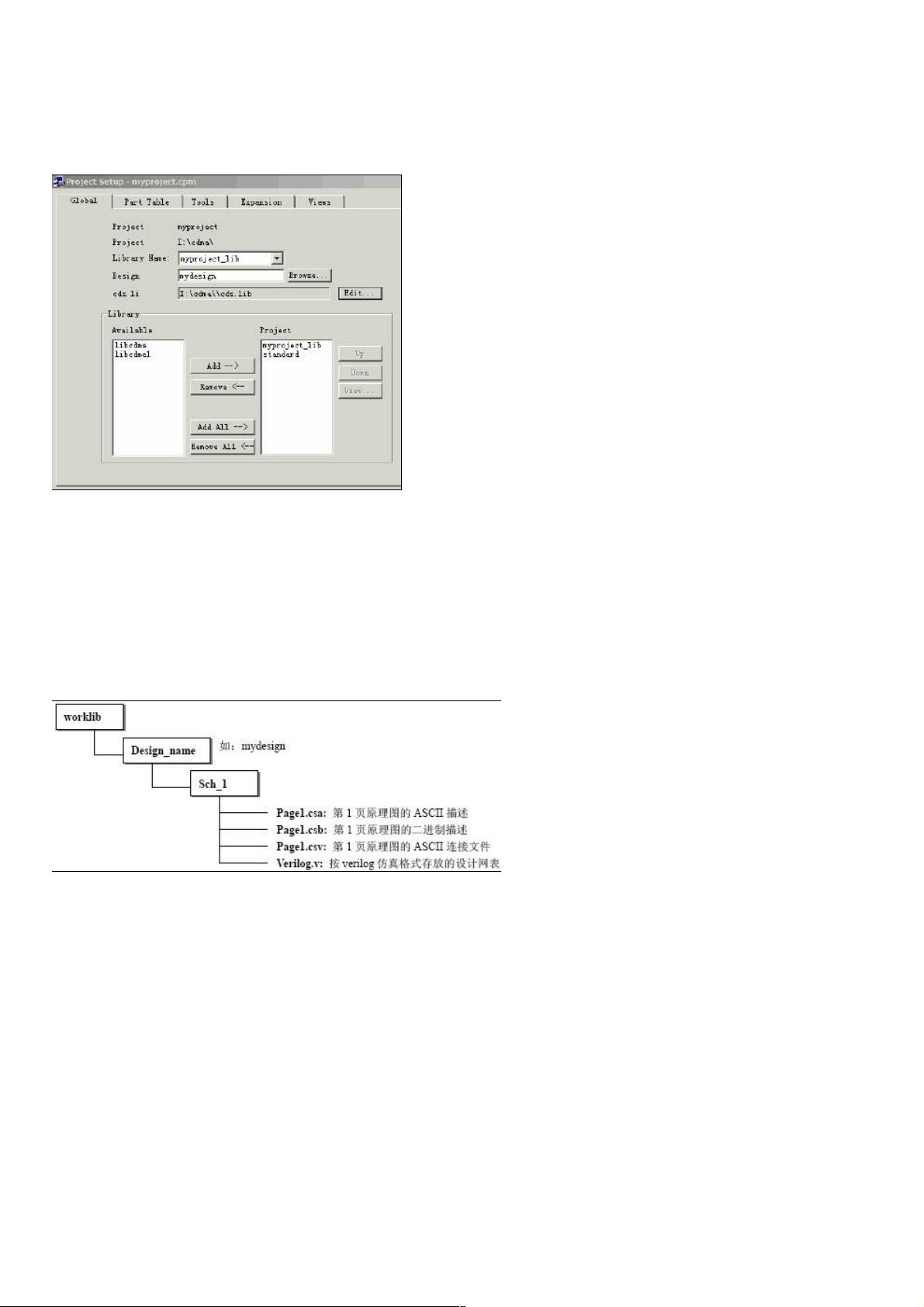

首先,建立一个新的工程是设计流程的第一步。在CADENCE中,你需要使用ProjectManager来配置设计目录。通过“New”选项创建新的Project,并根据提示设置项目名称(如myproject),这将生成对应的.cpm项目文件和.lib设计库文件。接着,选择所需的库,如myproject_lib,以便在项目中使用。确保所有的共享原理图库已同步并放置在指定位置,例如D:盘的libcdma和libcdma1目录。编辑cds.lib文件,使用`definelib`命令将共享库添加到AvailableLibrary中,然后通过“Add”将其移至ProjectLibrary。

完成工程配置后,你可以进入Concept-HDL环境开始绘制原理图。Concept-HDL是CADENCE的核心设计输入工具,其界面包含多个工作区域,便于管理设计的不同阶段。

1. **添加元件**:在设计流程中,第一步是找到合适的元件符号,这可以通过搜索或从库中拖拽完成。CADENCE支持自定义库,因此你可以根据需求添加或修改元件。

2. **连接线与网络**:连接线用于将元件的引脚相连,形成电路网络。在Concept-HDL中,可以使用鼠标拖动来绘制线条,或者使用预定义的网络标签快速连接。

3. **属性设置**:每个元件都有属性,包括值、封装等信息。这些属性可以在元件属性对话框中设置,对后续的仿真和PCB布局布线至关重要。

4. **层次设计**:大型设计通常会采用层次化方法,将复杂电路分解为子模块。在CADENCE中,你可以创建子电路,然后在主电路中引用它们,简化设计和管理。

5. **检查与验证**:在设计过程中,定期进行电气规则检查(ERC)以发现潜在的短路、开路等问题。同时,使用设计规则检查(DRC)确保符合制造工艺限制。

6. **保存与版本控制**:设计应定期保存,以防止意外丢失。对于团队协作项目,使用版本控制系统(如SVN或Git)来跟踪和管理不同版本的设计。

7. **生成网表**:完成设计后,通过网表生成器将原理图转换为网表文件,这是后续逻辑综合、仿真和PCB布局布线的基础。

8. **仿真验证**:使用CADENCE的SPICE工具,如Spectre,对原理图进行功能和性能仿真,确保设计满足预期。

9. **输出与导出**:最后,将经过验证的原理图导出为其他工具(如PCB设计工具)所需的格式,完成整个设计流程。

掌握CADENCE原理图设计流程需要时间和实践,但遵循以上步骤并不断学习,初学者将能逐步成长为熟练的硬件设计师。在设计过程中,理解每个步骤的目的和作用,以及如何与其他设计阶段(如仿真和PCB设计)协同工作,是非常重要的。

192 浏览量

193 浏览量

253 浏览量

253 浏览量

121 浏览量

283 浏览量

159 浏览量

131 浏览量

282 浏览量

weixin_38747144

- 粉丝: 4

- 资源: 938

最新资源

- Chrome tab counter-crx插件

- Layui 元件库.zip

- KVStore:分布式多一致性键值存储

- nfr:一种轻量级工具,可对网络流量进行评分并标记异常

- Java-Http-Server

- jhipster-bookstore:使用jhipster(angular + spring + ehcache + mvn + grunt)生成的项目

- Open1560

- APx500_4.2.1 音频分析仪 APX515 APX525

- Hadoop&Hbase.rar

- qrrs:CLI QR代码生成器和用锈写的阅读器

- blink.X_blink_PIC_

- nycblog-semantichtml

- Android面试题.zip

- kubernetes-kargo-logging-monitoring:使用kargo部署kubernetes集群

- shiwai-readable-code

- ADT_Set___Lab_1_HW:DSA第一次实验室评估