理解锁相环(PLL)基础:时钟净化与电路配置

需积分: 37 22 浏览量

更新于2024-08-08

1

收藏 1.58MB PDF 举报

"这篇文章主要介绍了锁相环(PLL)的基本原理,包括其基本配置、工作原理和关键组件,如鉴频鉴相器(PFD)、环路滤波器和压控振荡器(VCO)。文章引用了ADI公司的ADF4xxx和HMCxxx系列PLL产品,并使用ADIsimPLL仿真器展示不同电路性能参数。PLL常用于时钟净化、无线电通信和频率合成等高频应用。"

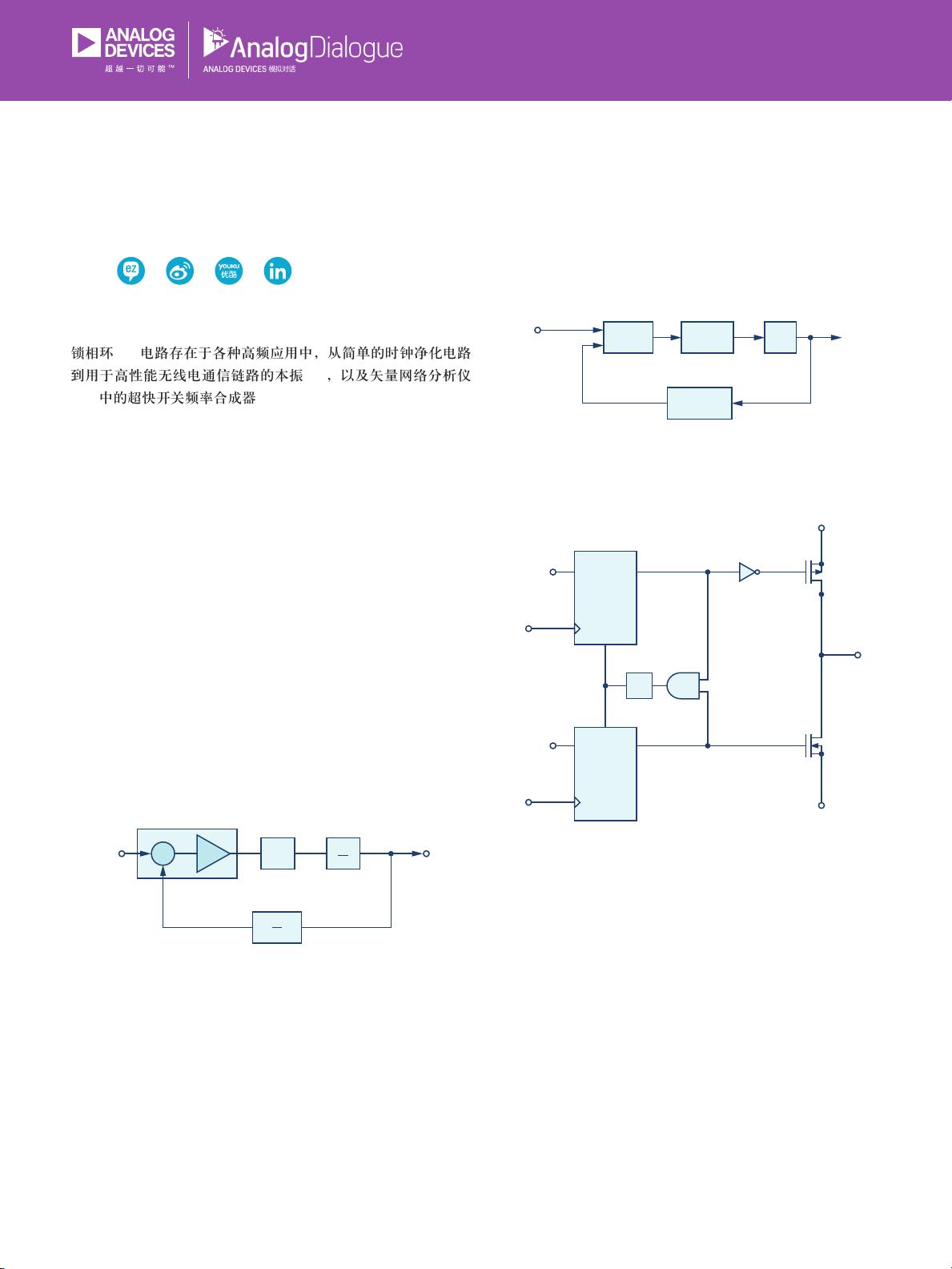

锁相环(PLL)是一种重要的电子技术,广泛应用于各种高频系统,如时钟同步、无线通信和频率合成。其基本工作原理是通过比较参考信号(FREF)与反馈信号(RFIN)的相位,调整输出信号以保持与参考信号的相位一致,从而实现频率锁定。

PLL的基本配置包括鉴频鉴相器(PFD)、环路滤波器和压控振荡器(VCO)。PFD是PLL的核心,它检测两个信号的相位差,输出相应的电流脉冲,这个电流脉冲被环路滤波器平滑处理后,控制VCO的频率。当PFD的输入频率不同,电荷泵会产生正或负电流,导致VCO的频率上升或下降,从而使两个输入信号相位趋于一致,实现锁相。

鉴频鉴相器如图3所示,由两个D型触发器和延迟元件组成,它能够检测频率和相位的差异。当+IN端的输入频率高于-IN端时,电荷泵输出正电流,反之则输出负电流。这种电流变化经过环路滤波器积分后,改变VCO的调谐电压,从而使VCO的输出频率跟随输入信号变化。

环路滤波器是PLL的重要组成部分,它的作用是滤除PFD产生的高频噪声,提供平滑的电压控制信号给VCO,确保系统的稳定性。在图4和图5中,展示了随着频率差异,电荷泵如何调节VCO的输出,使两个信号最终锁定在相同的频率上。

ADI公司的ADF4xxx系列PLL芯片提供了灵活的配置选项,例如ADF4002可以作为独立的PFD使用,适用于与高质量的压控晶体振荡器(VCXO)和窄带低通滤波器配合,以提高时钟清洁度。而HMCxxx系列可能包含了更复杂的PLL功能,适合高性能无线电通信应用。

理解PLL的工作原理和关键组件对于设计和优化高频系统至关重要。通过了解PFD的操作、环路滤波器的作用以及VCO的控制,工程师可以根据具体应用需求选择合适的PLL解决方案,并利用工具如ADIsimPLL进行电路性能的仿真和评估。

376 浏览量

3588 浏览量

540 浏览量

2009-07-10 上传

189 浏览量

809 浏览量

194 浏览量

TracelessLe

- 粉丝: 6w+

- 资源: 468