MPU SIGNAL DESCRIPTION

Proper operation of the MPU requires that certain control

and timing signals be provided to accomplish specific func-

tions and that other signal lines be monitored to determine

the state of the processor.

Clocks Phase One and Phase Two (o1, 42) – Two pins

are used for a two-phase non-overlapping clock that runs at

the VCC voltage level.

Figure 1 shows the microprocessor clocks. The high level

is specified at VIHC and the low level is specified at VILC.

The allowable clock frequency is specified by f (frequency).

The minimum @l and @2 high level pulse widths are specified

by PW~H (pulse width high time). To guarantee the required

access time for the peripherals, the clock up time, tut, is

specified. Clock separation, td, is measured at a maximum

voltage of VOV (overlap voltage), This allows for a multitude

of clock variations at the system frequency rate.

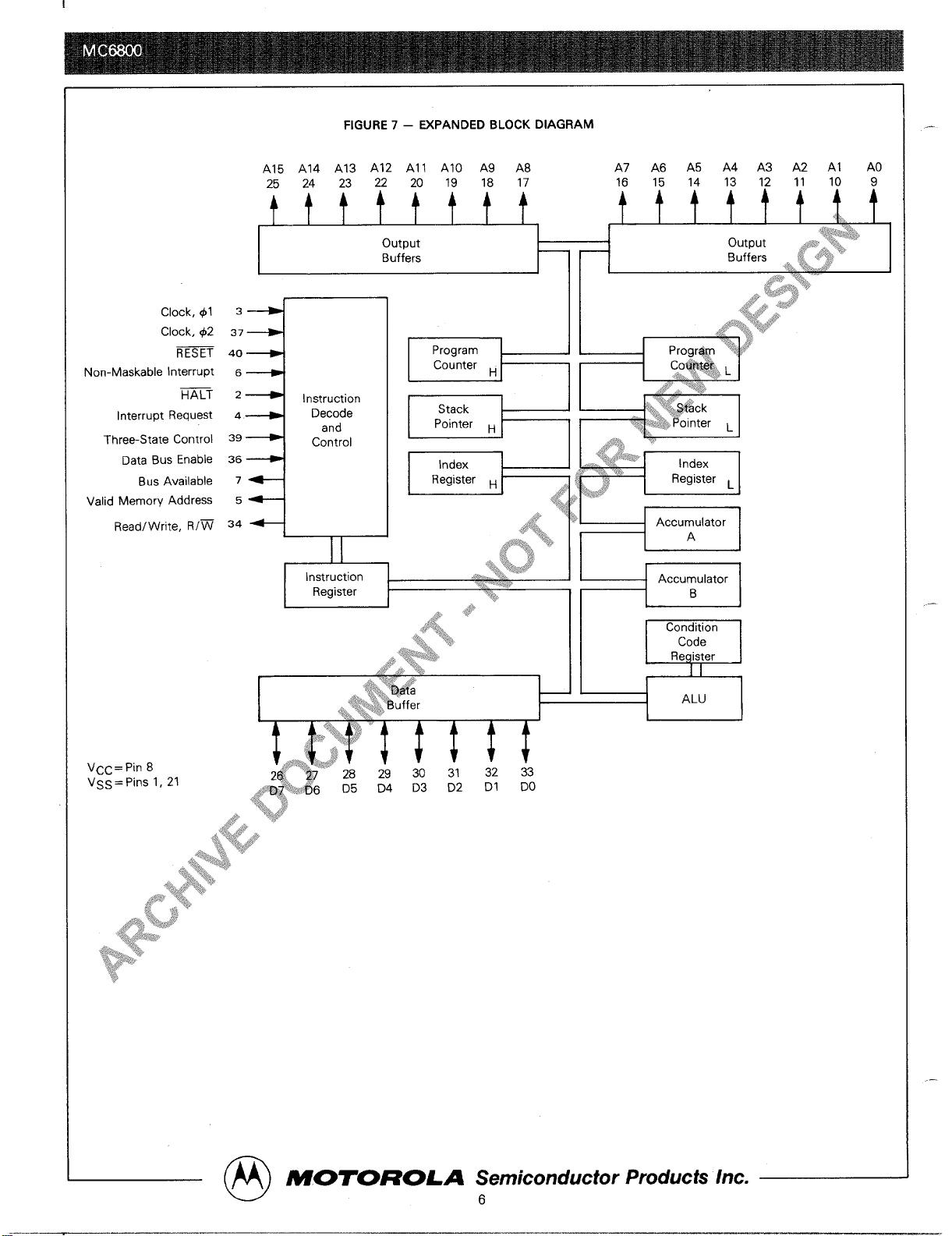

Address Bus (AOA15) – Sixteen pins are used for the ad-

dress bus. The outputs are three-state bus drivers capable of

driving one standard TTL load and 90 pF. When the output is

turned off, it is essentially an open circuit. This permits the

MPU to be used in DMA applications. Putting TSC in its high

state forces the Address bus to go into the three-state mode.

Data Bus (DO-D7) – Eight pins are used for the data bus.

It is bidirectional, transferring data to and from the memory

and peripheral devices. It also has three-state output buffer$

capable of driving one standard TTL load and 130 pF. D,a~$,

Bus is placed in the three-state mode when DBE is Io#t\,t w~$.

,{’.y...:>.:>,,:!:.?..

.+,.‘+:+”‘ ‘$,.?

Data Bus Enable (DBE) – This level sensitive i~[~t~$sthe

three-state control signal for the M PU data ~$~l:~yd will

enable the bus drivers when in the high st~:&$$@j9 Input is

TTL compatible; however in normal op~,atib~~$twould be

driven by the phase two clock. Durin&@n~~,K~ read cycle,

the data bus drivers will be disabled,’~~t~nal ly. When it is

desired that another device contr$PtR~&ata bus, such as in

Direct Memory Access (DMA)j+~k~@~ions, DBE should be

held low.

~t~

.>.:,:,.,,, ,x.

If additional data setup+p[+ho~d~?me is required on an MPU

write, the DB E

down ,~,~~ @n be decreased, as shown in

Figure 3 (DBE#@2\R:~~e~inimum down time for DBE is

tDB E as shown, ~~~.s}~ting D B E with respect to E, data

setup or hold t~,$@# be increased.

\\\$.

;>L:.,.?J~,

Bus Ay~i$~l~.(bA) – The Bus Available signal will nor-

mally ~%~ ~}$’low state; when activated, it will go to the

..,*.’:* Y

high.?ata~:+indicating that the microprocessor has stopped

* “’“’*’l+

and @,@tfhe address bus is available. This will occur if the

HALT~ne is in the low state or the processor is in the WAIT

state as a result of the execution of a WAIT instruction. At

such time, all three-state output drivers will go to their off

state and other outputs to their normally inactive level. The

processor is removed from the WAIT state by the occurrence

of a maskable (mask bit I = O) or nonmaskable interrupt, This

output is capable of driving one standard TTL load and

30 pF. If TSC is in the high state, Bus Available will be low,

Read/Write (R/~) – This TTL compatible output signals

the peripherals and memory devices wether the MPU is in a

@

MOTOROLA

Read (high) or Wrile (low) state, The normal standby state of

this signal is Read (high). Three-State Control going high will

turn Read/Write to the off (high impedance) state. Also,

when the processor is halted, it will be in the off state. This

output is capable of drivina one standard TTL Ioa&?iqnd

90 pF.

~+,r+i~ .:}

RESET – The RESET input is used to rese~&}N~&~rt the

M PU from a power down condition resulti~~,jf~% a power

failure or initial start-up of the processor,+:~@l%~i&el sensitive

input can also be used to reinitialize t,$~~~~~ne

at any time

after start-up.

.)’ k%}?*

:t:;l,\ \

If a high level is detected in th~ Inpw; this will signal the

MPU to begin the reset seqe~$~. During the reset se-

quence, the contents of th,~?%f$wb locations (FFFE, FFFF)

in memory will be loade@{~~&,Jtie Program Counter to point

to the beginning of..,$~b.:wet routine. During the reset

~.\J~t.~,,~y..

routine, the interrupt ~s~ bit is set and must be cleared

under program c~~ol, before the M PU can be interrupted by

IRQ. While ‘K%Jk’’low

(assuminga minimum of8 clock

cycles have ~Jcc~$r8d) the MPU output signals will be in the

followinqj$&MVMA= low, BA= low, Data Bus= high im-

peda~~e,>~~~= high (read state), and the Address Bus will

con$&8 the ‘reset address FFFE. Figure 8 illustrates a power

?}4

&“~q@~nce using the RESET control line. After the power

~i.

~,P@ reaches 4.75 V, a minimum of eight clock cycles are

?$:jlj$~qtiired for the processor to stabilize in preparation for

‘~trestarting. During these eight cycles, VMA will be in an in-

.lp~

determinate state so any devices that are enabled by VMA

which could accept a false write during this time (such as

battery-backed RAM) must be disabled until VMA is forced

low after eight cycles. RESET can go high asynchronously

with the system clock any time after the eighth cycle.

RESET timing is shown in Figure 8. The maximum rise and

fall transition times are specified by tpcr and tpcf. If RESET

is high at tpcs (processor control setup time), as shown in

Figure 8, in any given cycle then the restart sequence will

begin on the next cycle as shown. The RESET control line

may also be used to reinitialize the MPU system at any time

during its operation. This is accomplished by pulsing RESET

low for the duration of a minimum of three complete 42

cycles. The RESET pulse can be completely asynchronous

with the MPU system clock and will be recognized during 42

if setup time tpcs is met.

Interrupt Request (~Q) – This level sensitive input re-

quests that an interrupt sequence be generated within the

machine. The processor will wait until it completes the cur-

rent instruction that is being executed before it recognizes

the request. At that time, if the interrupt mask bit in the Con-

dition Code Register is not set, the machine will begin an in-

terrupt sequence. The Index Register, Program Counter, Ac-

cumulators, and Condition Code Register are stored away on

the stack. Next, the MPU will respond to the interrupt re-

quest by setting the interrupt mask bit high so that no further

interrupts may occur. At the end of the cycle, a 16-bit ad-

dress will be loaded that points to a vectoring address which

is located in memory locations FFF8 and FFF9. An address

loaded at these locations causes the MPU to branch to an in-

terrupt routine in memory. Interrupt timing is shown in

Figure 9.

Semiconductor Products Inc.

7