Spartan-3 FPGA: 解决LVDS信号倒相的PCB布局策略

需积分: 0 196 浏览量

更新于2024-08-01

1

收藏 300KB PDF 举报

“本文主要介绍了在Spartan-3 FPGA系列中如何高效地处理LVDS信号的PCB布局,特别是在遇到信号倒相问题时的解决方案。通过在接收器数据通路中添加倒相器,设计者可以避免大量使用过孔,同时解决因PCB迹线交换导致的问题,无需重新设计PCB。”

在Spartan-3 FPGA系列的设计中,LVDS(Low Voltage Differential Signaling)信号的正确布局至关重要,因为它直接影响到信号完整性和系统的性能。LVDS是一种高速、低功耗的差分信号传输标准,通常用于减少噪声影响和提高数据传输速率。然而,在PCB布线过程中,由于各种原因,LVDS信号的正负极引脚可能会被错误地交换,导致信号倒相,从而影响系统工作。

传统的解决方法是通过增加过孔来纠正这种倒相,但这会增加PCB的复杂性,降低信号质量,并可能导致设计成本增加。针对这一问题,本应用指南提出了一种创新的方法,即在接收器数据通路中内置一个倒相器。这样做不仅可以避免大量使用过孔,而且可以在不改变现有PCB布局的前提下解决迹线交换问题。

具体来说,如果在PCB上正极引脚错误地连接到了接收器的负极引脚,负极引脚连接到了正极,那么可以通过FPGA内部的逻辑来补偿这个倒相。Spartan-3 FPGA的结构允许设计者在接收器数据路径中插入一个倒相器,这样无论外部迹线如何交换,内部逻辑都能确保正确的信号流向。

这一技术的应用不仅限于接收器,也可以用于驱动器端。通过这种方式,设计者可以在不影响系统功能的前提下更灵活地布线,优化PCB布局,以达到最佳的信号完整性。

需要注意的是,如果设计中使用了DCM(Digital Clock Manager),这种方法只适用于数据线,而不适用于时钟线。因为时钟线的相位敏感性,交换时钟线可能会导致系统同步问题。此外,由于Spartan-3 FPGA的内部配置,用户无法直接访问用于选择真实输入或反相输入的多路复用器,它是由加载到器件的比特流初始化的。

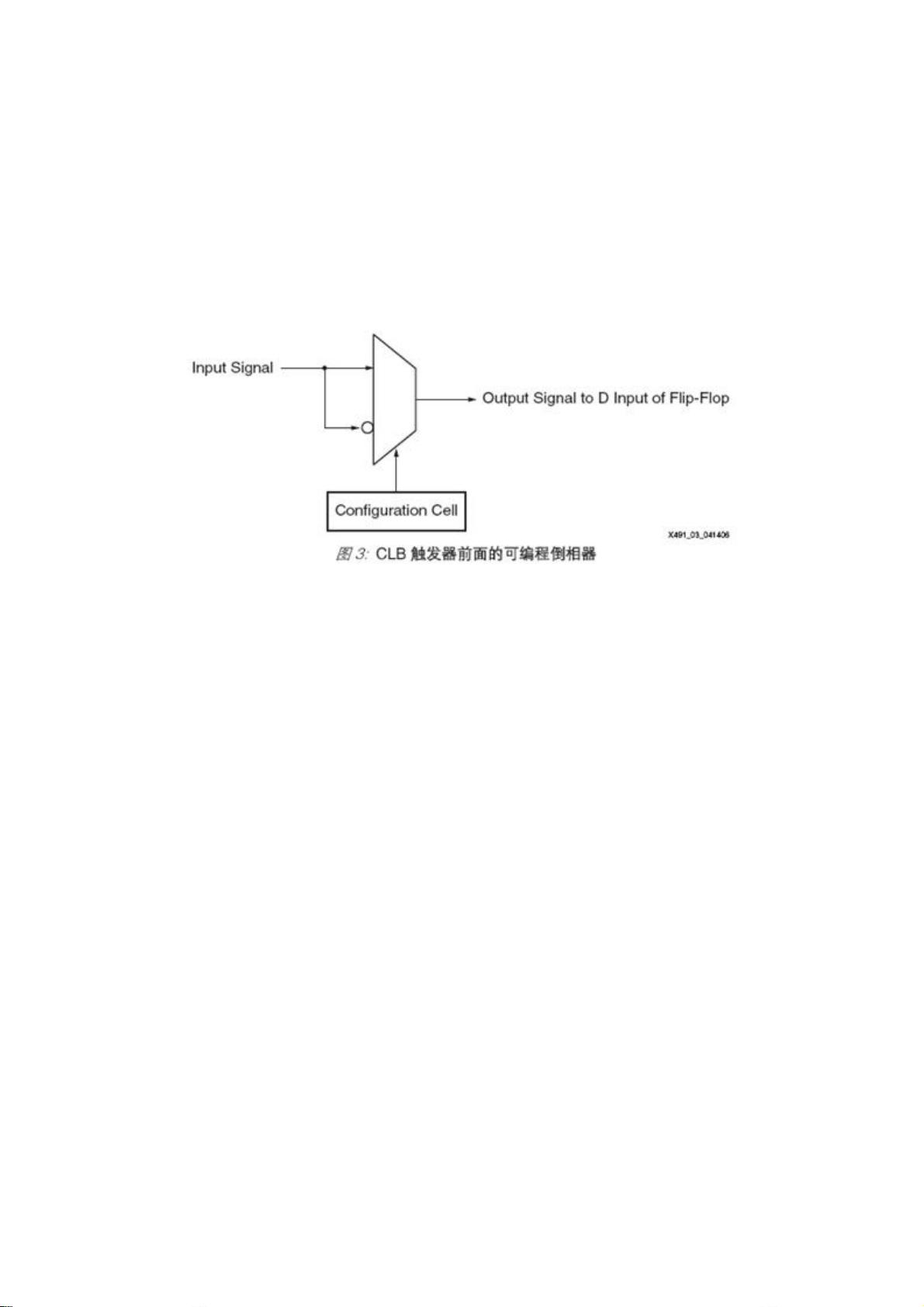

在实际应用中,倒相器的吸收有两种情况:一是直接驱动触发器输入时,FPGA的CLB触发器D输入路径上有一个多路复用器,可以选择真实输入或反相输入;二是当倒相器后面紧跟着逻辑函数时,倒相器可以直接被逻辑门吸收,如在执行“B = ~A”之后紧接着“D = B AND C”的逻辑操作。

Spartan-3 FPGA系列通过提供内置的倒相器功能,为高速PCB设计提供了一种灵活且高效的方法,以应对LVDS信号倒相问题,降低了设计的复杂性和成本,同时保证了系统的可靠性和性能。

2020-08-14 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

2024-11-06 上传

2022-04-22 上传

2019-07-09 上传

2022-03-09 上传

2011-03-01 上传

yk00110011

- 粉丝: 2

- 资源: 35

最新资源

- Python中快速友好的MessagePack序列化库msgspec

- 大学生社团管理系统设计与实现

- 基于Netbeans和JavaFX的宿舍管理系统开发与实践

- NodeJS打造Discord机器人:kazzcord功能全解析

- 小学教学与管理一体化:校务管理系统v***

- AppDeploy neXtGen:无需代理的Windows AD集成软件自动分发

- 基于SSM和JSP技术的网上商城系统开发

- 探索ANOIRA16的GitHub托管测试网站之路

- 语音性别识别:机器学习模型的精确度提升策略

- 利用MATLAB代码让古董486电脑焕发新生

- Erlang VM上的分布式生命游戏实现与Elixir设计

- 一键下载管理 - Go to Downloads-crx插件

- Java SSM框架开发的客户关系管理系统

- 使用SQL数据库和Django开发应用程序指南

- Spring Security实战指南:详细示例与应用

- Quarkus项目测试展示柜:Cucumber与FitNesse实践