微机原理与接口技术:总线驱动与竞争解析

需积分: 10 198 浏览量

更新于2024-07-30

收藏 873KB PDF 举报

"微机原理及接口技术的课后答案,包含各章节详解,重点讨论了总线的驱动与控制问题,旨在帮助学习者深入理解这门课程中的关键概念"

在微机原理及接口技术的学习中,总线是连接各个硬件组件的重要通道。本资料主要涉及第4章关于总线的内容,尤其是总线的驱动与控制,这是确保系统稳定运行的关键因素。

首先,我们来看"总线竞争"这一现象。当同一总线上有多个器件同时试图向总线输出数据时,就会出现总线竞争。例如,在传统的TTL逻辑中,如果两个或更多器件在同一时刻都尝试将状态写入总线,可能会导致总线电平处于不确定的状态,这不仅可能导致数据传输错误,严重时还可能损坏器件。为了避免这种情况,可以采用集电极开路(OC)输出,也称为线与逻辑。在这种情况下,即使多个器件同时输出,只要至少有一个器件为低电平,总线就能保持低电平状态。然而,如果所有器件都试图输出高电平,总线上的信号将会被拉低,导致信息丢失。

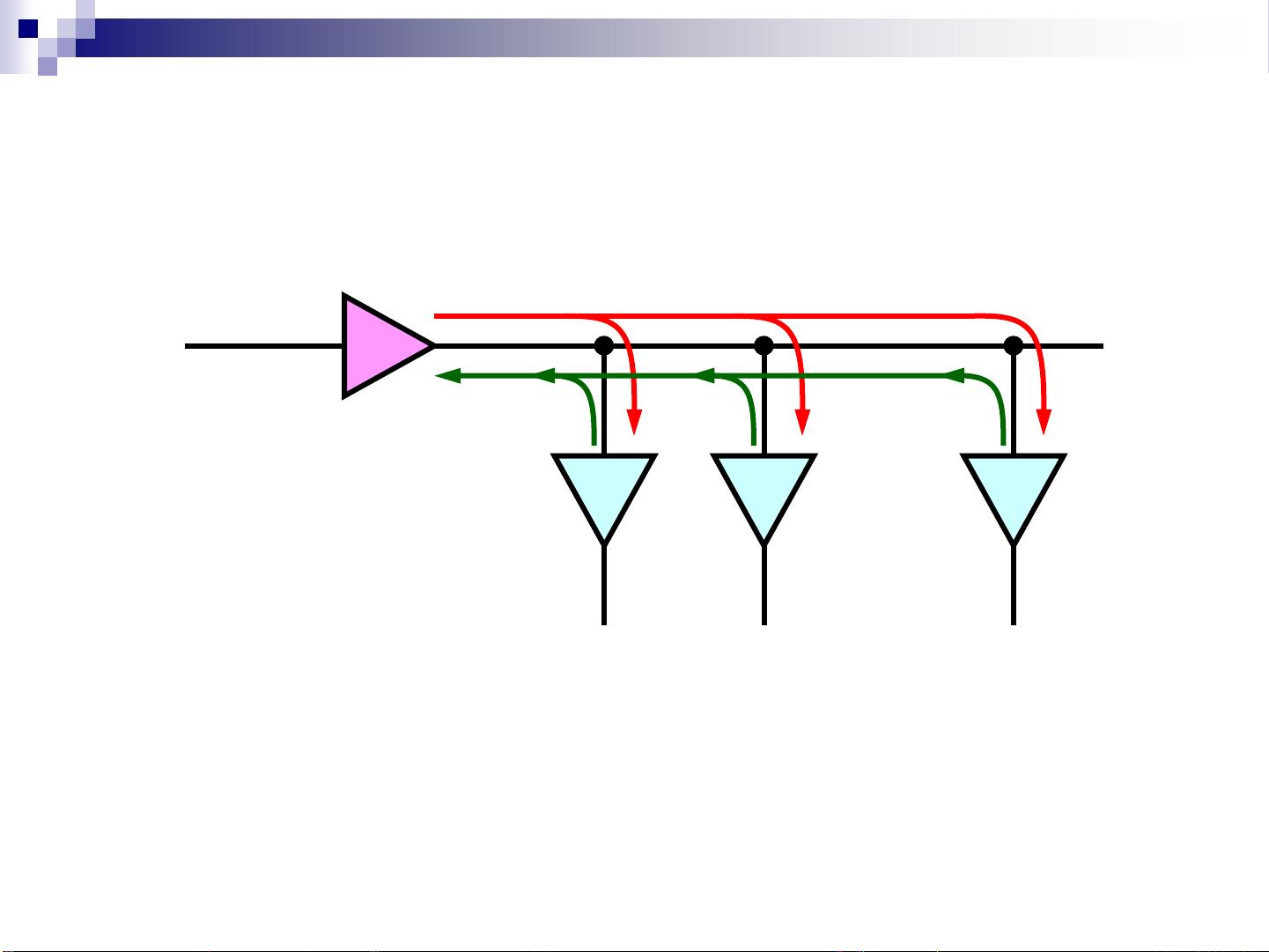

为了解决这个问题,通常会使用三态电路。三态门(Tri-state Gate)允许控制信号来开启或关闭其输出,确保在任何时候只有一个器件能够驱动总线,从而消除竞争条件,确保数据传输的准确性和设备的安全性。

接下来,我们讨论"总线的负载"。总线的负载指的是连接到总线上的所有器件所消耗的电流。CPU必须能够提供足够的电流来驱动这些负载,确保每个器件都能正常工作。对于非集电极开路(OC)门,当输出为高电平时,驱动门需要提供足够的IOH电流,而在输出为低电平时,则需要提供足够的IOL电流。对于OC门,电流流向则相反,从负载门流向驱动门。每个器件的电流需求都有最大值,设计时必须考虑所有连接器件的最大电流需求之和,以保证总线的驱动能力。

在选择和设计总线系统时,必须参照器件手册提供的最大电流值,确保输出高电平时驱动门的IOH大于或等于所有负载门IIH的最大值之和,同样,输出低电平时,驱动门的IOL也要大于或等于所有负载门IIL的最大值之和。这样,才能确保总线在承受最大负载时仍能稳定地传输数据。

总结来说,理解并掌握总线竞争的解决策略以及如何计算和满足总线的直流负载需求,对于设计和维护微机系统的可靠性至关重要。通过深入学习和理解这些知识点,我们可以更好地设计和优化计算机系统的硬件架构,以实现高效的数据交换和系统的稳定运行。

2011-06-27 上传

2021-09-21 上传

2009-10-16 上传

2013-09-11 上传

2024-12-25 上传

qsl1010

- 粉丝: 0

- 资源: 1

最新资源

- FACTORADIC:获得一个数字的阶乘基数表示。-matlab开发

- APIPlatform:API接口平台主页接口调用网站原始码(含数十项接口)

- morf源代码.zip

- 参考资料-附件2 盖洛普Q12 员工敬业度调查(优秀经理与敬业员工).zip

- MyJobs:Yanhui Wang 使用 itemMirror 和 Dropbox 管理作业的 SPA

- SiFUtilities

- PrivateSchoolManagementApplication:与db连接的控制台应用程序

- python-sdk:MercadoLibre的Python SDK

- Docket-App:笔记本Web应用程序

- Crawler-Parallel:C语言并行爬虫(epoll),爬取服务器的16W个有效网页,通过爬取页面源代码进行确定性自动机匹配和布隆过滤器去重,对链接编号并写入url.txt文件,并通过中间文件和三叉树去除掉状态码非200的链接关系,将正确的链接关系继续写入url.txt

- plotgantt:从 Matlab 结构绘制甘特图。-matlab开发

- 【精品推荐】智慧体育馆大数据智慧体育馆信息化解决方案汇总共5份.zip

- tsu津

- houdini-samples:各种Houdini API的演示

- parser-py:Python的子孙后代工具

- proton:Vue.js的无渲染UI组件的集合