解决冲突的Verilog流水线设计与MIPS单内存挑战

需积分: 13 23 浏览量

更新于2024-07-18

收藏 1.48MB PDF 举报

在计算机架构领域,流水线技术是提高处理器性能的关键概念,特别是在MIPS(Message Passing Interface for Superscalar Processors)流水线设计中。流水线的主要目标是通过将执行过程分解为一系列连续的步骤,以减少指令周期时间并提高处理能力。然而,流水线设计也带来了挑战,特别是资源冲突问题。

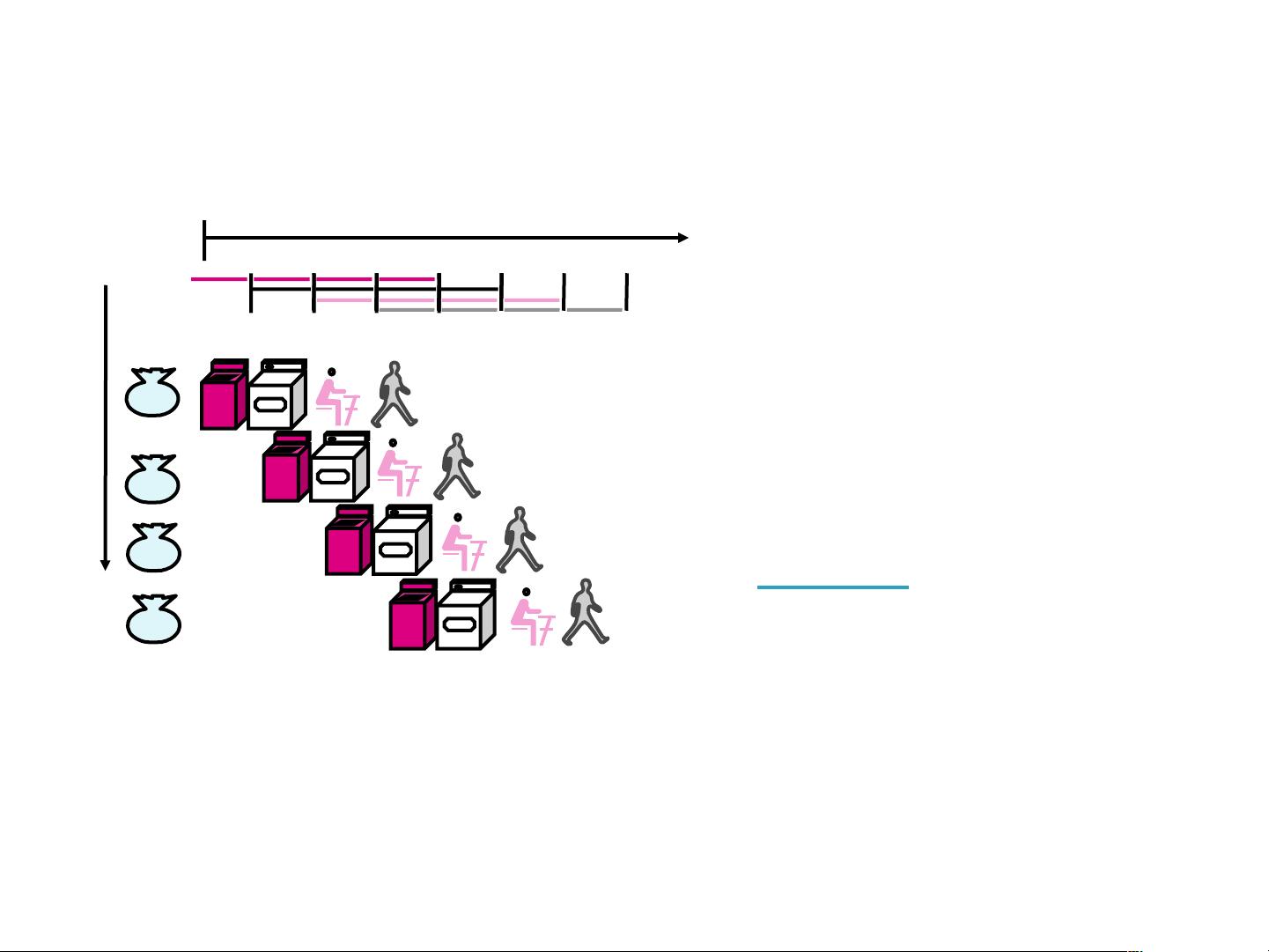

首先,流水线的基本原理是将一个复杂任务分解成多个独立且可以并行执行的阶段。例如,在MIPS流水线中,这可能包括取指(Instruction Fetch, IF)、解码(Instruction Decode, ID)、执行(Execution, EX)、访存(Memory Access, MA),以及写回(Write Back, WB)。每个阶段都有其特定的硬件组件,如指令寄存器、算术逻辑单元(ALU)和数据存储器等。

在设计过程中,一个常见的挑战是负载/存储冲突(Load/Store Conflict),它发生在指令流水线中,当一条指令需要从内存读取数据的同时,另一条指令正在试图写入同一地址。这种情况下,执行阶段(EX)会因为等待数据而停滞,导致整个流水线出现"bubble"(空转周期),从而降低了效率。为解决这个问题,通常采用多级存储结构,比如在单级流水线中,单独的L1指令缓存(L1 Instruction Cache, L1 I$)和L1数据缓存(L1 Data Cache, L1 D$)被设计出来,它们分别负责指令和数据的高速缓存,确保数据和指令的独立访问。

在设计一个单周期处理器时,遵循五个关键步骤:

1. 分析指令集:理解指令的执行流程,确定数据路径的需求。

2. 选择和配置数据路径组件:确定所需的运算部件(如ALU)、控制逻辑、以及如何同步各个阶段的时钟。

3. 组装数据路径:确保所有组件按照流水线模式协同工作。

4. 设计控制逻辑:分析每个指令的实现,确定控制点,以便有效地管理寄存器传输。

5. 设计控制和数据电路:根据逻辑方程制定电路设计,并集成到整体系统中,包括输入输出接口和内存访问逻辑。

总结来说,流水线技术是一项复杂的计算机体系结构设计手段,通过优化资源分配和解决冲突,如采用多级缓存来处理数据和指令的独立性,可以显著提升处理器性能。然而,这需要对指令集特性、硬件组件和流水线操作有深入的理解,并且要能够灵活地应用到具体的设计实践中。

2018-12-27 上传

2021-04-14 上传

2019-01-09 上传

2021-09-24 上传

2020-05-19 上传

2011-06-06 上传

2018-07-03 上传

2012-06-12 上传

2010-05-05 上传

小烦丶

- 粉丝: 0

- 资源: 1

最新资源

- 全国江河水系图层shp文件包下载

- 点云二值化测试数据集的详细解读

- JDiskCat:跨平台开源磁盘目录工具

- 加密FS模块:实现动态文件加密的Node.js包

- 宠物小精灵记忆配对游戏:强化你的命名记忆

- React入门教程:创建React应用与脚本使用指南

- Linux和Unix文件标记解决方案:贝岭的matlab代码

- Unity射击游戏UI套件:支持C#与多种屏幕布局

- MapboxGL Draw自定义模式:高效切割多边形方法

- C语言课程设计:计算机程序编辑语言的应用与优势

- 吴恩达课程手写实现Python优化器和网络模型

- PFT_2019项目:ft_printf测试器的新版测试规范

- MySQL数据库备份Shell脚本使用指南

- Ohbug扩展实现屏幕录像功能

- Ember CLI 插件:ember-cli-i18n-lazy-lookup 实现高效国际化

- Wireshark网络调试工具:中文支持的网口发包与分析