深亚微米工艺下的Astro布局布线流程解析

需积分: 9 61 浏览量

更新于2024-07-22

收藏 2.42MB PDF 举报

"Astro布局布线流程的详细解析"

Astro布局布线流程是现代集成电路物理设计的关键步骤,尤其在深亚微米工艺下,电路的时序性能很大程度上取决于门间的连线延迟。Synopsys公司的Astro软件是业界广泛使用的物理设计工具,它提供了全面的物理设计解决方案,包括布局、布线以及时序优化,旨在确保设计的物理实现满足预设的性能指标。

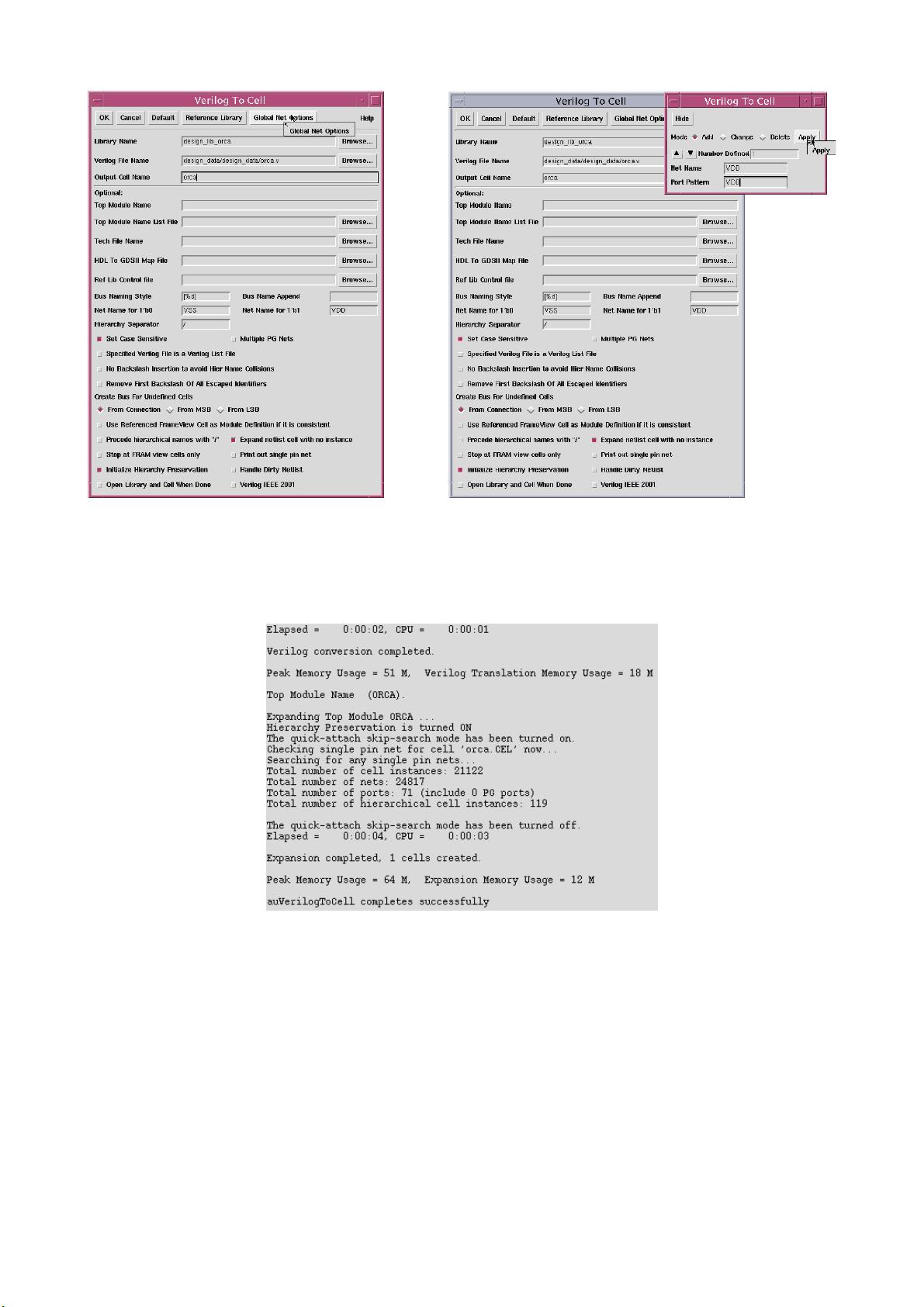

设计流程的第一步是**数据准备**。这个阶段需要以下几种关键输入文件:

1. **网表文件**:通常由Design Compiler(DC)生成,以Verilog (.v)格式存在。布局布线过程中,网表用于描述电路的逻辑结构和连接关系。

2. **时序约束文件(SDC)**:由前端工程师创建,以SDC格式存储,用于定义设计的时序要求。Astro需要精确的时钟定义,因此可能需要对从DC导出的SDC文件进行修改,确保时钟源明确指向网表中的具体时钟单元。

3. **参考库**:包含标准单元、IO单元和宏等,由Foundry提供。这些库文件定义了电路元件的物理形状和电气特性。

4. **TDF文件(Top Design File)**:定义PAD顺序和位置信息,对于芯片的外部接口布局至关重要。

5. **工艺tf文件(Technology File)**:由Foundry提供的工艺参数文件,定义了制造过程中的规则和限制。

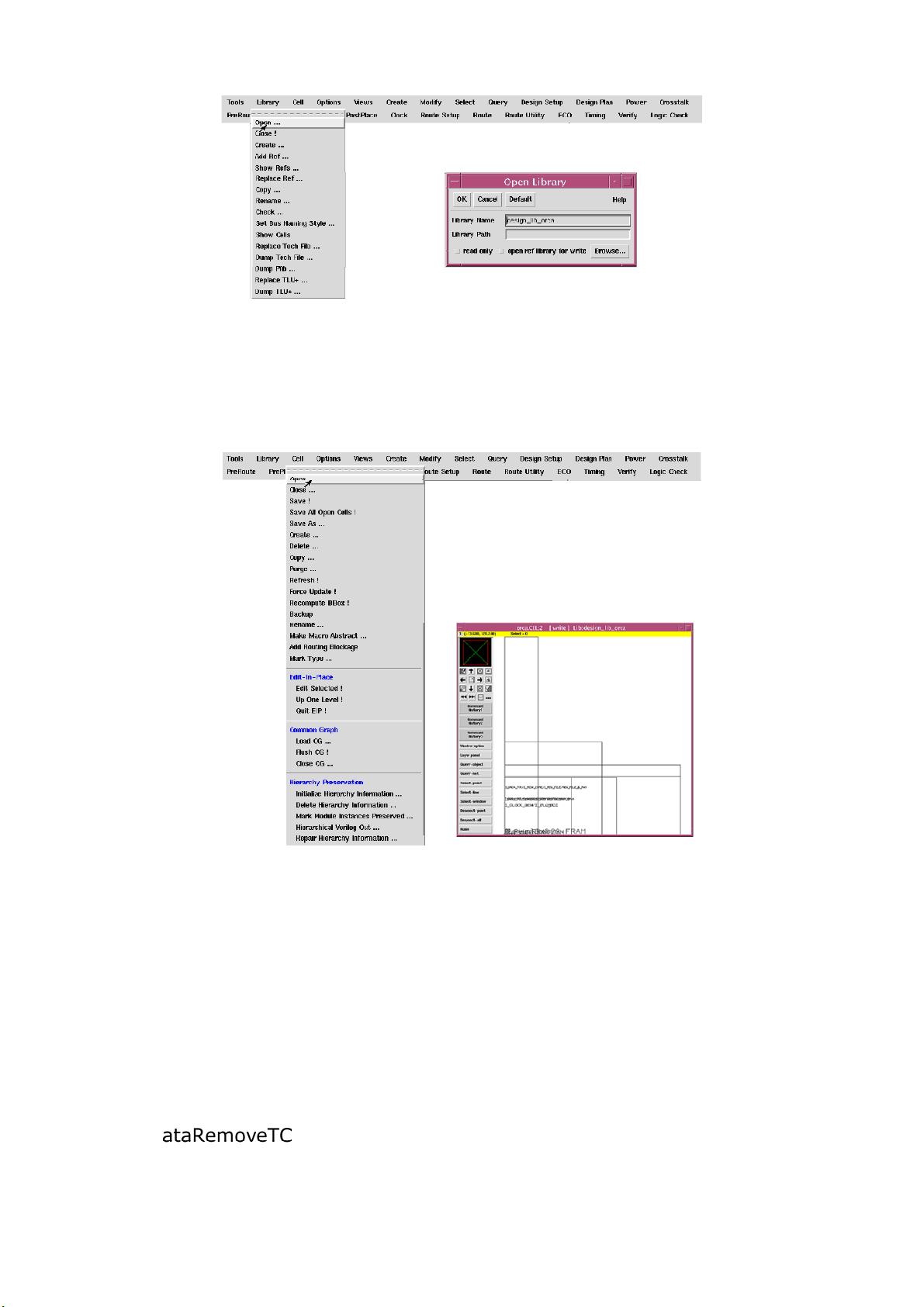

接下来,我们简要概述Astro的主要设计步骤:

1. **布局**:这一步涉及逻辑模块的放置,目标是优化逻辑门的物理位置,减少互连延迟并考虑散热、功耗等因素。

2. **时序预分析**:基于当前布局和时序约束,Astro评估设计的时序性能,以确定是否需要进一步优化。

3. **全局布线**:在初步布局的基础上,进行粗略的连线,形成全局的布线路径,初步解决信号的路由问题。

4. **局部布线和细节布线**:进一步细化布线,确保信号在最小化延迟的同时满足电气规则和设计规则。

5. **时序优化**:Astro通过移动门的位置或者调整布线路径来改进时序性能,确保满足预设的时序约束。

6. **寄生参数提取**:计算布线后的电容、电感等寄生效应,这些效应会影响电路的实际性能。

7. **后仿真和签核**:使用电路模拟器进行后仿真,验证物理设计是否符合功能和时序要求。

8. **输出GDSII**:最终的物理设计结果以GDSII格式输出,这是芯片制造厂接受的设计数据格式。

每个步骤都需要精确的设置和调优,Astro的复杂性在于它需要处理多个设计层面的问题,如性能、功耗和面积等,同时确保所有设计规则得以遵守。通过理解Astro的工作原理和流程,设计者能够更有效地驾驭这一强大的工具,实现高性能的集成电路设计。

2011-08-22 上传

2021-10-11 上传

2021-12-19 上传

2021-05-25 上传

2021-03-27 上传

2022-04-13 上传

2022-03-09 上传

charrasy

- 粉丝: 0

- 资源: 1

最新资源

- C语言快速排序算法的实现与应用

- KityFormula 编辑器压缩包功能解析

- 离线搭建Kubernetes 1.17.0集群教程与资源包分享

- Java毕业设计教学平台完整教程与源码

- 综合数据集汇总:浏览记录与市场研究分析

- STM32智能家居控制系统:创新设计与无线通讯

- 深入浅出C++20标准:四大新特性解析

- Real-ESRGAN: 开源项目提升图像超分辨率技术

- 植物大战僵尸杂交版v2.0.88:新元素新挑战

- 掌握数据分析核心模型,预测未来不是梦

- Android平台蓝牙HC-06/08模块数据交互技巧

- Python源码分享:计算100至200之间的所有素数

- 免费视频修复利器:Digital Video Repair

- Chrome浏览器新版本Adblock Plus插件发布

- GifSplitter:Linux下GIF转BMP的核心工具

- Vue.js开发教程:全面学习资源指南