二进制计数器详解:同步与异步,结构与应用

版权申诉

57 浏览量

更新于2024-06-26

收藏 4.21MB PPTX 举报

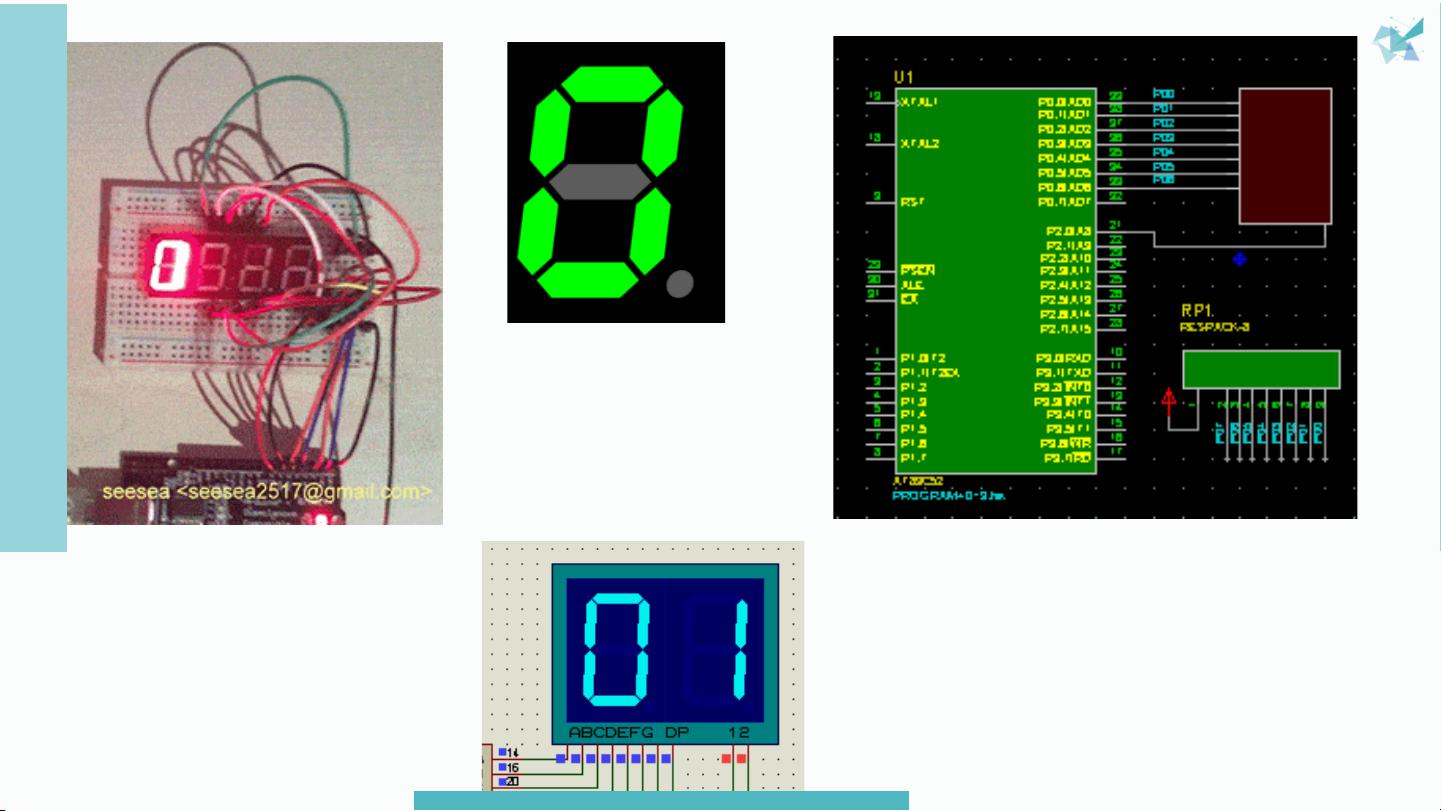

在数字电子技术中,二进制计数器占据着核心地位。二进制计数器是一种时序逻辑电路,其主要特点是具有记忆功能,通过触发器(如JK、D或T触发器)和门电路(如与非门、或非门等)的组合实现计数功能。对于8位的二进制计数器,需要8个触发器来分别存储每一位的状态,因为每个触发器代表二进制数的一个位。

计数器按照不同的标准可以分为不同的类别:

1. 按计数进制划分:主要有二进制计数器,遵循二进制数的运算规则;十进制计数器,适用于十进制数的计数;以及任意进制计数器,包括除二进制和十进制外的其他进制,如16进制、5进制等。尽管二进制计数器结构相对简单,但由于计算机技术的基础是二进制,因此其应用极为广泛。

2. 按计数方式区分:

- 加法计数器:随输入脉冲递增计数。

- 减法计数器:随输入脉冲递减计数。

- 加/减计数器:根据外部控制信号可以进行加计数或减计数,也称为可逆计数器。

- 特殊情况的计数器:在某些情况下,计数状态可能在特定条件下发生循环跳转,形成封闭的计数环。

3. 按触发器翻转的同步性划分:

- 异步计数器:计数脉冲仅作用于部分触发器,导致状态更新不一致,即各触发器的翻转时刻不同,需要关注每个触发器的有效时钟条件。

- 同步计数器:计数脉冲同时加到所有触发器的时钟输入端,保证所有触发器在相同的时间点翻转,使得状态更新完全同步。

异步二进制计数器是最基础的电路结构,通常由多个触发器串联组成,其中最低位触发器接收计数脉冲CP,它的输出作为高位触发器的时钟输入,形成逐位上升的计数序列。这种设计使得异步计数器简单易实现,常用于许多基本的数字逻辑系统中。

二进制计数器是数字电子技术中的基石,理解它们的工作原理、分类及其应用场景对于深入学习数字逻辑设计至关重要。无论是用于构建数字时钟、计数器应用、还是数据处理系统,掌握二进制计数器的构造和特性都是至关重要的。

174 浏览量

241 浏览量

129 浏览量

365 浏览量

297 浏览量