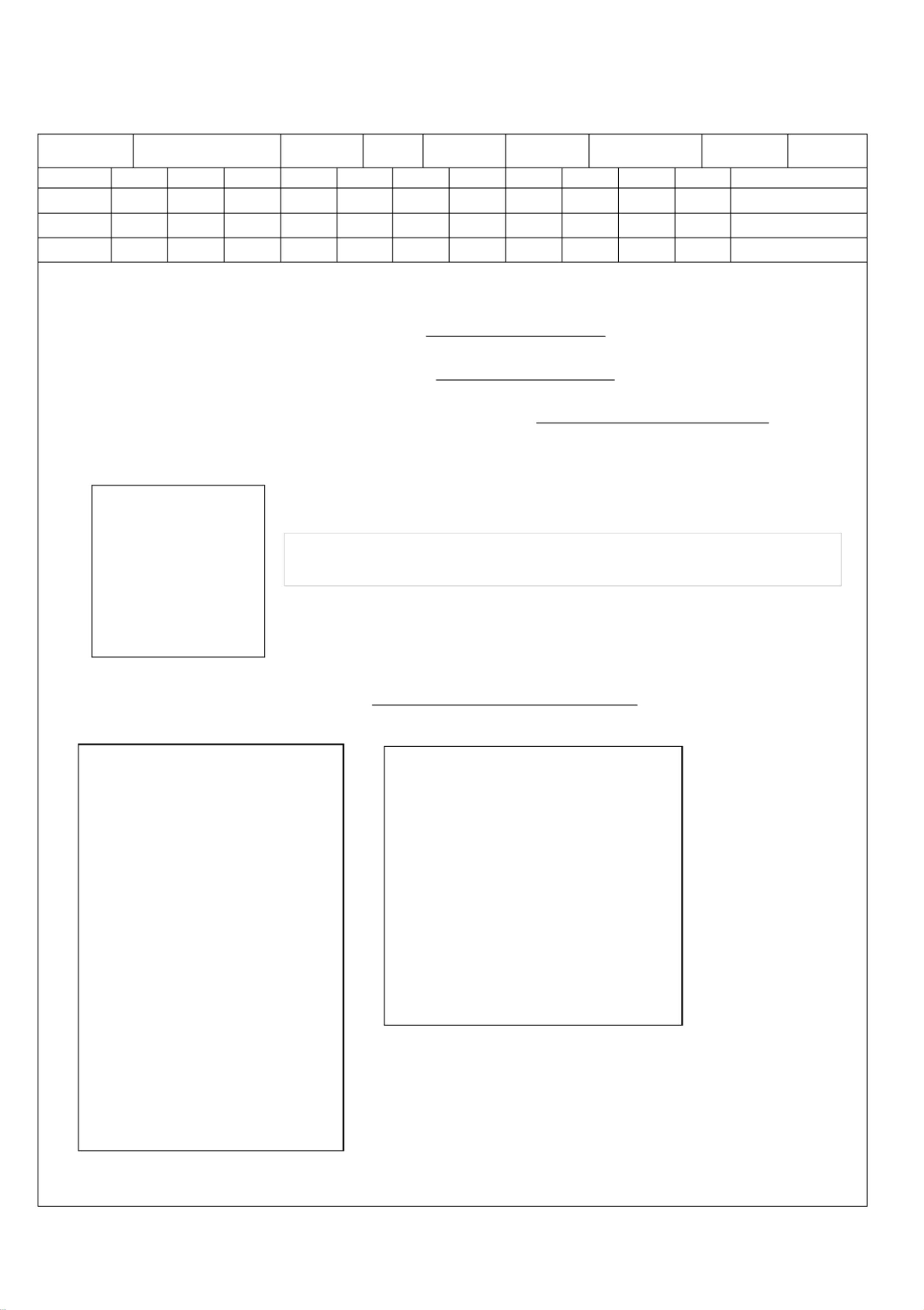

山东理工FPGA Verilog数字系统设计期末考卷

版权申诉

151 浏览量

更新于2024-08-13

收藏 160KB PDF 举报

本资源是一份山东理工大学《FPGA与Verilog数字系统设计》课程的期末考试题终稿,适用于09电子科技1、2专业的学生。考试性质为闭卷考试,时间为100分钟。题目涵盖了Verilog语言基础、逻辑运算、系统设计以及硬件描述语言的应用。

1. **Verilog基础**:题目中涉及了Verilog的`$display`函数,用于在仿真时显示数据。例如,第1题展示了如何使用该函数来展示二进制数值的或操作结果,`$display("result=%b", 5'b01010|5'b11111)`,这要求考生掌握Verilog中的位操作符。

2. **逻辑运算**:第2题要求理解逻辑非(`!`)运算符和按位或(||)运算符,`$display("result=%b", !(4'b1110||4'b1001))`,测试的是考生对这些基本逻辑运算的理解和使用。

3. **硬件描述语言应用**:第3题涉及Verilog结构化设计,通过`{}`操作符组合变量,`$display("result=%b", {a, b, a+b})`,考察了数据的并行赋值和组合逻辑操作。

4. **时序逻辑设计**:第4题要求考生根据给定的描述画出S信号波形图,这可能涉及到时序电路的设计和分析,需要理解Verilog中的事件驱动(`always @(posedge clk)`或`posedge`等)语句。

5. **系统模块设计**:`alu`模块展示了如何用Verilog实现一个基本算术逻辑单元,包括`alu`和`top_alu`模块。`alu`模块实现了加减乘除和取反操作,而`top_alu`模块则展示了如何将这些模块集成到一个完整的设计中,并通过`$display`输出结果。

6. **时间和仿真控制**:`#10 $display("ouput=%d", out);`和`#10 $stop;`是时间延迟和停止仿真指令,用于模拟实际系统的行为。

这份试题全面覆盖了Verilog语言的基本语法、逻辑运算、硬件描述以及系统级设计,旨在测试学生的编程能力、逻辑思维和硬件实现技能。对于准备参加此类考试的学生来说,理解和解答这些问题有助于提升其在FPGA和Verilog设计方面的实践能力。

2022-01-23 上传

126 浏览量

2021-09-29 上传

2024-05-13 上传

108 浏览量

1019 浏览量

2021-09-30 上传

149 浏览量

cjd13107639592

- 粉丝: 1

- 资源: 5万+

最新资源

- 易语言学习-扩展功能支持库一 (3.0#0版)逆向源代码.zip

- 【游戏开发】 phthon导出excel成lua表(可单独,可批量enter直接批量) exporExcelConfig.zip

- intro-to-programming-exercises

- Packt.Matplotlib.3.0.Cookbook.rar 2018年最新版本,epub格式,高清附图,文字可拷贝

- 添加sql server数据库分区.zip

- 简易波形发生器,51出品-电路方案

- jquerycsv:需要创建或解析CSV的东西所以使这个

- django-sqlalchemy:目前仅基于SQLalchemy核心1.42.0构建的Django ORM,用于将SQLAlchemy与Django 3.1+ PostgreSQL 12.1无缝集成

- gardenmuseumleicandrut.github.io:地点

- oldfiel.rar

- 易语言学习-Sqlite3支持库 - 公开测试版 [2012-5-2].zip

- NumHits-开源

- vcredist_x64_2020.zip

- django-text:使用Django的人类直观文本编辑

- 适用于Python的灵活而强大的数据分析/操作库,提供与R data.frame对象,统计函数等类似的标记数据结构-Python开发

- building+applications+with+spring5+and+vuejs2.rar