12 www.xilinx.com Clocking Resources

UG362 (v2.5) January 24, 2014

Chapter 1: Clocking Resources

Global Clock Inputs

Virtex-6 FPGAs contain specialized global clock input locations for use as regular user

I/Os if not used as clock inputs. There are eight global clock inputs per device. Clock

inputs can be configured for any I/O standard, including differential I/O standards. Each

clock input can be either single-ended or differential. All eight clock inputs can be

differential if desired. When used as outputs, global clock input pins can be configured for

any output standard. Each global clock input pin supports any single-ended output

standard or any output differential standard. The global clock inputs are distributed across

four banks in the inner I/O columns for the most flexible selection of I/O standards.

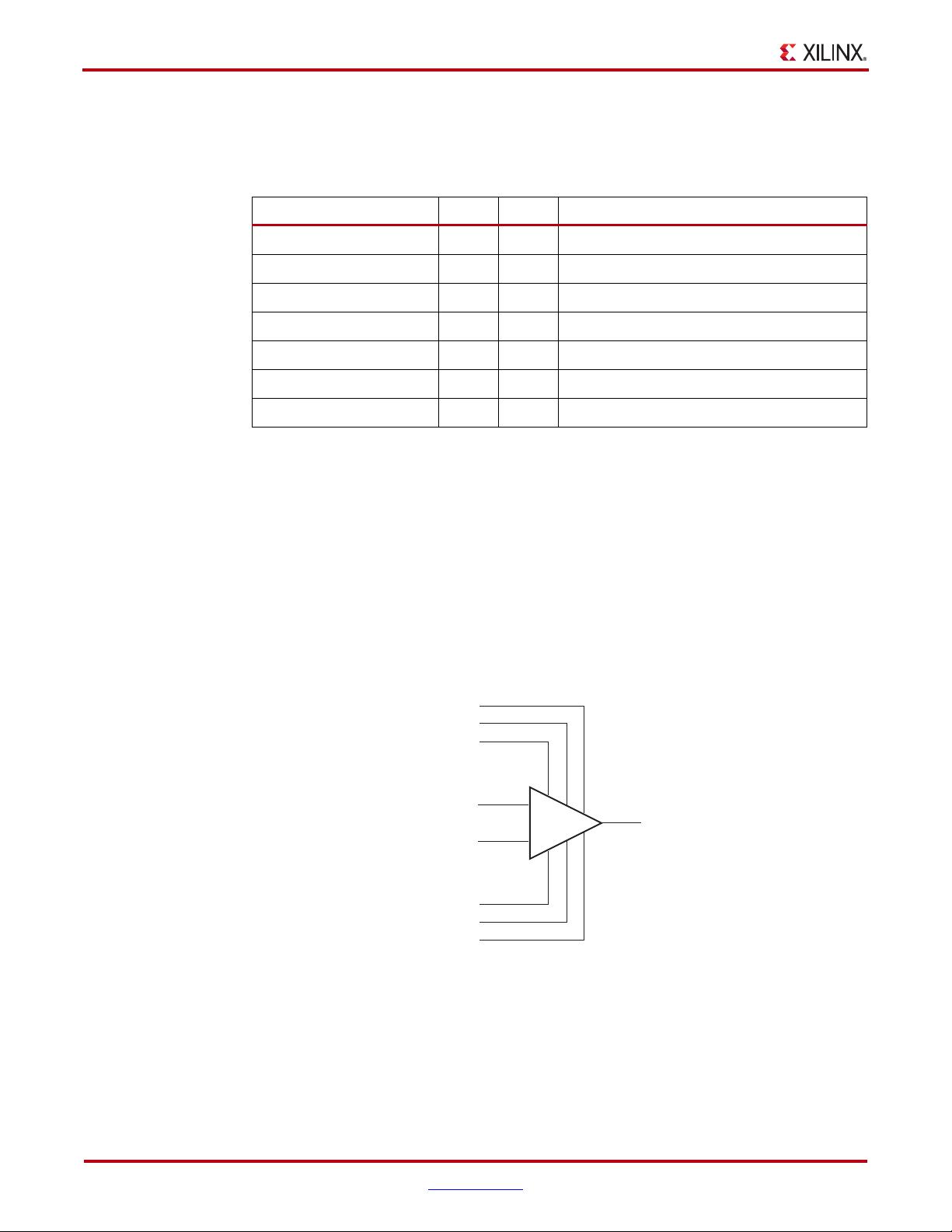

Global Clock Input Buffer Primitives

The primitives in Table 1-1 are different configurations of the input clock I/O input buffer.

These two primitives work in conjunction with the Virtex-6 FPGA SelectIO™ resource by

setting the IOSTANDARD attribute to the desired standard. Refer to Chapter 1 of the

Virtex-6 FPGA SelectIO Resources User Guide for a complete list of possible I/O standards.

Clock Gating for Power Savings

The Virtex-6 FPGA clock architecture provides a straightforward means of implementing

clock gating for the purposes of powering down portions of a design. Most designs contain

several unused BUFGCE resources. A clock can drive a BUFGCE input, and a BUFGCE

output can drive distinct regions of logic. For example, if all the logic that is required to

always be operating is constrained to a few clocking regions, then the BUFGCE output can

drive those regions. Toggling the enable of the BUFGCE provides a simple means of

stopping all dynamic power consumption in the logic regions available for power savings.

The Xilinx Power Estimator (XPE) or the Xilinx Power Analyzer (XPower) tools are used to

estimate power savings. The difference is calculated by setting the frequency on the

corresponding clock net to 0 MHz or providing the appropriate stimulus data to the tool.

Global Clock Buffers

There are 32 global clock buffers in every Virtex-6 device. A global clock input can directly

connect from the P-side of the differential input pin pair to any global clock buffer input.

There are eight global clock pin inputs. The top/bottom half rules from previous Virtex

architectures no longer apply. Each differential global clock pin pair can connect to either a

differential or single-ended clock on the PCB. If using a single-ended clock, then the P-side

of the pin pair must be used because a direct connection only exists on this pin. For pin

naming conventions please refer to the Virtex-6 FPGA Packaging and Pinout Specification. If

a single-ended clock is connected to the P-side of a differential pin pair, then the N-side can

not be used as another single-ended clock pin. However, it can be used as a user I/O.

MMCMs in the top half of the device can only drive the BUFGs in the top half of the device

and MMCMs in bottom half can only drive BUFGs in the bottom half. Similarly, only

BUFGs in the same half of the device can be used as feedback to the MMCMs in the same

half of the device.

Table 1-1: Clock Buffer Primitives

Primitive Input Output Description

IBUFG I O Input clock buffer for single-ended I/O

IBUFGDS I, IB O Input clock buffer for differential I/O