Xilinx FPGA Aurora 高速串行通信教程

需积分: 17 153 浏览量

更新于2024-07-18

收藏 1.15MB PDF 举报

"fpga arurora 开发教程,讲解如何使用XILINx Ip核进行高速串行通信的教程"

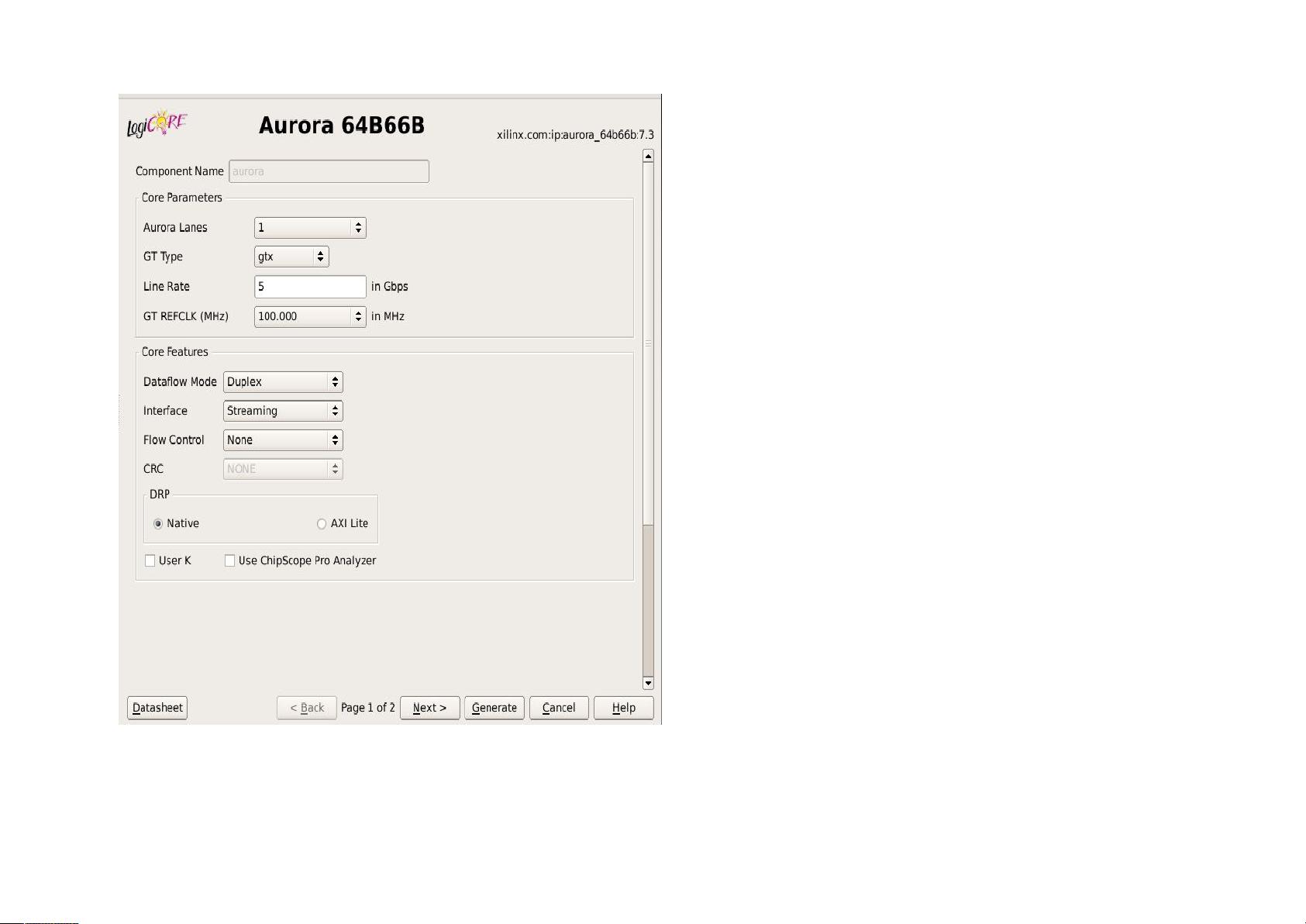

在XILINx FPGA开发中,Aurora是一种专有的高速串行通信协议,用于实现并行数据到串行数据的转换,并利用FPGA内置的高速收发器进行高效传输。它支持两个FPGA之间的全双工通信,即在同一时刻既能发送数据也能接收数据。Aurora协议还包含CRC(循环冗余校验)功能,用于检测数据传输中的错误,但本教程将主要关注如何快速上手使用Aurora IP核。

首先,了解基本概念至关重要。在Aurora术语中,“lane”是一个关键概念。Lane可以理解为并行数据流中的独立通道,每个通道独立地进行数据传输。例如,如果选择4个lanes,数据会被分为四部分同时传输,从而提高整体的数据传输速率。在本教程中,我们将选择1个lane进行操作,这已经足够满足许多基础应用的需求。当然,根据实际需求,最多可以选择16个lanes,但这可能需要更复杂的布线和更高的硬件资源。

Aurora IP核的配置中,"GTtype"是指通用收发器类型,通常默认为GTX,这是一种高速串行接口技术,用于实现FPGA之间的高速数据传输。GTX收发器的设计是为了处理高速串行数据,因此在创建IP核时,你无需更改这一选项。

"LineRate"是指数据传输速率,它是衡量Aurora接口性能的主要指标。你需要根据你的FPGA型号、电路板上的硬件资源以及实际应用需求来选择合适的line rate。选择合适的line rate确保了数据传输的效率和稳定性。

"GTREFCLK"是参考时钟,对于高速通信来说,这是一个至关重要的参数。参考时钟需要来自高质量的晶振,以保证数据传输的精度和可靠性。使用低质量的时钟源可能会导致数据同步问题和传输错误,因此在实际设计中,必须遵循官方文档的指导,使用推荐的高质量晶振。

在理解了这些基本概念后,你就可以开始创建和配置Aurora IP核了。首先,在IP核生成界面中搜索"Aurora",然后按照教程中介绍的步骤进行操作。这通常涉及到选择lane数量、配置line rate、设置参考时钟等参数。一旦IP核配置完成,你就可以将其集成到你的FPGA设计中,与DDR3控制器等其他组件一起工作,实现高速、可靠的通信。

在实际项目中,你需要进行硬件连接、时序约束、仿真验证等多个步骤,以确保Aurora IP核能正常工作。在DDR3教程的基础上,你应该已经掌握了基本的IP核使用方法和VHDL/Verilog编程技巧,这将帮助你更快地上手Aurora。记得在设计过程中,不断地进行测试和调试,以确保系统的稳定性和性能满足设计要求。

Aurora协议是XILINx提供的一种强大工具,用于实现FPGA之间的高速串行通信。通过理解lane的概念,选择合适的GTtype和LineRate,以及使用高质量的参考时钟,你可以有效地利用Aurora IP核构建高效、可靠的通信系统。在实践中,不断学习和实践,将使你成为更加熟练的FPGA开发者。

6870 浏览量

2025-03-12 上传

2025-03-12 上传

qq_37835821

- 粉丝: 0

最新资源

- 掌握Android ListView滑动删除实现的源码解析

- 桌面美化新选择:绿色小插件介绍

- MFight:新颖的1V1在线对战枪战游戏

- 实现Qt与KDE应用AVIF图像读写的新插件

- R语言数据可视化教程与习题集

- MyEclipse实现JS自动提示功能详解

- 全面解析X102 51学习板元器件及使用手册

- VC++实现跨程序按钮事件响应机制

- Halcon图像处理:缺陷检测差分法实现

- Linux下的项目启动脚本命令行工具

- 未使用文件webpack插件:高效识别未编译文件

- JavaScript实现复选框全选、反选和取消选中功能

- 地级市行政区划shp文件的地理信息应用

- DIV+CSS网页布局商业案例精析与代码实战

- 链表操作指南:创建、清空、删除与插入

- Sublime Text 6新特性:高级Vim模拟器发布