Zynq-7000 APSoC DDR3内存接口用户指南

需积分: 9 14 浏览量

更新于2024-07-21

1

收藏 18.12MB PDF 举报

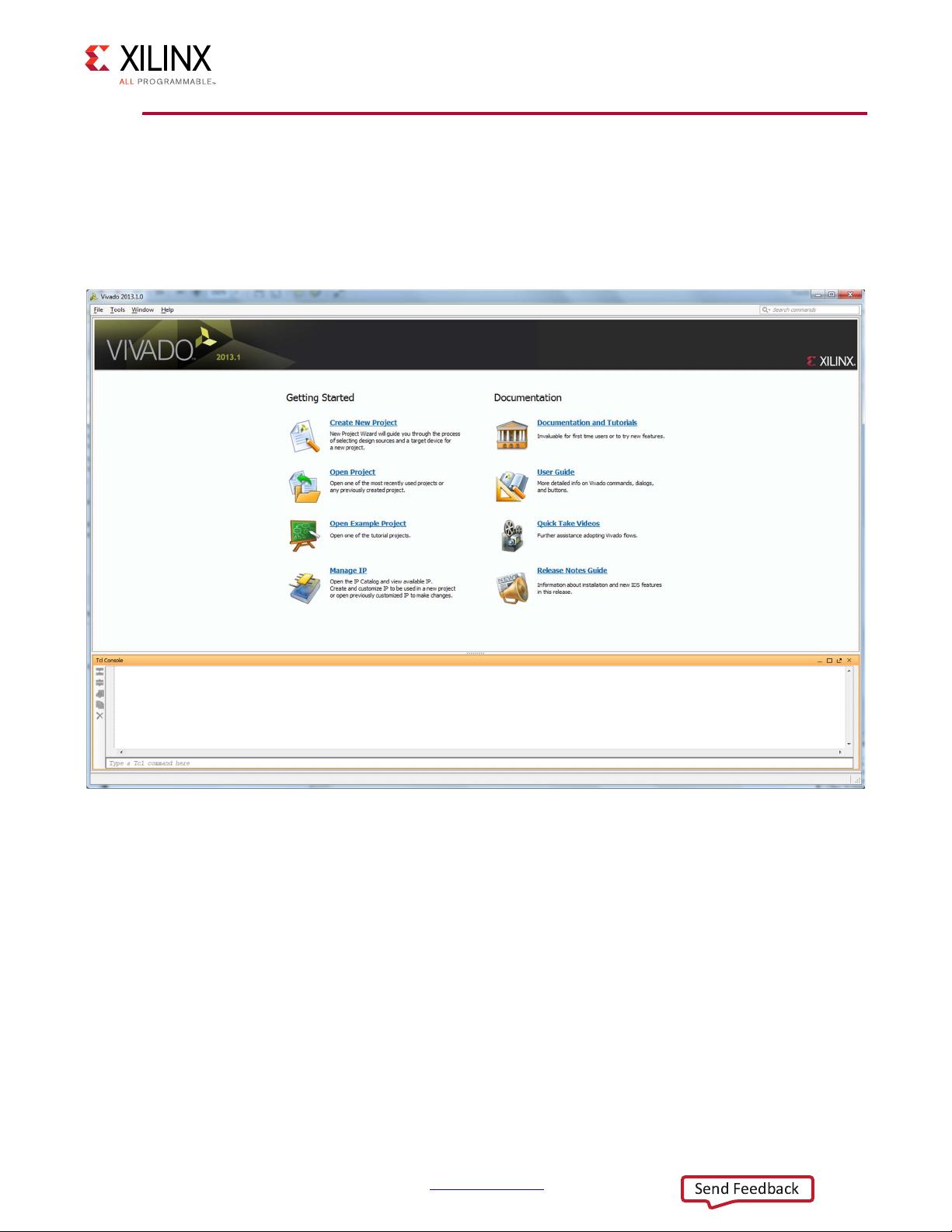

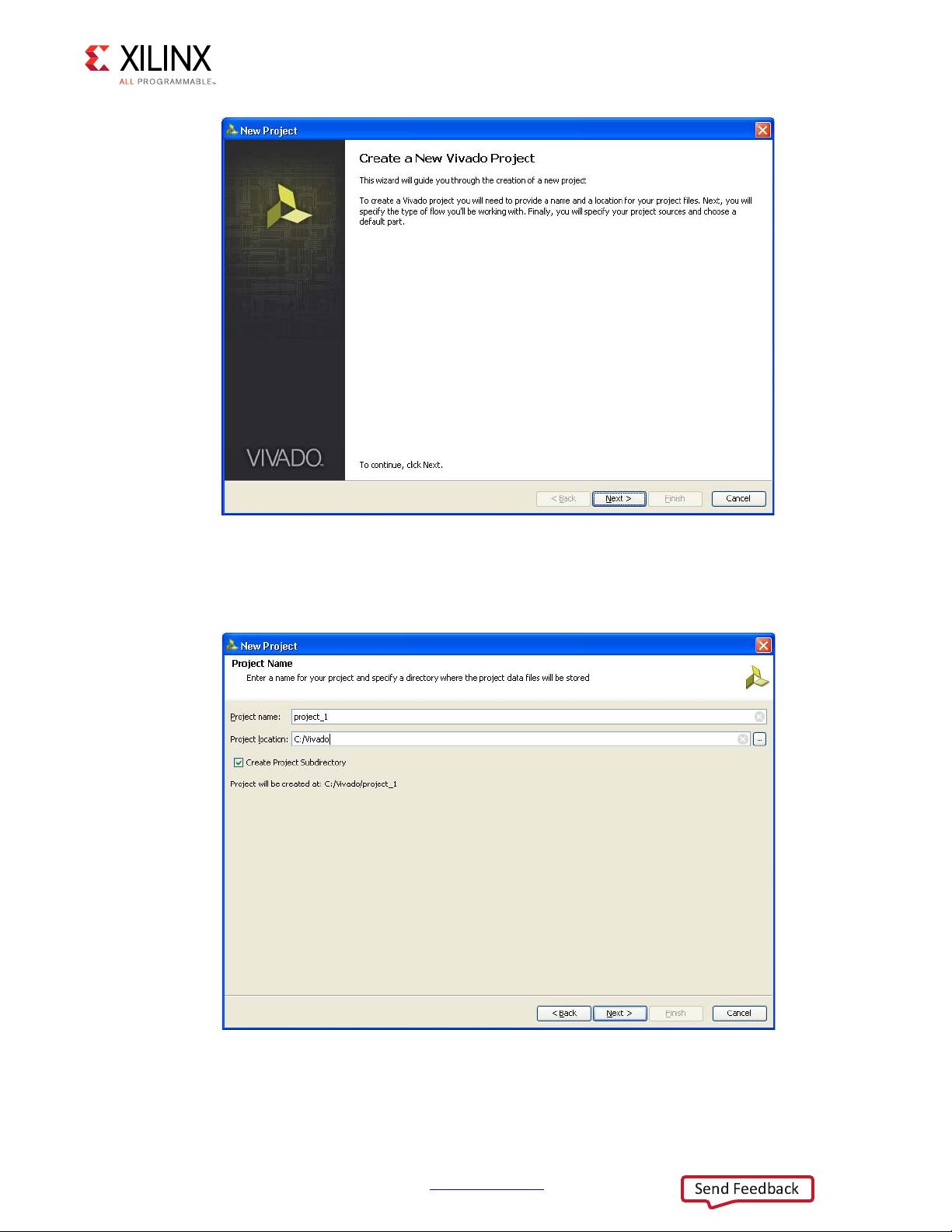

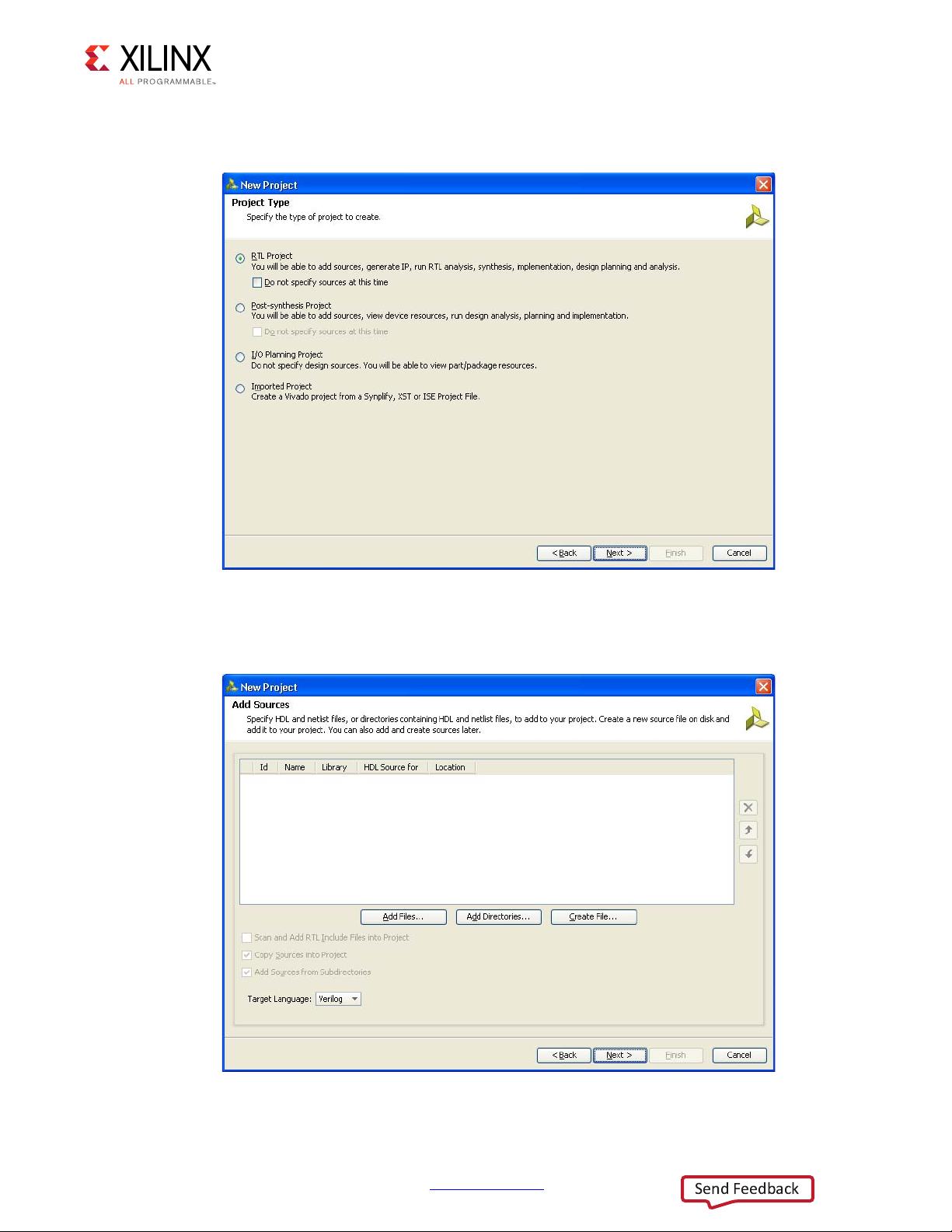

"DDR3指导文档,涉及Zynq-7000 AP SoC和7系列设备的内存接口解决方案,使用Vivado和ModelSim进行仿真测试,通过Xilinx的IP核实现,用户接口模块自定义。"

在DDR3内存接口设计中,Zynq-7000 AP SoC和7系列FPGA提供了先进的内存接口解决方案,以满足高速数据传输的需求。文档版本为v2.3,包含了重要的更新和改进,如VCS和IES的仿真流程,以及QDRII+、RLDRAM II/RLDRAM 3和LPDDR2章节的时钟部分。

对于DDR3的读写程序,设计者需要理解其内存参数设置,如在Chapter 1中新增的DDR3内存参数选项设置描述。控制器选项部分也进行了更新,特别是在Answer Record 54025中添加了注释,这对于正确配置DDR3控制器至关重要。此外,用户接口中的app_rd_data_end参数有了新的描述,这是控制读取数据流的关键信号。

在AXI4从属接口参数方面,Table 1-19有所更新,详细列出了接口信号的参数,这有助于理解FPGA如何与DDR3内存进行通信。文档还增强了对时间分复用(TDM)、轮询(Round-Robin)和读取优先级(RD_PRI_REG)的描述,这些都是优化内存访问效率的重要机制。

在时钟架构部分,文档更新了Fig.1-50,详细阐述了DDR3内存系统的时钟方案,包括时钟的生成和同步,这对于确保数据的准确传输至关重要。同时,校准时间(Calibration Times)章节中,全局误差校正(GES)的描述也得到了更新,这对于保证内存系统在不同条件下的稳定运行起到了关键作用。

最后,文档还涵盖了地址/控制信号和SSIdescriptions,这是在Pinout Requirements部分新增的内容,有助于设计者正确布局和连接DDR3内存。输入时钟指南也进行了更新,确保了与各种内存类型的兼容性和性能优化。

这个DDR3指导文档提供了一套完整的内存接口设计流程,包括仿真测试、硬件平台测试以及关键参数的配置,对于使用Xilinx IP核并自定义用户接口模块的设计者来说,是宝贵的参考资料。通过深入理解和应用文档中的知识,可以有效地实现和验证DDR3内存系统在Zynq-7000 AP SoC和7系列FPGA上的功能。

217 浏览量

167 浏览量

点击了解资源详情

138 浏览量

182 浏览量

1715 浏览量

153 浏览量

153 浏览量

156 浏览量

qq_16797773

- 粉丝: 0

- 资源: 3