Verilog实现数据比较器:组合逻辑与测试

需积分: 9 72 浏览量

更新于2024-07-23

收藏 274KB PDF 举报

在这个资源中,主要讨论了如何使用Verilog HDL语言设计和实现基础的数字逻辑电路,特别是组合逻辑电路和时序逻辑电路。组合逻辑电路部分介绍了一个数据比较器的设计,通过assign语句实现了简单的逻辑判断,即当输入数据a与b相等时,输出结果为1,否则为0。该电路的关键部分是`equal=(a==b)?1:0`,这是一种在Verilog中常见的用法,用于实现条件分支。

设计的模块名为compare.v,它有三个端口:输入a和b,以及输出equal。测试模块comparetest通过设置不同的输入值(例如,先将a和b都设为0,然后改变其中一个为1),观察equal的输出,验证设计的正确性。同时,还要求扩展测试,设计一个8位字节比较器,根据字节大小关系输出高低电平,以确保全面测试电路的功能。

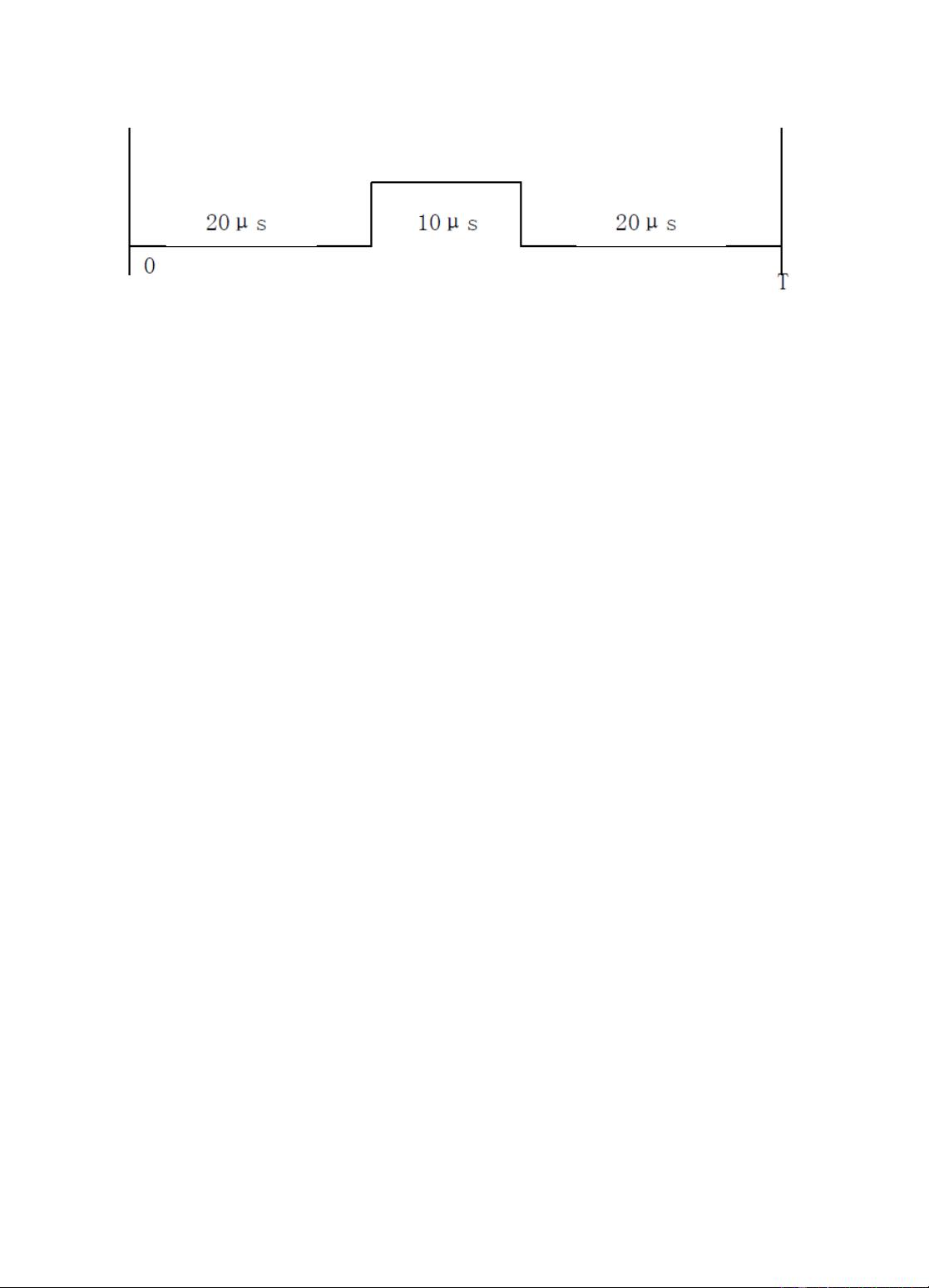

时序逻辑电路部分讲述了在Verilog中,对于依赖于时钟事件的逻辑,如计数器、触发器等,会使用always块结合posedge clk(上升沿)或negedge clk(下降沿)来描述。这与组合逻辑电路的区别在于,时序逻辑电路的时间行为更为复杂,且其行为会根据时钟信号的变化而变化。

总结来说,这个资源提供了使用Verilog HDL进行基础逻辑电路设计的实际例子,包括组合逻辑电路中的数据比较器设计,以及时序逻辑电路的概念和基本表述方法。这对于理解并实践Verilog语言进行硬件描述语言设计至关重要。通过这个过程,学习者能够掌握如何构建和测试复杂的逻辑电路,提升数字逻辑设计的技能。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-09-24 上传

2016-05-31 上传

2010-01-26 上传

2008-05-02 上传

2018-06-02 上传

sinat_15456963

- 粉丝: 0

- 资源: 1

最新资源

- upptime-test:Kar Karan Kale的正常运行时间监控器和状态页面,由@upptime提供支持

- Practica:数据清洗与分析

- 渣浆泵过流部件的生产实践.rar

- Newsletter-Signup-Web-App:在Node中使用MailChimp API服务制作的Newsletter注册Web应用程序

- 使用SpringBoot + SpringCloudAlibaba(正在重构中)搭建的金融类微服务项目-万信金融. .zip

- 西安交大电力系统分析视频教程第27讲

- MDIN3xx_mainAPI_v0.2_26Aug2011.zip

- hibernate,java项目源码,java中如何查看方法的

- 七段图像创建:非常灵活的功能,您可以创建任意大小的七段图像。-matlab开发

- cv

- OnePortMeas:适用于一端口RF设备表征的Python App

- java,java源码网站,javaunsafe

- 网址状态

- 网络时间同步工具 NetTime 3.20 Alpha 3.zip

- css-grid-course

- Python库 | clay-3.2.tar.gz