1

1

2

2

3

3

4

4

5

5

6

6

D D

C C

B B

A A

Avnet Engineering Services

Title:

Size: Rev:

C

Document Number:

Date:

Sheet of

10/29/2013 3 11

F

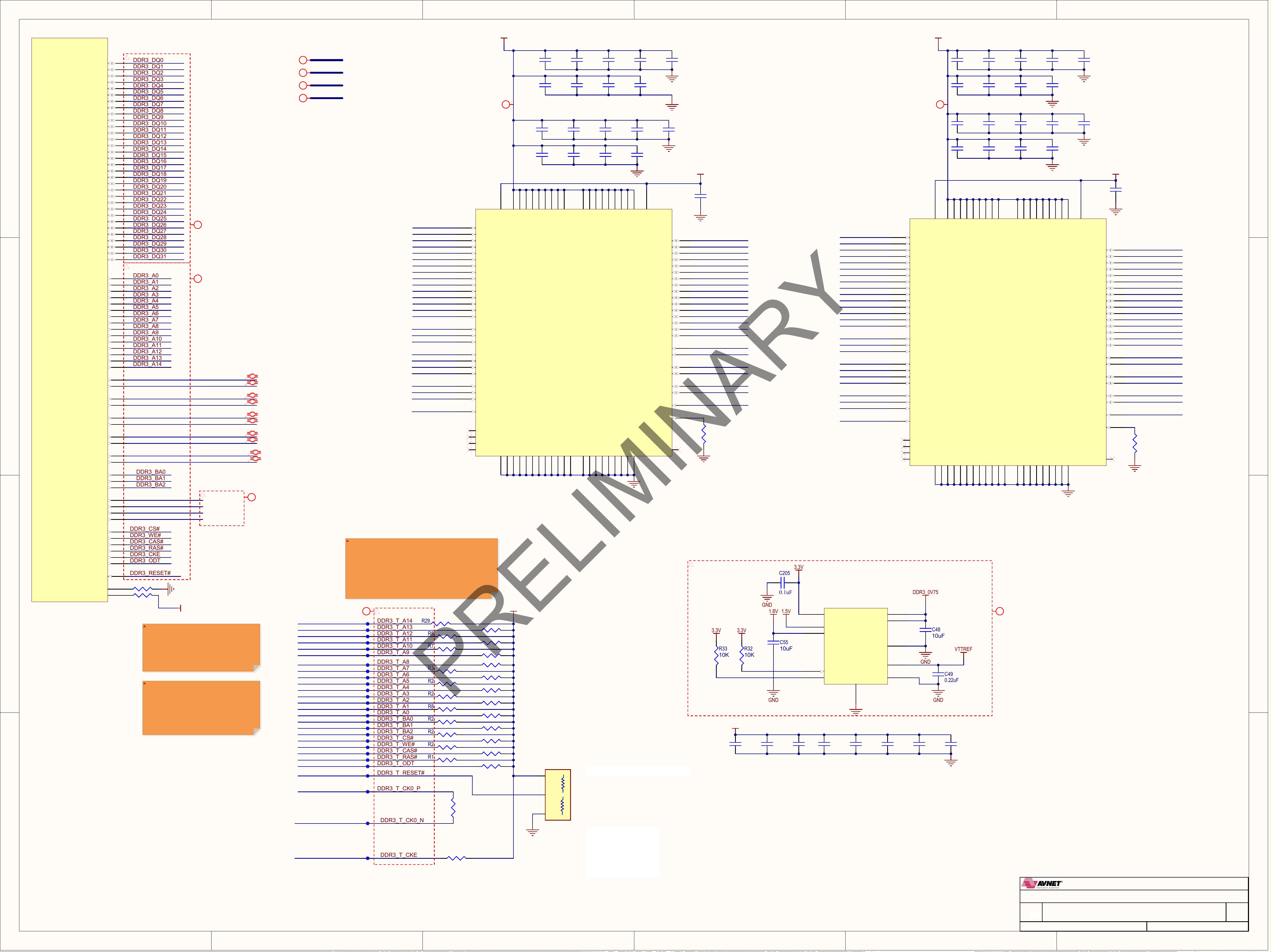

03 - DDR3.SchDoc

VDDQ

A1

DQ13

A2

DQ15

A3

DQ12

A7

VDDQ

A8

VSS

A9

VSSQ

B1

VDD

B2

VSS

B3

UDQS#

B7

DQ14

B8

VSSQ

B9

VDDQ

C1

DQ11

C2

DQ9

C3

UDQS

C7

DQ10

C8

VDDQ

C9

VSSQ

D1

VDDQ

D2

UDM

D3

DQ8

D7

VSSQ

D8

VDD

D9

VSS

E1

VSSQ

E2

DQ0

E3

LDM

E7

VSSQ

E8

VDDQ

E9

VDDQ

F1

DQ2

F2

LDQS

F3

DQ1

F7

DQ3

F8

VSSQ

F9

VSSQ

G1

DQ6

G2

LDQS#

G3

VDD

G7

VSS

G8

VSSQ

G9

VrefDQ

H1

VDDQ

H2

DQ4

H3

DQ7

H7

DQ5

H8

VDDQ

H9

n/c

J1

VSS

J2

RAS#

J3

CK

J7

VSS

J8

n/c

J9

ODT

K1

VDD

K2

CAS#

K3

CK#

K7

VDD

K8

CKE

K9

n/c

L1

CS#

L2

WE#

L3

A10/AP

L7

ZQ

L8

n/c

L9

VSS

M1

BA0

M2

BA2

M3

n/c

M7

VrefCA

M8

VSS

M9

VDD

N1

A3

N2

A0

N3

A12/BC#

N7

BA1

N8

VDD

N9

VSS

P1

A5

P2

A2

P3

A1

P7

A4

P8

VSS

P9

VDD

R1

A7

R2

A9

R3

A11

R7

A6

R8

VDD

R9

VSS

T1

RESET#

T2

A13

T3

A14

T7

A8

T8

VSS

T9

U12

MT41K256M16HA-125:E

VDDQ

A1

DQ13

A2

DQ15

A3

DQ12

A7

VDDQ

A8

VSS

A9

VSSQ

B1

VDD

B2

VSS

B3

UDQS#

B7

DQ14

B8

VSSQ

B9

VDDQ

C1

DQ11

C2

DQ9

C3

UDQS

C7

DQ10

C8

VDDQ

C9

VSSQ

D1

VDDQ

D2

UDM

D3

DQ8

D7

VSSQ

D8

VDD

D9

VSS

E1

VSSQ

E2

DQ0

E3

LDM

E7

VSSQ

E8

VDDQ

E9

VDDQ

F1

DQ2

F2

LDQS

F3

DQ1

F7

DQ3

F8

VSSQ

F9

VSSQ

G1

DQ6

G2

LDQS#

G3

VDD

G7

VSS

G8

VSSQ

G9

VrefDQ

H1

VDDQ

H2

DQ4

H3

DQ7

H7

DQ5

H8

VDDQ

H9

n/c

J1

VSS

J2

RAS#

J3

CK

J7

VSS

J8

n/c

J9

ODT

K1

VDD

K2

CAS#

K3

CK#

K7

VDD

K8

CKE

K9

n/c

L1

CS#

L2

WE#

L3

A10/AP

L7

ZQ

L8

n/c

L9

VSS

M1

BA0

M2

BA2

M3

n/c

M7

VrefCA

M8

VSS

M9

VDD

N1

A3

N2

A0

N3

A12/BC#

N7

BA1

N8

VDD

N9

VSS

P1

A5

P2

A2

P3

A1

P7

A4

P8

VSS

P9

VDD

R1

A7

R2

A9

R3

A11

R7

A6

R8

VDD

R9

VSS

T1

RESET#

T2

A13

T3

A14

T7

A8

T8

VSS

T9

U11

MT41K256M16HA-125:E

4.7uF

C39

4.7uF

C45

GND

DDR3_0V75

1.5V

10uF

C55

GND

DDR3_0V75

VTTREF

DDR3 Termination Supply

GND

240

R85

GND

240

R79

NOTE:

RESET# requires 40.2

resistor for PD, to maintain

logic high through FPGA

Configuration. See

UG933p62

DDR3_T_CK0_N

DDR3_T_CK0_P

40.2R80

40.2R84

40.2R78

40.2R24

40.2R31

40.2R30

40.2R86

40.2R28

40.2R83

40.2R26

40.2R23

40.2R82

40.2R21

40.2R25

40.2R81

40.2R22

40.2R18

40.2R20

40.2R19

40.2R17

DDR3_0V75

40.2R27

40.2R29

GND

47uF

C42

GND

GND

GND

VTTREF

47uF

C41

GND

GND

GND

1.5V

VTTREF

DDR3_DQ0

DDR3_DQ1

DDR3_DQ2

DDR3_DQ3

DDR3_DQ4

DDR3_DQ5

DDR3_DQ6

DDR3_DQ7

DDR3_DQ8

DDR3_DQ9

DDR3_DQ10

DDR3_DQ11

DDR3_DQ12

DDR3_DQ13

DDR3_DQ14

DDR3_DQ15

DDR3_DM1

DDR3_DM0

DDR3_DQS1_P

DDR3_DQS0_P

DDR3_DQS0_N

DDR3_DQS1_N

DDR3_ODT

DDR3_BA0

DDR3_BA1

DDR3_BA2

DDR3_CS#

DDR3_WE#

DDR3_CAS#

DDR3_RAS#

DDR3_CKE

DDR3_CK0_N

DDR3_RESET#

DDR3_CK0_P

GND

DDR3_ODT

DDR3_DQ0

DDR3_DQ1

DDR3_DQ2

DDR3_DQ3

DDR3_DQ4

DDR3_DQ5

DDR3_DQ6

DDR3_DQ7

DDR3_DQ8

DDR3_DQ9

DDR3_DQ10

DDR3_DQ11

DDR3_DQ12

DDR3_DQ13

DDR3_DQ14

DDR3_DQ15

DDR3_DQS1_P

DDR3_DQS0_P

DDR3_DQS0_N

DDR3_DQS1_N

DDR3_ODT

DDR3_DQ16

DDR3_DQ17

DDR3_DQ18

DDR3_DQ19

DDR3_DQ20

DDR3_DQ21

DDR3_DQ22

DDR3_DQ23

DDR3_DQ24

DDR3_DQ25

DDR3_DQ26

DDR3_DQ27

DDR3_DQ28

DDR3_DQ29

DDR3_DQ30

DDR3_DQ31

DDR3_DQ16

DDR3_DQ17

DDR3_DQ18

DDR3_DQ19

DDR3_DQ20

DDR3_DQ21

DDR3_DQ22

DDR3_DQ23

DDR3_DQ24

DDR3_DQ25

DDR3_DQ26

DDR3_DQ27

DDR3_DQ28

DDR3_DQ29

DDR3_DQ30

DDR3_DQ31

DDR3_DM3

DDR3_DM2

DDR3_DQS3_P

DDR3_DQS2_P

DDR3_DQS2_N

DDR3_DQS3_N

DDR3_DQS3_P

DDR3_DQS2_P

DDR3_DQS2_N

DDR3_DQS3_N

DDR3_RESET#

DDR3_CS#

DDR3_WE#

DDR3_CAS#

DDR3_RAS#

DDR3_CKE

DDR3_CK0_N

DDR3_CK0_P

DDR3_BA0

DDR3_BA1

DDR3_BA2

DDR3_A0

DDR3_A1

DDR3_A2

DDR3_A3

DDR3_A4

DDR3_A5

DDR3_A6

DDR3_A7

DDR3_A8

DDR3_A9

DDR3_A10

DDR3_A11

DDR3_A12

DDR3_A13

DDR3_A14

80.6

R74

1.5V

80.6R75

80.6

R77

47uF

C43

GND

GND

1.5V

47uF

C44

GND

GND

DDR3_T_A0

DDR3_T_A1

DDR3_T_A2

DDR3_T_A3

DDR3_T_A4

DDR3_T_A5

DDR3_T_A6

DDR3_T_A7

DDR3_T_A8

DDR3_T_A9

DDR3_T_A10

DDR3_T_A11

DDR3_T_A12

DDR3_T_A13

DDR3_T_A14

DDR3_A0

DDR3_A1

DDR3_A2

DDR3_A3

DDR3_A4

DDR3_A5

DDR3_A6

DDR3_A7

DDR3_A8

DDR3_A9

DDR3_A10

DDR3_A11

DDR3_A12

DDR3_A13

DDR3_A14

DDR3_A0

DDR3_A1

DDR3_A2

DDR3_A3

DDR3_A4

DDR3_A5

DDR3_A6

DDR3_A7

DDR3_A8

DDR3_A9

DDR3_A10

DDR3_A11

DDR3_A12

DDR3_A13

DDR3_A14

DDR3_BA0

DDR3_BA1

DDR3_BA2

DDR3_CS#

DDR3_WE#

DDR3_CAS#

DDR3_RAS#

DDR3_CKE

DDR3_CK0_N

DDR3_CK0_P

DDR3_RESET#

DDR3_T_RESET#

DDR3_T_CKE

DDR3_T_ODT

DDR3_T_BA0

DDR3_T_BA1

DDR3_T_BA2

DDR3_T_CS#

DDR3_T_WE#

DDR3_T_CAS#

DDR3_T_RAS#

40.2R15

GND

i DDR_AC

i DDR_D

DDR3_DQ[7..0]

DDR3_DQ[15..8]

DDR3_DQ[23..16]

DDR3_DQ[31..24]

iDDR_D_BL0

iDDR_D_BL1

iDDR_D_BL2

iDDR_D_BL3

i DDR_DM

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1DDR3_A14

DDR3_A13

DDR3_A12

DDR3_A11

DDR3_A10

DDR3_A9

DDR3_A8

DDR3_A7

DDR3_A6

DDR3_A5

DDR3_A4

DDR3_A3

DDR3_A2

DDR3_A1

DDR3_A0

DDR3_BA0

DDR3_BA1

DDR3_BA2

DDR3_CS#

DDR3_WE#

DDR3_CAS#

DDR3_RAS#

DDR3_ODT

DDR3_RESET#

DDR3_CK0_P

DDR3_CK0_N

DDR3_CKE

1

iDDR_PWRiDDR_PWR

iDDR_T

DDR3_DM1

DDR3_DM0

DDR3_DM3

DDR3_DM2

3.3V

GND

1.8V

10K

R32

10K

R33

3.3V 3.3V

10uF

C48

GND

0.22uF

C49

GND

GND

PS_DDR_DRST_B_502

B4

PS_DDR_DQ0_502

C3

PS_DDR_DQ1_502

B3

PS_DDR_DQ2_502

A2

PS_DDR_DQ3_502

A4

PS_DDR_DM0_502

A1

PS_DDR_DQS_P0_502

C2

PS_DDR_DQS_N0_502

B2

PS_DDR_DQ4_502

D3

PS_DDR_DQ5_502

D1

PS_DDR_DQ6_502

C1

PS_DDR_DQ7_502

E1

PS_DDR_DQ8_502

E2

PS_DDR_DQ9_502

E3

PS_DDR_DQ10_502

G3

PS_DDR_DQ11_502

H3

PS_DDR_DM1_502

F1

PS_DDR_DQS_P1_502

G2

PS_DDR_DQS_N1_502

F2

PS_DDR_DQ12_502

J3

PS_DDR_DQ13_502

H2

PS_DDR_DQ14_502

H1

PS_DDR_DQ15_502

J1

PS_DDR_A14_502

F4

PS_DDR_A13_502

D4

PS_DDR_A12_502

E4

PS_DDR_A11_502

G4

PS_DDR_A10_502

F5

PS_DDR_A9_502

J4

PS_DDR_A8_502

K1

PS_DDR_A7_502

K4

PS_DDR_A6_502

L4

PS_DDR_A5_502

L1

PS_DDR_A4_502

M4

PS_DDR_A3_502

K3

PS_DDR_VRN_502

G5

PS_DDR_VRP_502

H5

PS_DDR_CKP_502

L2

PS_DDR_CKN_502

M2

PS_DDR_A2_502

M3

PS_DDR_A1_502

K2

PS_DDR_A0_502

N2

PS_DDR_BA2_502

J5

PS_DDR_BA1_502

R4

PS_DDR_BA0_502

L5

PS_DDR_ODT_502

N5

PS_DDR_CS_B_502

N1

PS_DDR_CKE_502

N3

PS_DDR_WE_B_502

M5

PS_DDR_CAS_B_502

P5

PS_DDR_RAS_B_502

P4

PS_DDR_DQ16_502

P1

PS_DDR_DQ17_502

P3

PS_DDR_DQ18_502

R3

PS_DDR_DQ19_502

R1

PS_DDR_DM2_502

T1

PS_DDR_DQS_P2_502

R2

PS_DDR_DQS_N2_502

T2

PS_DDR_DQ20_502

T4

PS_DDR_DQ21_502

U4

PS_DDR_DQ22_502

U2

PS_DDR_DQ23_502

U3

PS_DDR_DQ24_502

V1

PS_DDR_DQ25_502

Y3

PS_DDR_DQ26_502

W1

PS_DDR_DQ27_502

Y4

PS_DDR_DM3_502

Y1

PS_DDR_DQ30_502

V2

PS_DDR_DQ28_502

Y2

PS_DDR_DQS_N3_502

W4

PS_DDR_DQ31_502

V3

PS_DDR_DQ29_502

W3

PS_DDR_DQS_P3_502

W5

BANK 502

U9G

Zynq 7010/7020 SOC CLG400

40.2R16

0.01uF

C193

0.1uF

C190

0.1uF

C202

MicroZed 7010

B

3

Com

2

A

1

Jumper

40.2

JT6

GND

Default: Pins 1 - 2, 40.2 ohm resistor.

i DDR_PWR

0.1uF

C170

0.1uF

C179

0.1uF

C189

0.1uF

C169

0.1uF

C201

0.1uF

C182

0.1uF

C177

0.1uF

C176

0.1uF

C181

0.1uF

C188

0.1uF

C199

0.1uF

C194

0.1uF

C186

0.1uF

C184

0.01uF

C196

0.01uF

C200

0.01uF

C203

0.01uF

C180

0.01uF

C178

0.01uF

C172

0.01uF

C174

0.01uF

C173

0.01uF

C175

0.01uF

C171

0.01uF

C183

0.01uF

C197

0.01uF

C192

0.01uF

C198

0.01uF

C191

0.01uF

C195

0.01uF

C187

0.1uF

C185

0.01uF

C37

0.1uF

C204

0.01uF

C38

0.1uF

C205

100uF

C47

100uF

C46

VDDQSNS

1

VLDOIN

2

VTT

3

PGND

4

VTTSNS

5

VTTREF

6

S3

7

GND

8

S5

9

VDD

10

PAD

U13

TPS51206

Layout Note:

Use Fly-by routing and termination for DDR3

control signals.

Resistors should be placed past the last

memory IC & as close to the device as

possible.

Layout Note:

DDR3 target trace impedances are

as follows:

Single Ended Signals = 40 ohms

Differential Signals = 80 ohms

Layout Note:

DDR3 trace lengths must include

Zynq package flight times.

See UG933 and Layout

Guidelines.