MAX+PLUSⅡ开发软件:宏模块详解与应用实例

需积分: 9 187 浏览量

更新于2024-08-02

收藏 10.42MB PPT 举报

MAX+PLUSⅡ开发软件是一款广泛应用于硬件描述语言(HDL)设计的工具,特别是针对数字逻辑电路的设计和仿真。其中,宏模块(Macro Modules)是其强大的功能之一,它们是预先编写的可重用代码块,能够简化设计过程并提高效率。在第七章中,我们深入探讨了MAX+PLUSⅡ开发软件中的宏模块及其具体应用。

本章节主要关注以下几个方面:

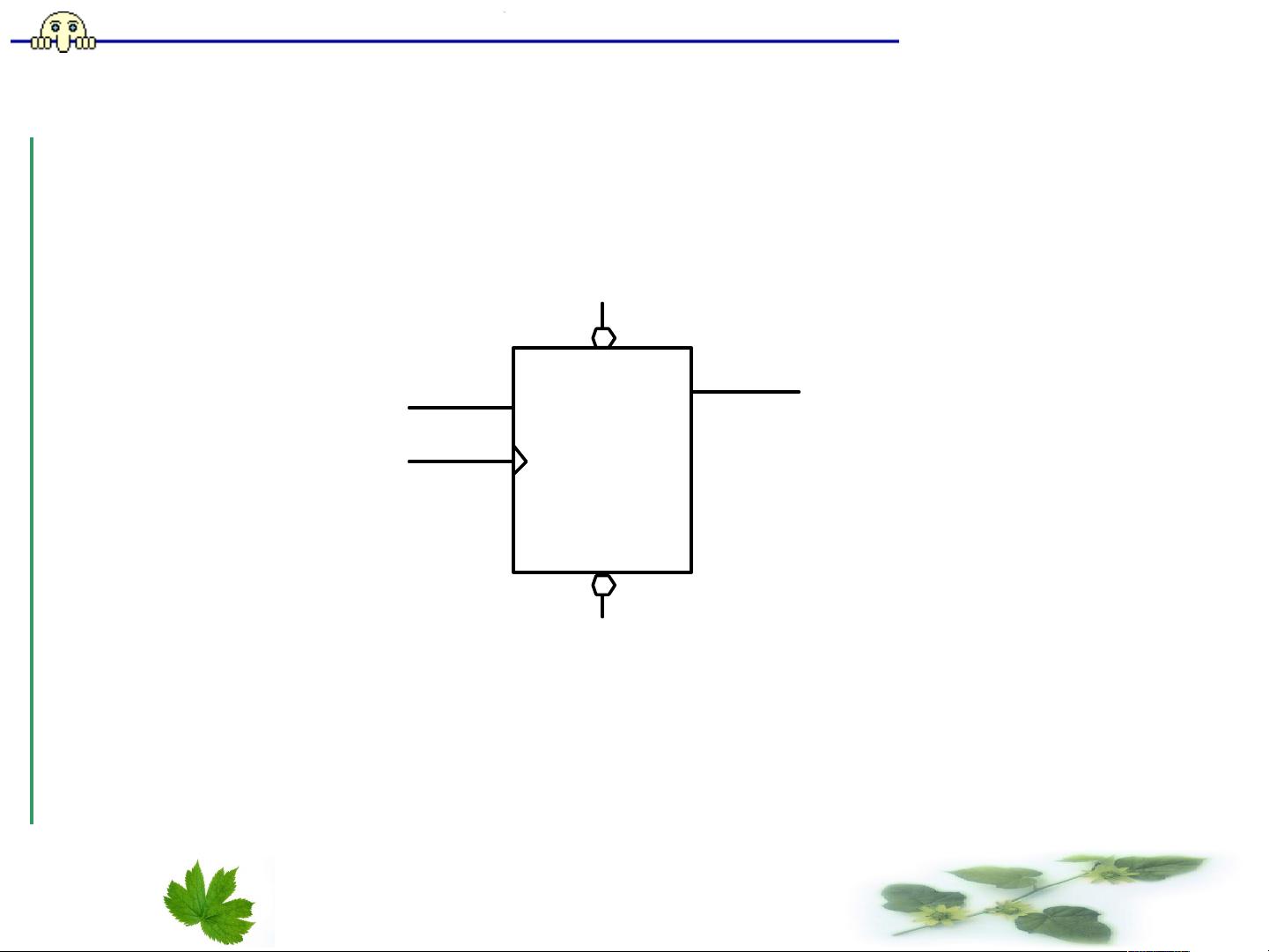

1. **时序电路宏模块**:这部分介绍了基础的数字逻辑组件,如触发器,它是构建复杂时序电路的基础。常见的触发器类型有D触发器、T触发器、JK触发器以及扩展型触发器,如带使能端和控制端的模型。MAX+PLUSⅡ提供了多种预定义的触发器宏模块,如Lpm_H、Lpm_dff、Lpm_t等,用户可以根据需要选择和定制。

2. **运算电路宏模块**:尽管这部分没有在提供的内容中详细列出,但我们可以推测这部分可能涉及基本的算术和逻辑运算电路的宏模块,如门电路、加法器、比较器等,这些都是设计数字电路时必不可少的组成部分。

3. **存储器宏模块**:包括寄存器和计数器等,如Lpm_dff中的移位寄存器,以及74系列芯片中用于不同功能的多路复用器、双JK触发器等,这些都是实现数据存储和处理的关键模块。

表格7.1列举了部分触发器宏模块,涵盖了各种类型的触发器,如带有预置、清零、异步输入等控制信号的JK触发器和D触发器,还有专门针对特定功能设计的多路复用器和多位寄存器。使用这些宏模块,设计师可以直接调用,减少了重复编码的工作量,提高了设计的准确性和一致性。

通过MAX+PLUSⅡ的宏模块,设计师可以快速构建复杂的数字电路,并在软件环境中进行仿真和验证。掌握和熟练运用这些宏模块,对于提高设计效率和减少错误至关重要。此外,熟悉各个宏模块的功能特性和使用方法,有助于开发者更好地理解和优化他们的电路设计。因此,学习和实践MAX+PLUSⅡ的宏模块是任何从事VHDL或Verilog设计人员必备的技能。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-01-19 上传

2020-12-05 上传

2021-09-21 上传

2021-01-19 上传

2020-12-04 上传

2020-10-20 上传