FPGA实现分频器设计:VHDL代码与原理

需积分: 9 196 浏览量

更新于2024-07-31

收藏 507KB PDF 举报

"使用FPGA实现分频器的设计,通过VHDL进行描述,涵盖了偶数、奇数、半整数、小数、分数和积分分频器的实现方法,适用于SynplifyPro和FPGA厂商的综合器,并在ModelSim上验证。"

在FPGA设计中,分频器是一种常见且重要的电路,它能够将输入时钟频率降低到所需的比例。本文主要探讨了如何使用VHDL这一硬件描述语言在FPGA上实现各种类型的分频器。VHDL是一种强大的工具,允许设计者创建复杂的数字系统,而无需关心具体的物理实现细节。

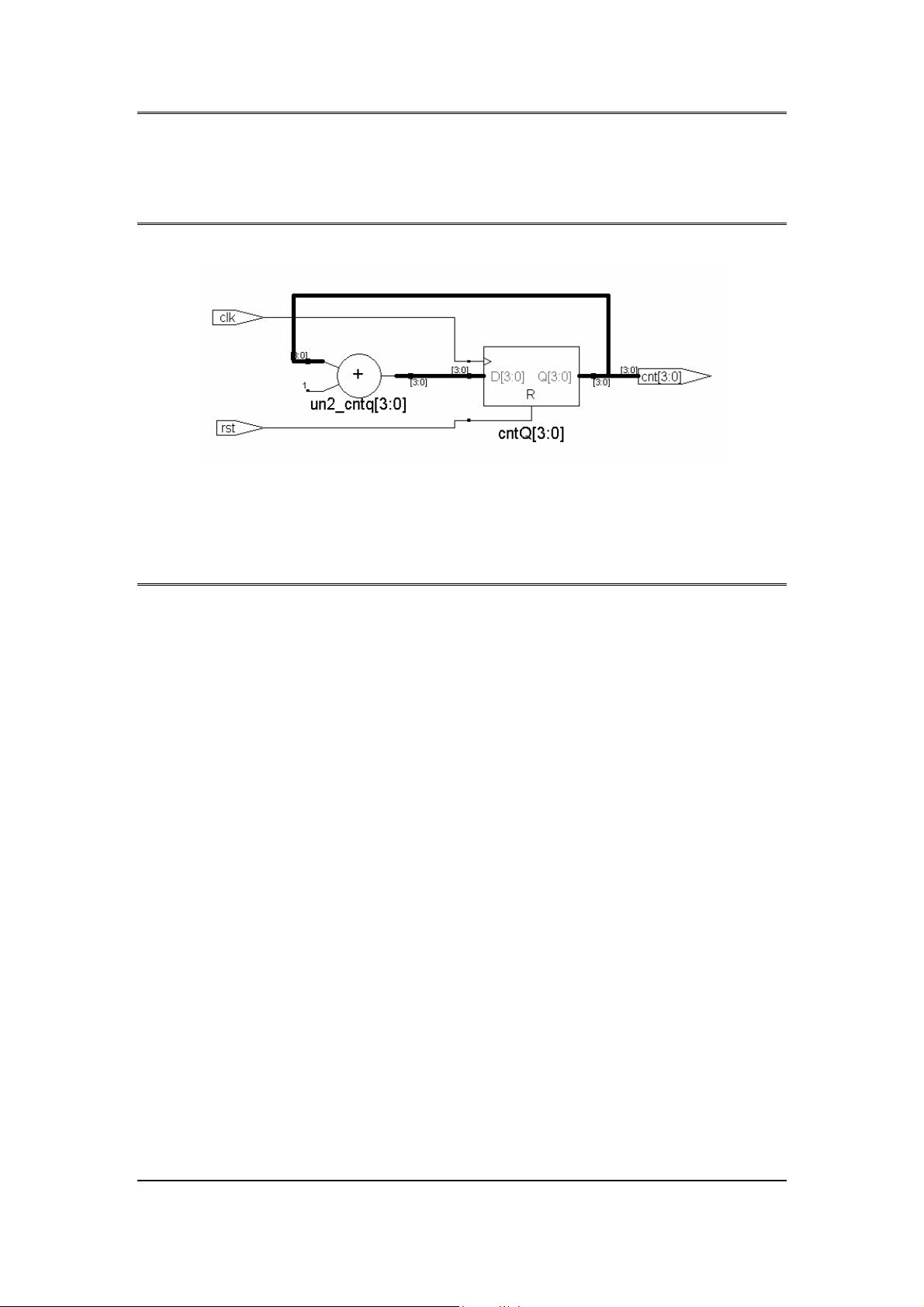

首先,文章介绍了计数器作为实现分频器的基础。计数器分为普通计数器和约翰逊计数器。普通计数器是最基础的加法或减法计数器,例如一个简单的带复位功能的加法计数器可以用VHDL表示,并通过SynplifyPro工具进行综合,生成RTL视图以理解其逻辑结构。

接着,文章深入讨论了不同类型的分频器设计:

1. 偶数分频器:这类分频器将输入时钟频率降低为输入频率的整数倍,且输出脉冲的占空比通常为50%。

2. 奇数分频器:对于奇数分频,输出脉冲的数量会少于输入脉冲,且占空比可能不是50%。设计时需要考虑如何处理最后一个脉冲,以保持正确的时序。

3. 半整数分频器:这种分频器输出脉冲的周期为输入周期的一半,但每个周期只有一个脉冲,占空比为0%或100%。

4. 小数分频器:小数分频涉及到非整数比例的频率降低,这通常通过累加器或累减器实现,以在连续多个周期内积累误差来达到所需的平均频率。

5. 分数分频器:分数分频器允许更灵活的分频比例,可以是任何有理数,通过组合整数和小数部分实现。

6. 积分分频器:积分分频器是基于累加过程的,通过连续的整数分频和小数分频组合,以实现任意精确的分频比。

所有这些分频器设计都可以使用SynplifyPro或FPGA制造商的综合器(如ALTERA的PLL或Xilinx的DLL)综合成实际电路,并在ModelSim这样的仿真环境中进行功能验证,确保设计的正确性。

使用VHDL在FPGA上实现分频器设计提供了一种灵活且成本效益高的方法,能够满足多种时钟管理和信号处理的需求。通过理解和掌握这些设计原理与技巧,设计者可以有效地构建复杂且高效的数字系统。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-05-06 上传

2018-04-13 上传

2022-04-22 上传

2023-12-26 上传

点击了解资源详情

点击了解资源详情

howord_li

- 粉丝: 0

- 资源: 21

最新资源

- Smoker-Generator:给我照片,我帮你抽烟!

- 三菱包装-mt 高级运动_PLC_q173_三菱_包装机_运动

- Research-report-Classification-system:爬取东方财富的宏观研究的研报,基于LSTM进行情感分析,分类为正向,负向和中性三类

- Sichem:C到C#代码转换器

- 毕业设计&课设--大学毕业设计-校园小助手.zip

- gulp-starter:gulp-starter 项目

- 毕业设计&课设--仿知乎社区问答类App,吉林大学计算机科学与技术学院毕业设计.zip

- oceanhonki

- Excel模板客户登记表格式.zip

- yii2-system-info:有关服务器的信息

- notence:not受notion.so(Alpha:pushpin:)启发的开源个人笔记应用程序

- 对数音符

- protonmail-api::envelope:ProtonMail的Node.js API

- incubator_labview_TCP断线重连_tcp通信

- xiuxian:修仙之路 - 小游戏 玩法同2048

- MyAdGuardFilter:我的AdGuard过滤器