FPGA在EDA/PLD中实现SDRAM控制的FIFO设计

PDF格式 | 203KB |

更新于2024-08-31

| 36 浏览量 | 举报

本文主要探讨了在EDA/PLD领域中,如何利用FPGA实现基于FPGA的FIFO设计,以解决在视频实时跟踪应用中数据存储的问题。文中提到,由于DSP内置FIFO的局限性,需要寻找替代方案,而FPGA结合SDRAM成为一种经济高效的解决方案。

在视频实时跟踪系统中,图像数据的高速采集要求大量的存储空间。传统的专用高速FIFO芯片虽然性能优秀,但价格昂贵且容量有限。因此,设计者选择了FPGA作为核心,通过FPGA来控制SDRAM,构建一个大容量、高速的FIFO存储结构。选择SDRAM的原因在于其大容量、低价格以及数据突发传输模式下优异的存取速度,能够满足高带宽数据流的需求。

FPGA中的FIFO设计的关键在于SDRAM的性能限制。首先,SDRAM的最高工作频率决定了数据传输的最高速度。频率越高,数据传输速率也越快。其次,SDRAM的突发长度影响数据吞吐量,突发长度越长,数据传输速率理论上可以提高。以文中举例的MT48LC4M3282 SDRAM为例,它具有128Mb的存储容量,32位数据宽度,并由4个Bank组成,具备良好的扩展性和高速存取能力。

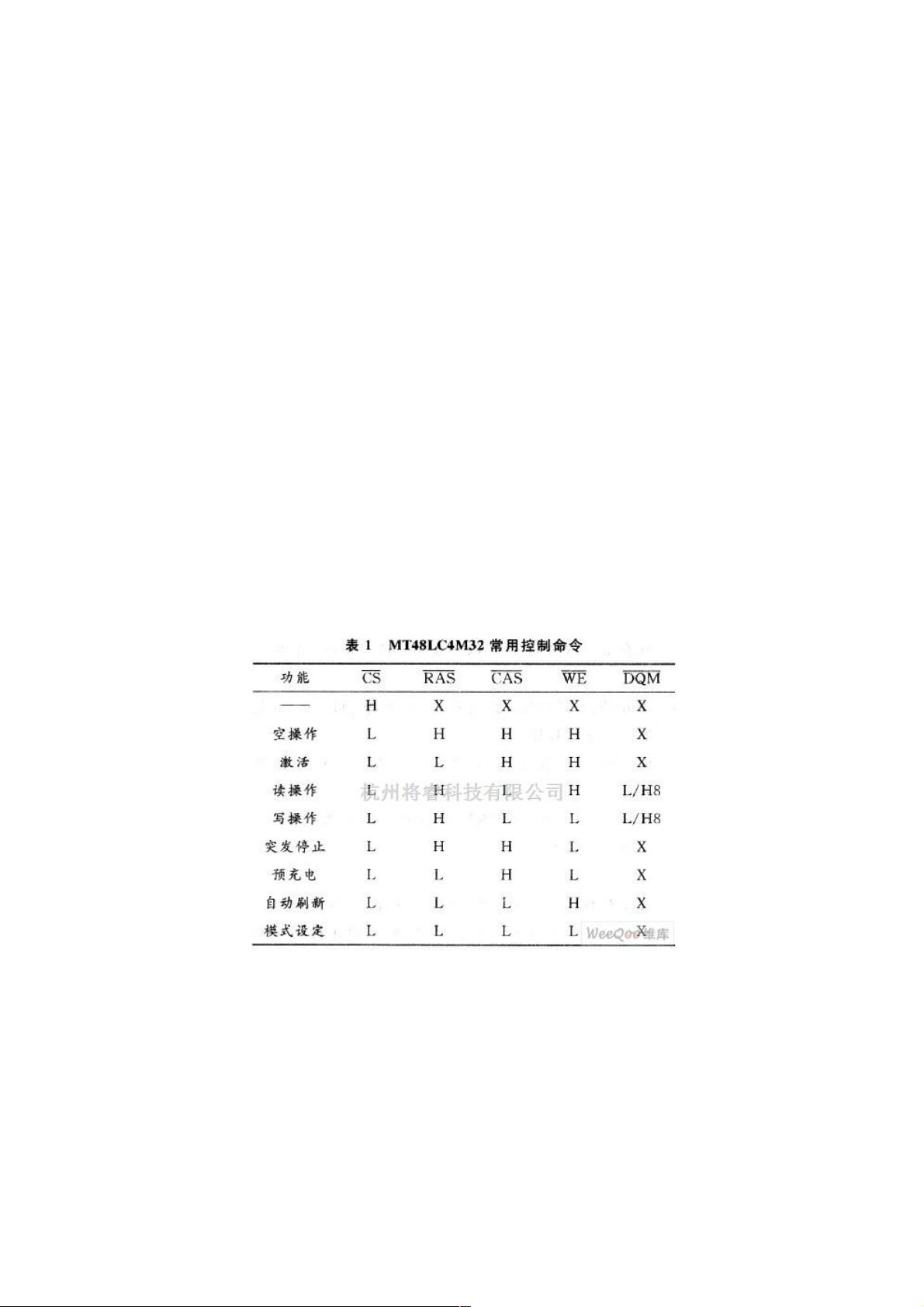

FIFO系统的设计包括FPGA内部的FIFO模块、缓冲器以及SDRAM控制器。FIFO模块负责数据的临时存储和读写管理,缓冲器用于数据的暂存和速率匹配,SDRAM控制器则负责与SDRAM之间的交互,正确执行读写操作,如控制时钟信号(CLK)、时钟使能(CKE)、片选信号(CS)、写使能(WE)、列有效(CAS)、行有效(RAS)等,以及输入输出使能(DQM)。

在实际应用中,FPGA会根据预定义的控制命令与SDRAM进行通信,确保数据的高效、准确传输。这样的设计不仅降低了系统的成本,还提高了系统的灵活性和可扩展性,适用于多种高速数据处理应用场景。

总结来说,基于FPGA的FIFO设计提供了一种经济且高效的解决方案,解决了视频实时跟踪等高带宽应用中的大数据存储问题,通过FPGA对SDRAM的智能控制,实现了高速数据存取,降低了系统成本,提高了系统性能。

相关推荐

weixin_38729399

- 粉丝: 7

最新资源

- 渝海QQ号码吉凶查询工具PHP源码及多样化技术项目资源

- QT串口通信数据完整性解决方案

- DTcms V5.0旗舰版MSSQL源码深度升级与功能增强

- 深入探讨单片机的整机设计与多机通信技术

- VB实现鼠标自动连点技术指南

- DesignToken2Code:Sketch插件将设计标记自动转换为SCSS代码

- 探索Android最佳实践:MVP、RxJava与热修复

- 微软日本发布Win7萌系主题包:5位萌少女主题全体验

- Scratch3.0编程启蒙源代码包:少儿教育与创造力培养

- 实现汉字简繁转换的JavaScript代码教程

- Debian环境下Alacritty终端模拟器的软件包发布

- Mybatis自动生成代码工具:快速实现代码生成

- 基于ASP.NET和SQL的选课系统开发与实现

- 全面掌握Swift开发的权威指南解析

- Java实现的HTTP代理测试工具ProxyTester

- 6至10岁儿童Scratch3.0积木编程源代码下载